1.half adder:

module top_module(

input a, b,

output cout, sum );

assign {cout,sum}=a+b;

endmodule

2.full adder:

module top_module(

input a, b, cin,

output cout, sum );

assign {cout,sum}=a+b+cin;

endmodule

运用全加器模块:

** 3. 3-bit binary ripple-carry adder:**

module top_module(

input [2:0] a, b,

input cin,

output [2:0] cout,

output [2:0] sum );

full u1(a[0],b[0],cin,cout[0],sum[0]);

full u2(a[1],b[1],cout[0],cout[1],sum[1]);

full u3(a[2],b[2],cout[1],cout[2],sum[2]);

endmodule

module full(

input a, b, cin,

output cout, sum );

assign {cout,sum}=a+b+cin;

endmodule

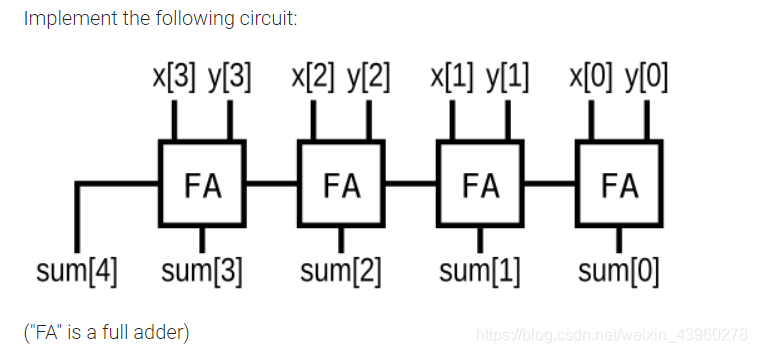

4.电路图如下:

module top_module (

input [3:0] x,

input [3:0] y,

output [4:0] sum);

wire [2:0] cout;

full u1(x[0],y[0],0,cout[0],sum[0]);

full u2(x[1],y[1],cout[0],cout[1],sum[1]);

full u3(x[2],y[2],cout[1],cout[2],sum[2]);

full u4(x[3],y[3],cout[2],sum[4],sum[3]);

endmodule

module full(

input a, b, cin,

output cout, sum );

assign {cout,sum}=a+b+cin;

endmodule

自然也有更加简单的方法,由于不需要知道每一位的cout

module top_module (

input [3:0] x,

input [3:0] y,

output [4:0] sum);

assign sum=x+y;

endmodule

5.计算并判断是否溢出:

module top_module (

input [7:0] a,

input [7:0] b,

output [7:0] s,

output overflow

);

assign s=a+b;

assign overflow=(a[7] ^ ~b[7])&(a[7]^s[7]);

endmodule

详情见HDLbits Arithmetic circuit.

2320

2320

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?