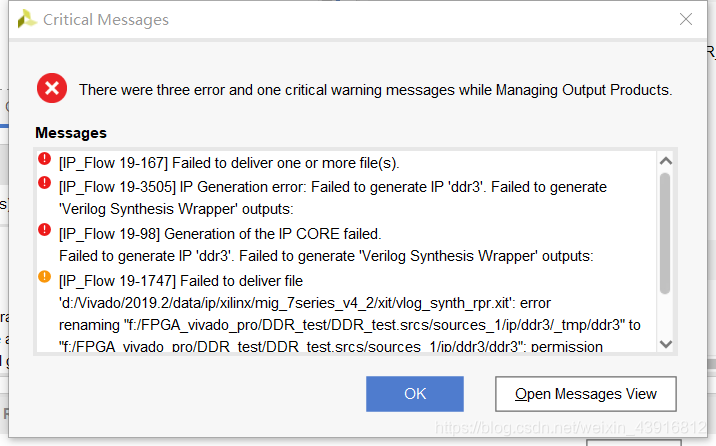

生成MIG报错:

在用vivado的mig ip核做ddr3控制器时,生成时报错

问题描述:

解决方案:

网上有很多说法,比如工程地址太长,没有添加路径之类的,但我试过都解决不了。

我的vivado安装在D盘的,安装完后D盘还剩100G可用空间,我给D盘扩容到300G之后,报错消失,IP核可以综合

第二天更新:

今天又出现之前的问题了,这次我更改了[IP_Flow 19-1747] Failed to deliver file ‘d:/Vivado/2019.2/data/ip/xilinx/mig_7series_v4_2/xit/synthesis.xit’: error renaming “f:/FPGA_vivado_pro/DDR3_test/DDR3_test.srcs/sources_1/ip/ddr3/_tmp/ddr3” to “f:/FPGA_vivado_pro/DDR3_test/DDR3_test.srcs/sources_1/ip/ddr3/ddr3”: permission denied

这条信息中提到的DDR3_test.srcs/sources_1/ip/ddr3/_tmp文件夹权限,添加一个完全控制权限,就可以了

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?