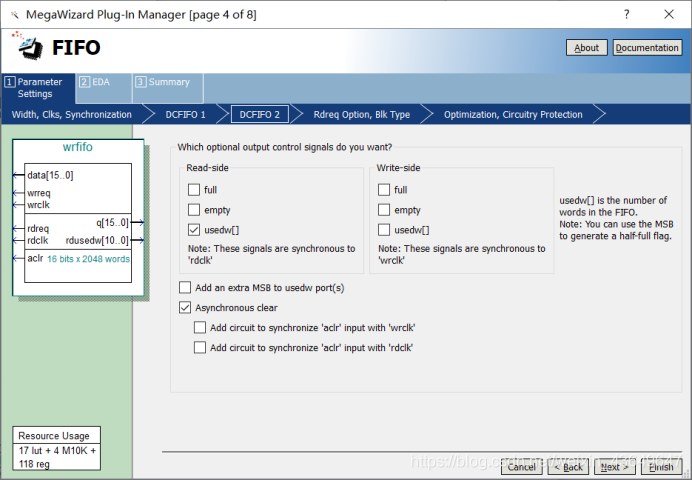

如图,我们在调用FIFO的IP核的时候有这么一个选项,可以选择读端口与写端口的相关信号。今天学习了FIFO中的有效数据量,也就是usedw信号。

从note中可以看出,这个信号是相对于其对应的clk的同步信号。

在上图中,我选择的是读那一侧的同步数据量,那么这个usedw信号就是依靠读时钟来同步的。同理选择写一侧的就是依靠写时钟来同步的。

仿真

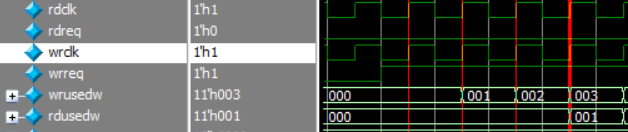

写操作

如图,该仿真是我将读一侧与写一侧的都选上了,先看写操作下的时序。

可见读一侧的数据是相对写时钟延时一个读clk的,这个不用管,只需要知道只相对读信号延时一个clk就行。

主要看rdusedw,这个是读那一侧的同步信号,可见是相对wrusedw延时两个读时钟,应该就是我们平时学习的两级触发器同步,该同步器是受读信号来控制的。

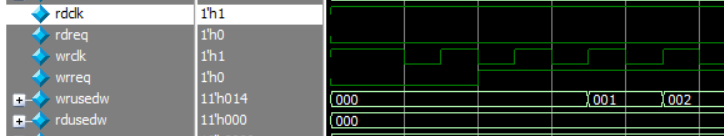

接下来我把读时钟取消来看。

读一侧的数据信号是没有同步到读端口的。

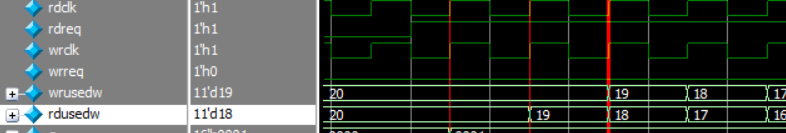

读操作

读操作时,同步到写时钟的数据量信号只延时了一个写时钟,读与写是不一样的,所以只用了一级寄存器延时。

本文详细探讨了FIFO(先进先出)IP核中usedw信号的同步特性,特别是在读写端口的选择下如何影响信号同步。在仿真过程中,作者观察到当选择读端口同步时,rdusedw信号相对于wrusedw延时两个读时钟,而选择写端口同步时,数据量信号仅延时一个写时钟。这表明读写两侧的信号同步机制存在差异,对于理解和正确使用FIFO至关重要。

本文详细探讨了FIFO(先进先出)IP核中usedw信号的同步特性,特别是在读写端口的选择下如何影响信号同步。在仿真过程中,作者观察到当选择读端口同步时,rdusedw信号相对于wrusedw延时两个读时钟,而选择写端口同步时,数据量信号仅延时一个写时钟。这表明读写两侧的信号同步机制存在差异,对于理解和正确使用FIFO至关重要。

3759

3759

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?