一、简介

Zynq-7000 All Programmable SOC,是Xilinx推出的全可编程系统,他将处理器(PS部分)的软件可编程性和FPGA(PL部分)的硬件可编程性集成到了同一芯片上,提供了极大的系统性能、灵活性和可扩展性。Zynq系列旨在为视频监视、汽车驾驶员辅助以及工厂自动化等高端嵌入式应用提供所需的处理与计算性能水平。

PS(Processing System)和PL(Programmable Logic)是zynq的两个核心组件,它们之间通过AXI总线进行连接。

PS(Processing System)是整个zynq平台的核心,负责处理、运算和决策等任务。PS基于ARM架构,由一颗或多颗处理器核构成,并包括了各种外设接口和存储器等组件。PS能够运行Linux等高级操作系统,也支持多种应用程序和算法的运行。

PL(Programmable Logic)是Zynq平台中的可编程逻辑部分,它基于Xilinx的FPGA技术。通过使用Vivado等开发工具,用户可以根据应用需求对PL进行编程和定制,实现各种数字逻辑功能。

PL和PS之间通过AXI(Advanced eXtensible Interface)总线进行通信和数据传输。PS端和PL端都可以作为AXI的主设备和从设备。主设备负责启动数据传输,并控制数据的流向和速率;从设备则负责接收数据,并响应主设备的控制信号。通过使用AXI接口,可以实现高性能、高速度的数据传输,并且可以根据应用需求灵活地配置AXI接口的参数。

在Zynq平台中,PS和PL的分工协作可以实现更高效、更灵活和更低功耗的计算与处理能力。

二、架构框图

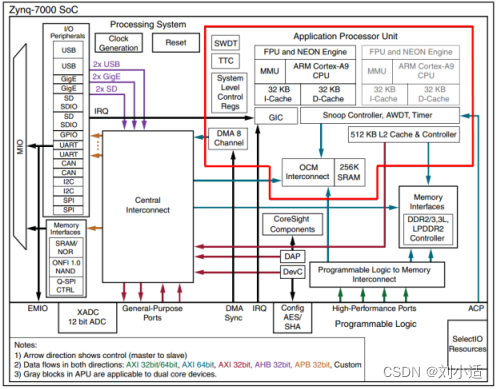

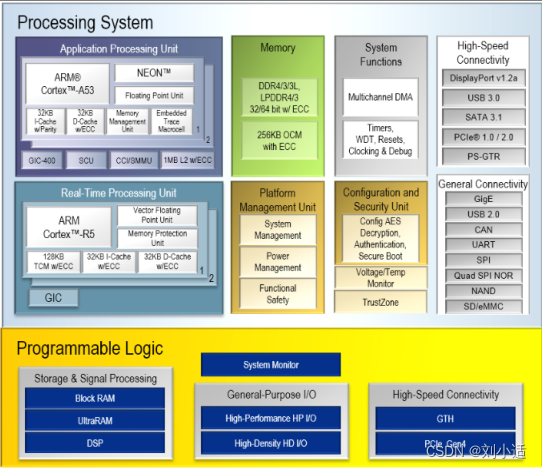

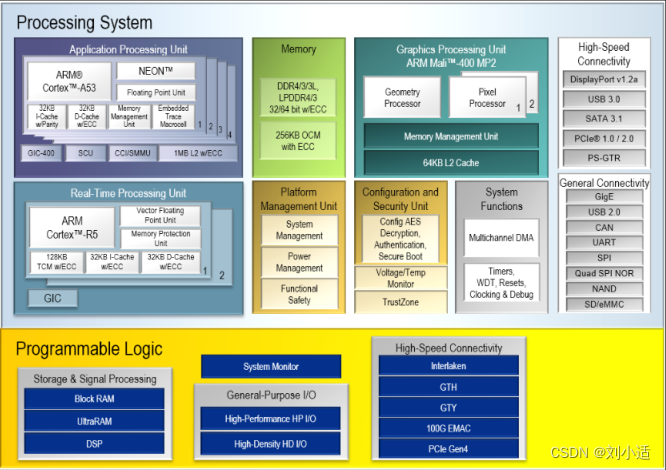

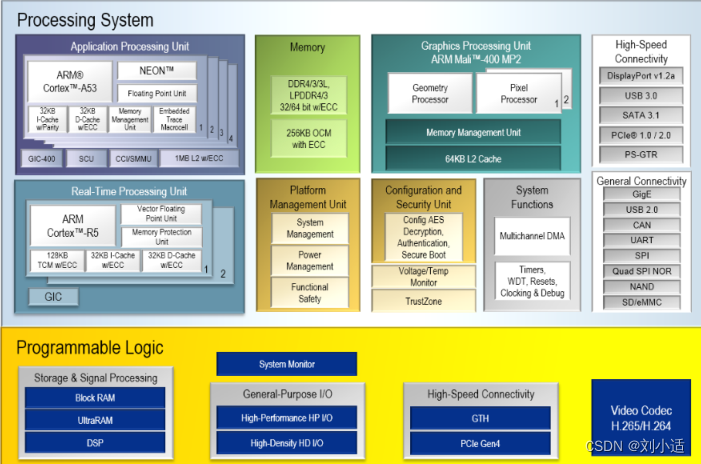

Zynq-7000 SoC的框图如下所示,其整体分为上下两个矩形框图,上面的矩形框图为PS部分,下面的矩形框图为PL部分。

Zynq将arm处理器为主的PS系统作为为核心,而PL部分只是其一个外设,通过AXI总线进行通信。从框图中容易看出,Zynq PS系统里并非只有 ARM 处理器,还有一组相关的处理资源,形成了一个应用处理器单元(Application Processing Unit, APU),另外还有扩展外设接口、 cache 存储器、存储器接口、互联接口和时钟发生电路等模块。

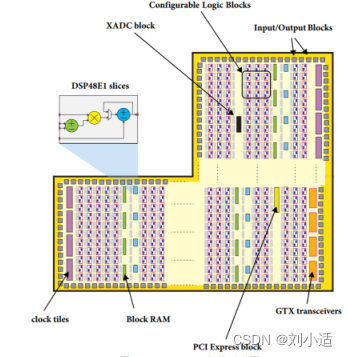

Zynq PL 部分等价于 Xilinx 7 系列 FPGA,其资源主要由可编程输入/输出单元、可编程逻辑单元、嵌入式块RAM、布线资源、底层嵌入功能单元和内嵌专用硬核等组成。PL部分的架构如下图所示。

PS 和 PL 之间有9个根据AXI4总线协议进行通信的端口,将其分为三类:

1、 通用 AXI(General Purpose AXI):一条 32 位数据总线,适合 PL 和 PS 之间的中低速通信。接口是透传的不带缓冲。总共有四个通用接口:两个 PS 做主机,另两个 PL 做主机。

2、 加速器一致性端口(Accelerator Coherency Port):在 PL 和 APU 内的 SCU 之间的单个异步连接,总线宽度为 64 位。这个端口用来实现 APU cache 和 PL 的单元之间的一致性。 PL 是做主机的。

3、 高性能端口(High Performance Ports):四个高性能 AXI 接口,带有 FIFO 缓冲来提供“批量”读写操作,并支持 PL 和 PS 中的存储器单元的高速率通信。数据宽度是 32 或 64 位,在所有四个接口中PL 都是做主机的。

值得指出的是,虽然zynq 中集成的了硬核arm处理器,但依然可以用FPGA 来搭建嵌入式处理器,即在PL部分实现 MicroBlaze 处理器,其优势在于数量以及实现方式的灵活性。zynq中的硬件处理器和软核处理器并不冲突,可以使用 PL 的逻辑资源搭建一个 Microblaze 软核处理器,来和 ARM 硬核处理器协同工作。

三、zynq SoC系列

Zynq SoC系列是Xilinx FPGA+ARM硬核架构的系列产品,其分类为:

Zynq-7000系列:Zynq 7000 SoC 系列集成 ARM® 处理器的软件可编程性与 FPGA 的硬件可编程性,不仅可实现重要分析与硬件加速,同时还在单个器件上高度集成 CPU、DSP、ASSP 以及混合信号功能。Zynq 7000 系列包括单核 Zynq7000S 器件和双核 Zynq-7000 器件,是具有出色单位功耗性价比的全面可扩展的 SoC 平台,可充分满足应用需求。Zynq7000S 器件采用与 28nm Artix™ 7 可编程逻辑配对的单核 ARM Cortex®-A9 处理器,是可扩展 Zynq-7000 平台的最低成本入门级产品。Zynq-7000S 和 6.25Gb/s 收发器一起提供,配备有通用固化外设,所实现的成本优化系统集成是电机控制与嵌入式视觉等工业物联网应用的理想选择。Zynq 7000 器件配备双核 ARM Cortex-A9 处理器,该处理器与基于 28nm Artix7 或 Kintex 7 的可编程逻辑集成,可实现优异的性能功耗比和最大的设计灵活性。Zynq 7000 器件具有高达 6.25M 的逻辑单元以及从 6.6Gb/s 到 12.5Gb/s 的收发器,可为多摄像头驾驶员辅助系统和 4K2K 超高清电视等大量嵌入式应用实现高度差异化的设计。

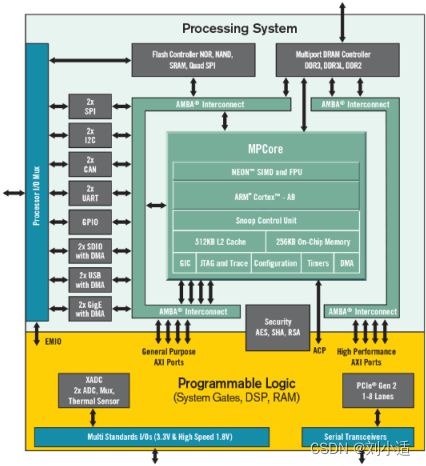

Zynq 7000s框图

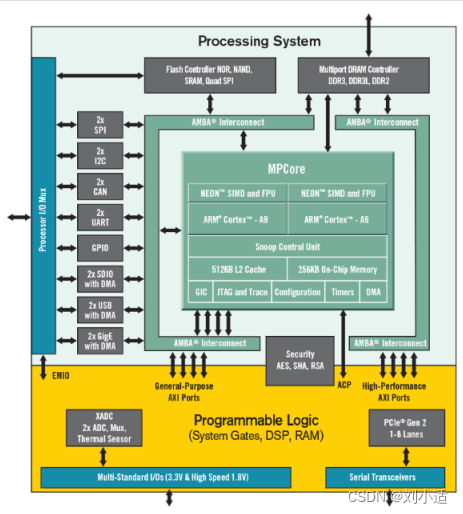

Zynq7000 框图

Zynq UltraScale+ MPSoC系列:Zynq UltraScale+ MPSoC 器件不仅提供 64 位处理器可扩展性,同时还将实时控制与软硬件引擎相结合,支持图形、视频、波形与数据包处理。置于包含通用实时处理器和可编程逻辑的平台上,三个不同变体包括双核应用处理器 (CG) 器件、四核应用处理器和 GPU (EG) 器件、以及视频编解码器 (EV) 器件, 为 5G 无线、下一代 ADAS 和工业物联网创造了无限可能性。三者均为16nm FinFET+可编程逻辑结构。

Zynq UltraScale+ MPSoC CG器件框图

Zynq UltraScale+ MPSoC EG器件框图

Zynq UltraScale+ MPSoC EG器件框图

三者对比

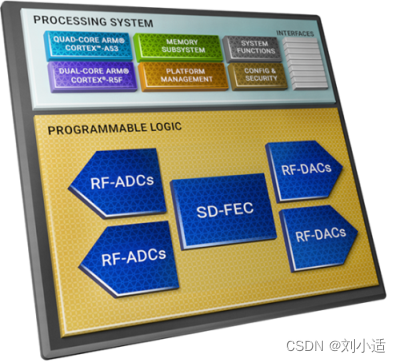

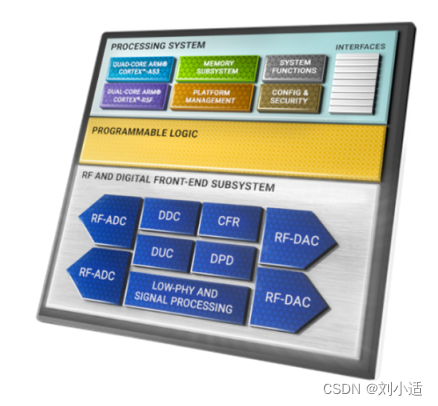

Zynq UltraScale+ RFSoC平台:Zynq UltraScale+ RFSoC 是一种异构计算架构,包括完整的 Arm 处理子系统、FPGA 架构,以及 RF 信号链中的完整模数可编程性,其不仅可为不同的应用提供一个完整的单片软件定义无线电平台,而且还有助于随着市场动态的发展,生产无线电变体。为16nm FinFET+可编程逻辑结构。Zynq UltraScale+ RFSoC 将 Soft-decision Forward Error-correction Cores (SD-FEC) IP 块与低密度奇偶校验 (LDPC) 及涡轮编解码器支持集成在一起。硬化内核可在低时延下提供超过 1Gb/s 的性能,与软逻辑实现方案相比,功耗更低、占位面积更小。Zynq RFSoC DFE 是最新的自适应 RFSoC 平台,其针对重要的 DFE 处理集成比软逻辑更硬的 IP。Zynq RFSoC DFE 可为 5G 新无线电实现高度灵活的解决方案,能够低功耗、低成本地运行高达 7.125GHz 的输入输出频率。

Zynq UltraScale+ RFSoC框图

Zynq RFSoC DFE框图

Versal ACAP系列:Versal ACAP具有高度集成的多核计算平台,可以适应不断变化的算法,并且可以在硬件和软件级别进行动态自定义,以适应各种应用和工作负载。它围绕可编程NoC进行设计,软件开发者和硬件程序员可以轻松地对其进行编程。为7nm可编程逻辑结构。

总的来说,从前到后,其性能越来越好。另外,一般简称Zynq就是指的 Zynq-7000 器件。

四、参考资料

正点原子:ZYNQ 之 FPGA开发指南 V2.0

Xilinx官网:SoC、MPSoC 和 RFSoC (xilinx.com)

2663

2663

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?