FPGA串口波特率与系统时钟频率关系

FPGA主板频率是50Mhz,T=20ns

9600波特率指的是9600bps,9600bit/s

然后周期是1/速率 = 1/9600 = 1.0416666667*10^(-4)=104167ns (也就是说每104167ns传输一个bit位的数据)

波特率分频计数值:104167/System_clk_period=104167/20=5208

波特率分频计数值 :50_000_000/96000 = 5208 (系统时钟频率为50MHZ,也就是说系统时钟经过5208次计数后到达 5208*20=104167ns,即经过1个波特率周期,一个波特率周期可以完成一个bit位数据的传输)

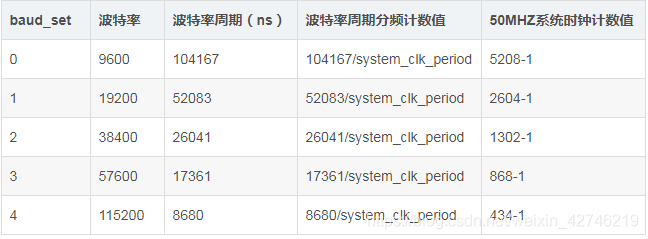

计数值与波特率之间的关系如表 1 所示:

本文详细解析了FPGA中串口波特率与系统时钟频率的关系,以50MHz系统时钟为例,计算9600波特率下所需分频计数值,揭示了波特率设置原理。

本文详细解析了FPGA中串口波特率与系统时钟频率的关系,以50MHz系统时钟为例,计算9600波特率下所需分频计数值,揭示了波特率设置原理。

422

422