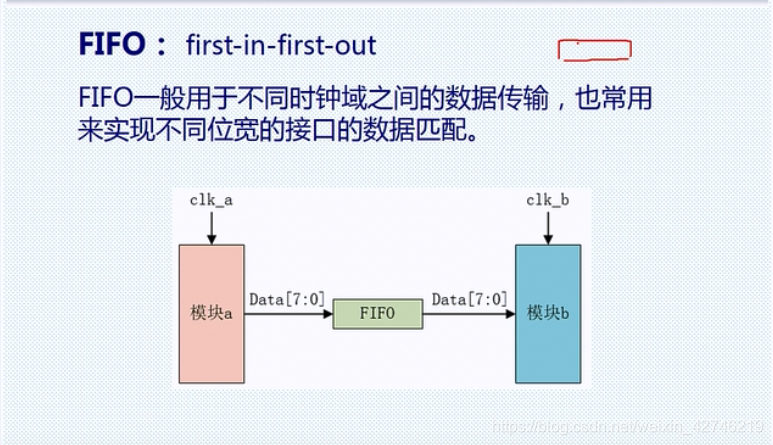

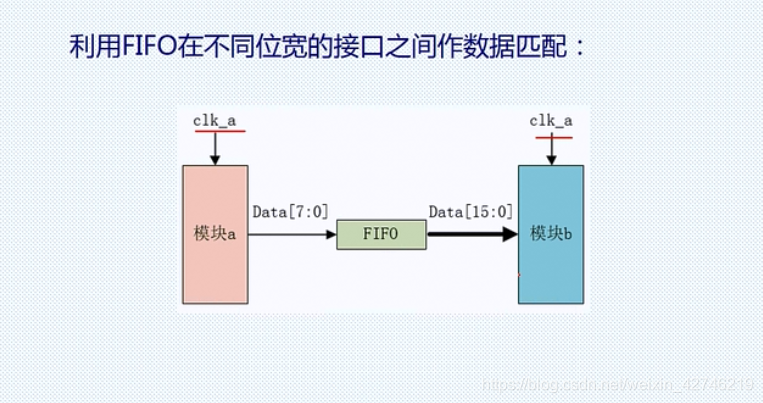

FIFO简介:

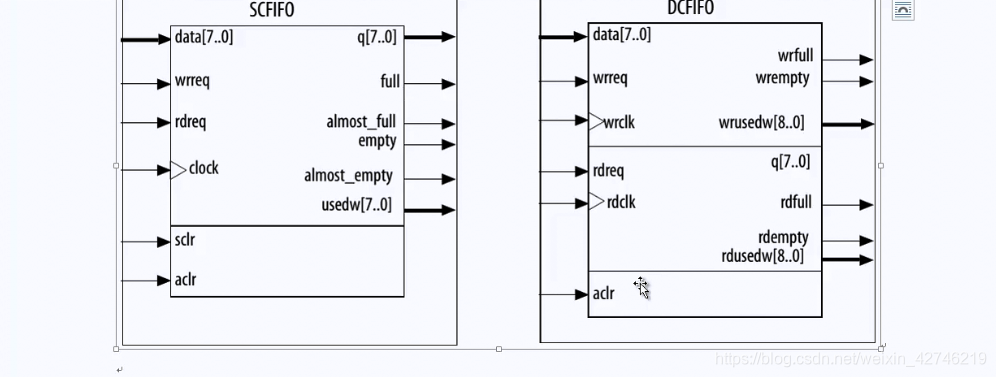

data[7:0] :数据输入端口,当wrreq信号为高电平且clok信号为高电平时将data线上的数据写入到FIFO中

wrreq:写请求信号,高电平有效

rdreq:读请求信号,高电平有效

q[7:0]:数据读取端口,当rdreq信号为高电平,且clok信号为高电平时,FIFO 将数据放到q数据线上

full:写满信号标志位,当FIFO中数据写满时改为置1

almost_full :即将写满信号(可配置还差多少个数据即将写满,例如配置为3,表示还差三个数据的时候将almost_full 信号拉高)

empty:FIFO读空信号,全空时置1

almost_empty:即将读空信号(可配置,例如配置为3,表示还差三个数据将FIFO读空的时候,讲almost_empty 信号拉高)

usedw[7:0]:当前FIFO中可用的数据个数

sclr:同步清0信号,该信号为1时,并且在clok信号来到时将FIFO中的数据清0

aclr:异步清0信号,该信号为1时,将FIFO中数据立即清0,不受时钟的约束

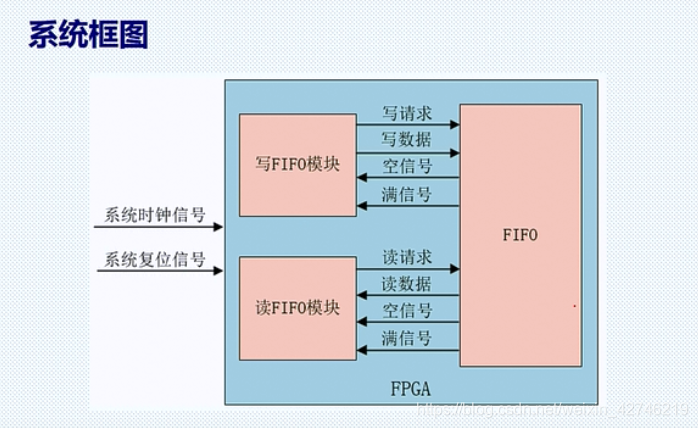

基于FPGA的FIFO读写实验介绍

基于FPGA的FIFO读写实验介绍

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1458

1458

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?