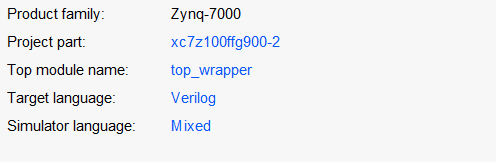

Zynq 板卡型号为 7100 ,具体如下图 :

一 :ZYNQ 中的 IO 规则

要想配置 Zynq 的 IO 资源,就必须先了解 其 IO 的使用规则 。

该部分中有的知识点摘录自 :

被王大锤砸的核桃

传送门

GPIO

GPIO (General-Purpose IO),即通用 IO 接口,是 ZYNQ 所有 IO 的统称,它包括 MIO,EMIO,AXI GPIO 和 AXI Lite 自定义的 GPIO 。它们的区别如下 :

MIO

M7100FA 属于 Zynq7000 系列,故有 54 个 MIO 资源,共占54 bit ,占用 IO 号为 0-53,分布在 GPIO 的 Bank0 和 Bank1 部分,是 PS 上的资源。

MIO 是 PS 端独立的 IO,对 PL 端透明,它可以用在GPIO、SPI、UART、TIMER、Ethernet、USB等功能上 ;在配置 MIO 时,不需要配置引脚。

EMIO

EMIO 是为了防止 Zynq PS 端 IO 资源不够,使用的部分 PL 端资源当做扩展接口,故称作 EMIO (Express MIO) 。

EMIO 分布在 Bank2 和 Bank 3 ,占用 IO 号为 54-117,共占 64 bit 。由于其调用了 PS 端部分 IO 资源,所以在用 EMIO 时需要在 PL 端对管脚 进行声明;并生成 PL 端 bit 文件,烧写到 FPGA 中。

本文详细介绍了ZYNQ 7 Processing System中的GPIO,包括MIO、EMIO和AXI GPIO的区别,如管脚分布、资源消耗和功能划分。同时,讲解了IP核配置过程,如MIO Configuration、Clock Configuration和DDR Configuration,重点在于GPIO在Zynq7000中的应用和配置技巧。

本文详细介绍了ZYNQ 7 Processing System中的GPIO,包括MIO、EMIO和AXI GPIO的区别,如管脚分布、资源消耗和功能划分。同时,讲解了IP核配置过程,如MIO Configuration、Clock Configuration和DDR Configuration,重点在于GPIO在Zynq7000中的应用和配置技巧。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2630

2630

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?