版权声明:本文为博主原创文章,遵循 CC 4.0 BY-SA 版权协议,转载请附上原文出处链接和本声明。

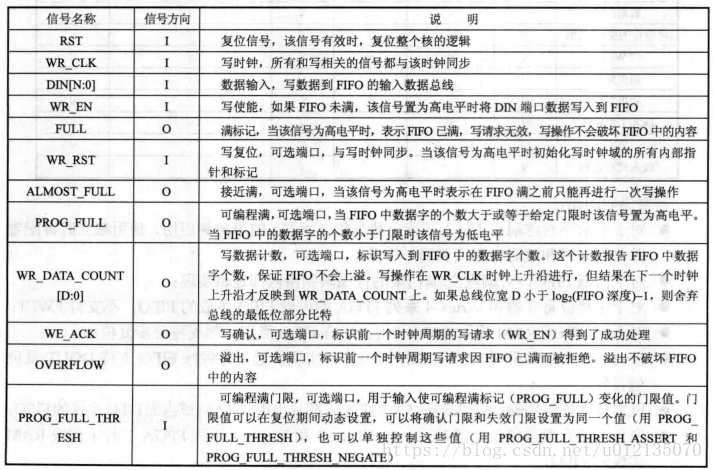

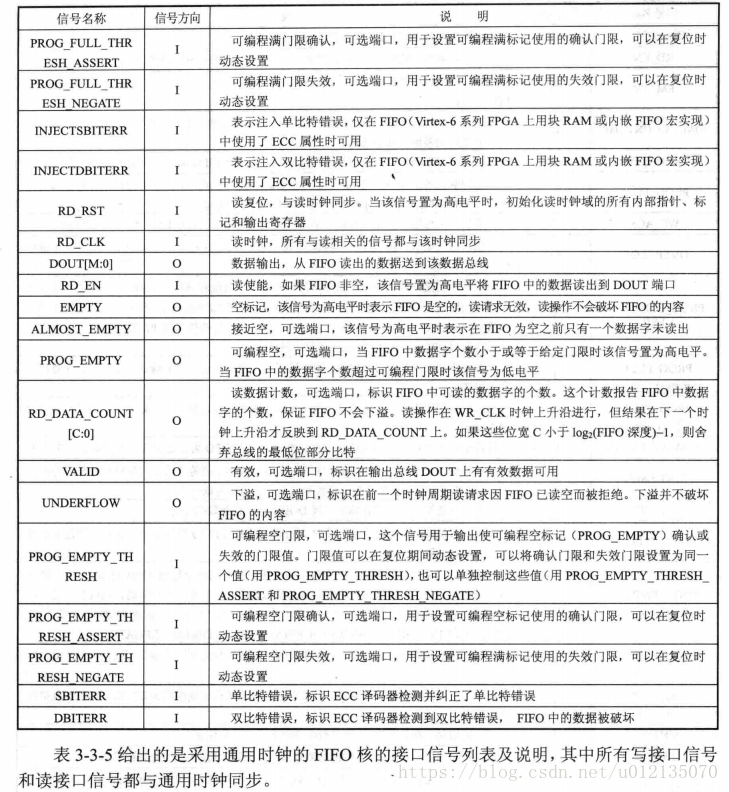

<xlinx FPGA应用进阶 通用IP核详解和设计开发>读书摘录:

1.

2. 3.仿真模型

3.仿真模型

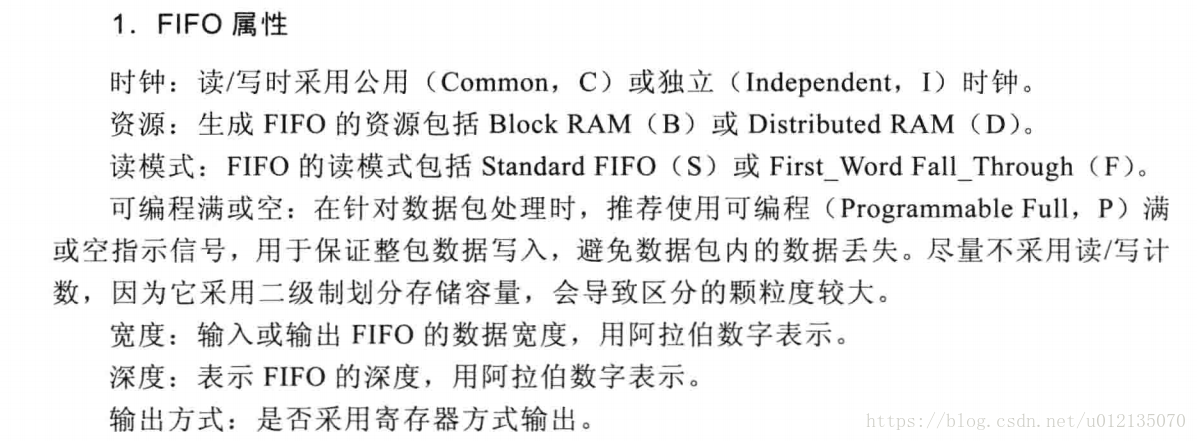

特点总结:1)复位后会有busy状态,需要等待wr_rst_busy信号低电平后才能正常写入

2)prog_full信号的高电平长度可调

3)仿真中的读状态很奇怪,并没有正常读取,都是XXX的状态。

所用的testbench:

`timescale 1ns / 1ps

module fifo_tb(

);

wire FIFO_READ_0_empty;

wire [9:0]FIFO_READ_0_rd_data = 0;

reg FIFO_READ_0_rd_en = 0;

wire FIFO_WRITE_0_full;

reg [9:0]FIFO_WRITE_0_wr_data= 0;

reg FIFO_WRITE_0_wr_en= 0;

wire prog_full_0;

reg rd_clk_0= 0;

wire rd_rst_busy_0;

reg rst_0= 1;

reg wr_clk_0= 0;

wire wr_rst_busy_0;

fifo_logicore_wrapper i1mysyst

(.FIFO_READ_0_empty(FIFO_READ_0_empty),

.FIFO_READ_0_rd_data(FIFO_READ_0_rd_data),

.FIFO_READ_0_rd_en(FIFO_READ_0_rd_en),

.FIFO_WRITE_0_full(FIFO_WRITE_0_full),

.FIFO_WRITE_0_wr_data(FIFO_WRITE_0_wr_data),

.FIFO_WRITE_0_wr_en(FIFO_WRITE_0_wr_en),

.prog_full_0(prog_full_0),

.rd_clk_0(rd_clk_0),

.rd_rst_busy_0(rd_rst_busy_0),

.rst_0(rst_0),

.wr_clk_0(wr_clk_0),

.wr_rst_busy_0(wr_rst_busy_0));

always #5 wr_clk_0 = ~wr_clk_0;

always #20 rd_clk_0 = ~rd_clk_0;

initial begin

rst_0 = 1;

#100;

rst_0 = 0;

#100;

@(negedge wr_rst_busy_0)

FIFO_WRITE_0_wr_en = 1'b1;

repeat (512) begin

#10

FIFO_WRITE_0_wr_data = FIFO_WRITE_0_wr_data + 10'd1;

end

#100;

FIFO_WRITE_0_wr_en = 1'b0;

#1000;

FIFO_READ_0_rd_en = 1'b1;

repeat (512) begin

#(40);

end

#100;

FIFO_READ_0_rd_en = 1'b0;

#400;

$stop;

end

endmodule

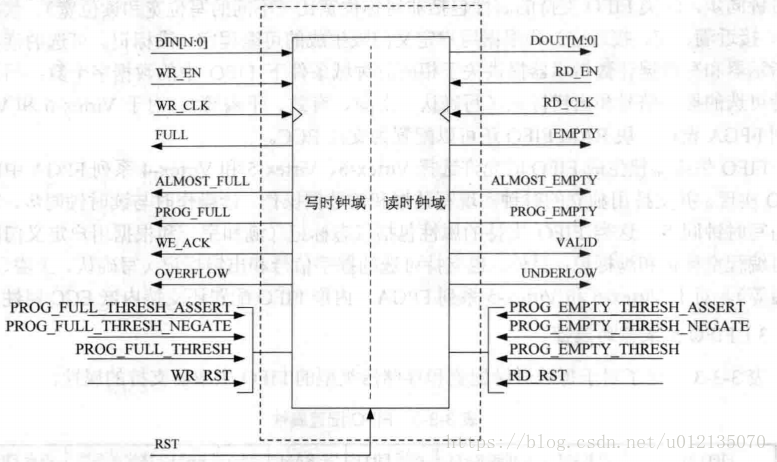

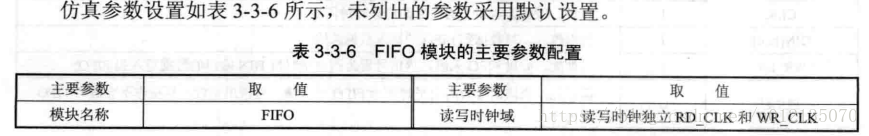

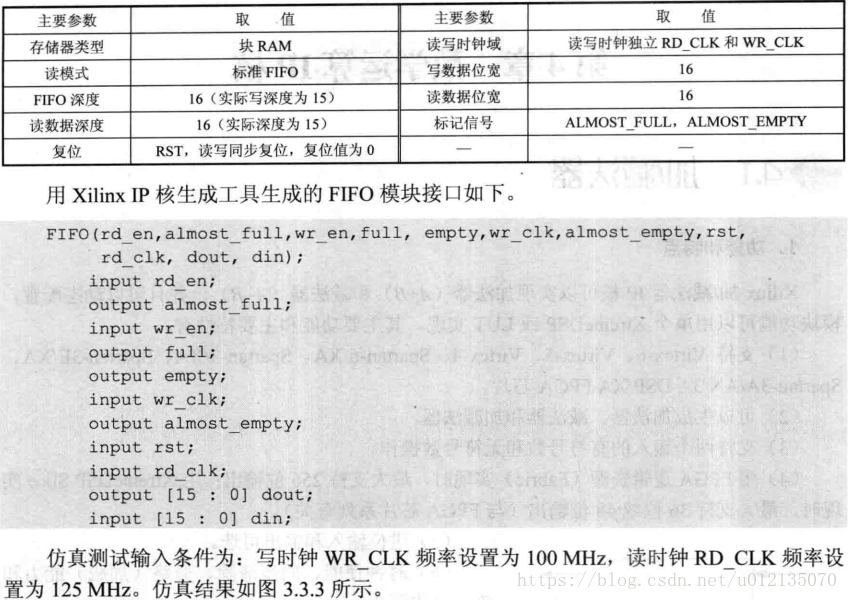

刘东华的xilinx系列FPGA芯片IP核详解>读书摘录:

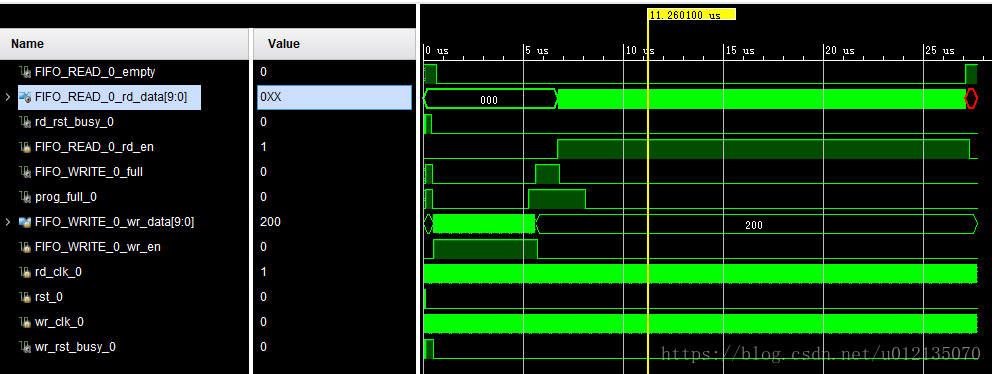

1.

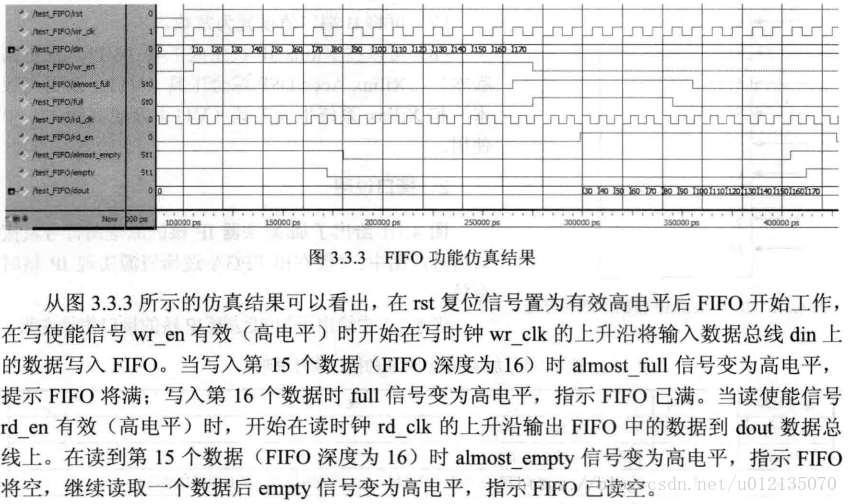

2.仿真结果

其他参考资料:

1、https://blog.youkuaiyun.com/xuexiaokkk/article/details/47753459

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?