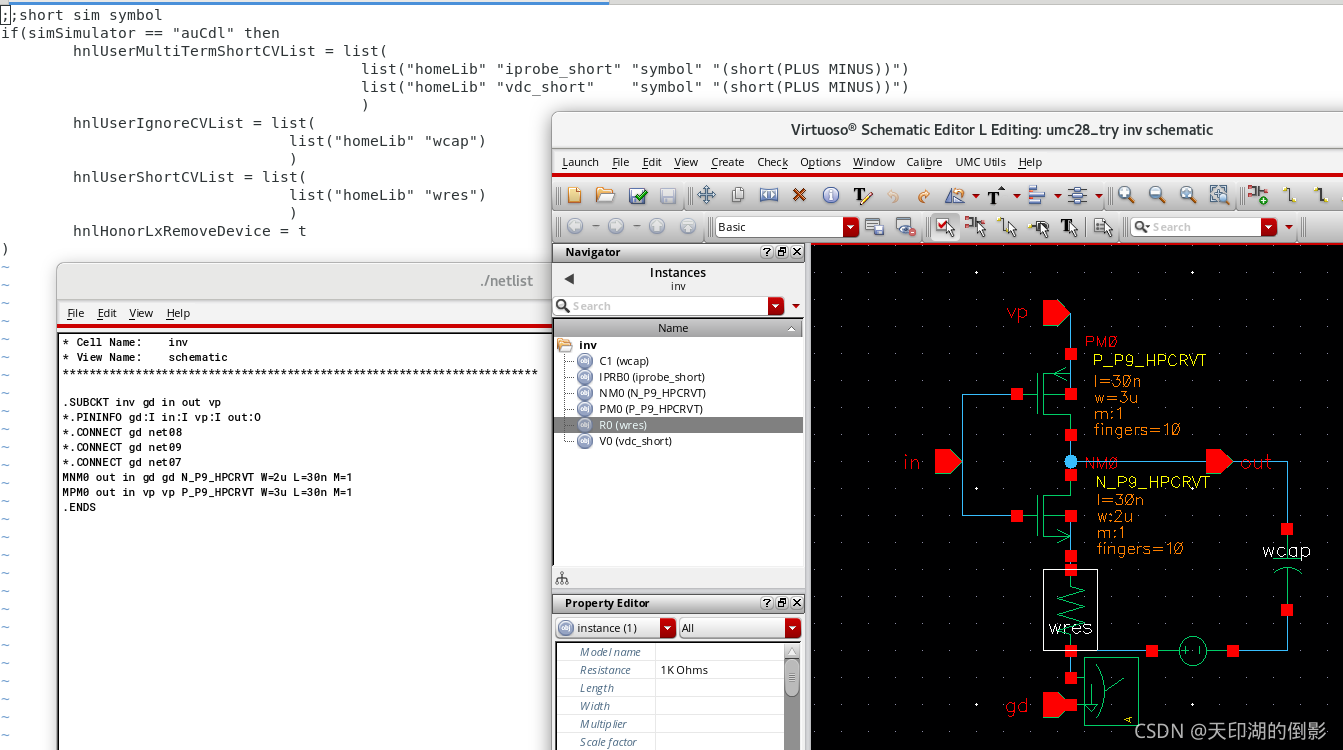

感谢EDA经验分享群的群友"郁离子"教授的方法,在.simrc里添加如下一段话,电路图示例和CDL out的结果如图所示。其他多端口的器件处理方法和short之后net的命名问题可以参考cadence help documentation。

备注:

使用上述方法存在一个问题,使用spectre仿真的时候抽取的网表也没有寄生电阻电容。

另一种替代方案:

电容直接添加CDF描述,lvsIgnore,boolen,true;

电阻在symbol编辑状态下,shift+Q,添加参数 lxRemoveDevice = (short(PLUS MINUS))

本文介绍了在Cadence环境中通过修改.simrc文件来处理多端口器件和short之后net命名的问题,以及在spectre仿真中缺失寄生元件的解决方法。另外,提出了一种替代方案,即直接在CDF描述中添加电容属性,并在电阻编辑状态下设置特定参数以去除设备。

本文介绍了在Cadence环境中通过修改.simrc文件来处理多端口器件和short之后net命名的问题,以及在spectre仿真中缺失寄生元件的解决方法。另外,提出了一种替代方案,即直接在CDF描述中添加电容属性,并在电阻编辑状态下设置特定参数以去除设备。

902

902

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?