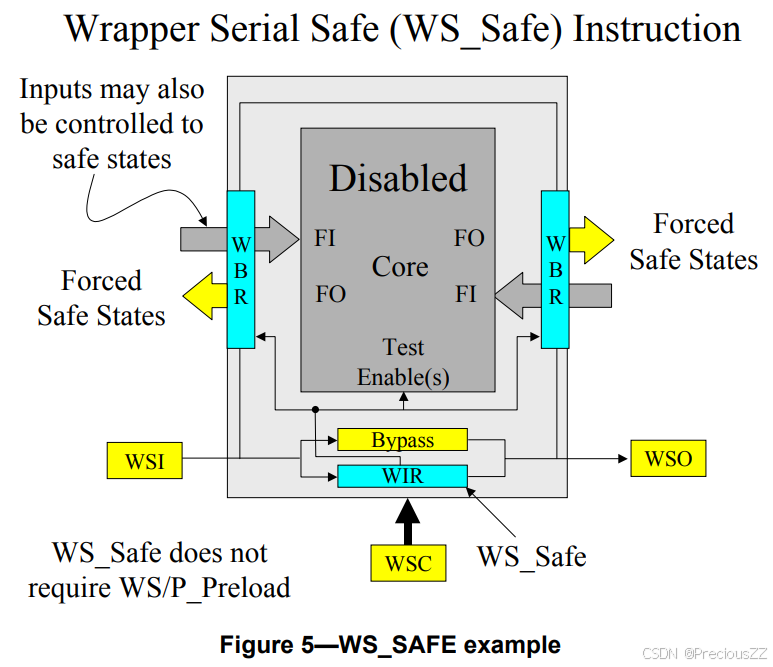

7.8 WS_SAFE instruction The optional WS_SAFE instruction allows the state of the signals driven from WFOs to be determined from the WBR while the WBY is selected as the serial path between the serial input (WSI) and serial output (WSO) of the wrapper. The signals driven from the WFOs will not change while the WS_SAFE instruction is selected. The WS_CLAMP instruction can also be used to put the wrapper into a safe state by utilizing a Wx_PRELOAD instruction to shift in the proper states and then clamping them with the WS_CLAMP instruction. However, it is important to allow a straightforward way for the core integrator to put wrappers into a safe state. This is why there is a separate instruction for WS_SAFE. This instruction allows the core integrator to more easily put various wrappers into safe states while other portions of an SoC are being tested. The rules in 7.8.1 apply where the WS_SAFE instruction is provided. NOTE—Following use of the WS_SAFE instruction, the core circuitry may be in an indeterminate state that will persist until a system reset is applied. Therefore, the core circuitry may need to be reset on return to normal (i.e., nontest) operation.

7.8 WS_SAFE 指令:可选的 WS_SAFE 指令允许在选择 WBY 作为封装器的串行输入(WSI)和串行输出(WSO)之间的串行路径时,从 WBR 确定从 WFO 驱动的信号的状态。当选择 WS_SAFE 指令时,从 WFO 驱动的信号不会改变。WS_CLAMP 指令也可以通过使用 Wx_PRELOAD 指令移入适当的状态,然后用 WS_CLAMP 指令夹紧它们,从而将封装器置于安全状态。然而,重要的是要为核心集成商提供一种直接的方法将封装器置于安全状态。这就是为什么有一个单独的 WS_SAFE 指令。这个指令允许核心集成商在测试片上系统(SoC)的其他部分时更容易地将各种封装器置于安全状态。在提供 WS_SAFE 指令的情况下,7.8.1 中的规则适用。注意:在使用 WS_SAFE 指令后,核心电路可能处于不确定状态,这种状态将持续存在,直到应用系统复位。因此,在恢复正常(即非测试)操作时,核心电路可能需要复位。

7.8.1 Specifications Rules a) While the WS_SAFE instruction is selected, the WBY shall be connected for serial access between WSI and WSO during wrapper data scan operations. b) While the WS_SAFE instruction is selected, the state of all signals driven from WFOs shall be hardwired to fixed values that have been predetermined at wrapper instantiation. NOTE—The data output from the WBR shall be safe and established as a result of entering the WS_SAFE instruction. c) When the WS_SAFE instruction is selected, the core circuitry shall be controlled so that it cannot be damaged as a result of signals received at the core data input or core clock input terminals. d) While the WS_SAFE instruction is selected, the WSC shall be utilized for test control. Recommendations e) While the WS_SAFE instruction is selected, the core circuitry should be put into a quiet mode (e.g., reset or clock off).

这段文本是关于特定规范的说明。首先提到当选择 “WS_SAFE” 指令时,在包装器数据扫描操作期间,WBY 应连接以实现 WSI 和 WSO 之间的串行访问。接着指出在选择 “WS_SAFE” 指令时,从 WFO 驱动的所有信号的状态应硬连线为在包装器实例化时预先确定的固定值。注释说明由于进入 “WS_SAFE” 指令,来自 WBR 的数据输出应是安全的并已确定。然后表明当选择 “WS_SAFE” 指令时,核心电路应被控制,以便不会因在核心数据输入或核心时钟输入端子处接收的信号而受损。还提到在选择 “WS_SAFE” 指令时,WSC 应被用于测试控制。最后给出建议,当选择 “WS_SAFE” 指令时,核心电路应置于安静模式(例如,复位或关闭时钟)。

“Permissions(权限)” 可能是在讨论某种特定情境下的许可规定。

“f) The binary code for the WS_SAFE instruction may be selected by the wrapper designer.” 这句话的意思是:f 项规定,WS_SAFE 指令的二进制代码可以由包装器设计者进行选择。这里明确了包装器设计者在特定指令(WS_SAFE 指令)的二进制代码选择方面拥有权限。

7.8.2 Description During testing of a particular core or cluster of cores on a system chip, it may be necessary to place static values on signals that control operation of circuitry not involved in the test, e.g., to place the core in a state where it will not respond to signals received from the circuitry under test. The optional WS_SAFE instruction is similar to the WS_CLAMP instruction in that it allows safe static values to be applied using the WBRs of the appropriate core wrapper, but does not retain these registers in the serial path during test application. In a case in which the WS_SAFE instruction is used to create safe static signals, the following process would be used. It is presumed in the following example that every wrapper implements the optional WS_SAFE instruction. — Shift the WS_SAFE instruction into all core wrappers that will provide safe static signals during the upcoming test. Call this group of wrappers G. If test setup data are required in wrappers not in G (i.e., in the wrappers that will participate actively in the upcoming test), another instruction (e.g., WS_EXTEST) may be loaded into these core wrappers simultaneously with the loading of WS_SAFE into core group G. — From this point on, until the test is concluded, every time instructions are to be scanned into core wrappers in the SoC, enter the WS_SAFE instruction into the wrappers in G. As long as the WS_SAFE instruction is maintained as the active instruction in the wrappers of G, the output signal values of these wrappers will be determined by the safe data at their WBR outputs. Also, as a consequence of the use of the WS_SAFE instruction, the wrappers in G all have their WBYs selected throughout the test; thus, they contribute very little to the overall test time. Figure 5 shows an example of the configuration of the wrapper during the WS_SAFE instruction.

这段文本主要描述了在系统芯片上对特定内核或内核集群进行测试时,WS_SAFE 指令的作用和使用过程。

首先提到在芯片测试中,可能需要在不参与测试的电路控制信号上设置静态值,例如将内核置于不会响应来自被测电路信号的状态。WS_SAFE 指令与 WS_CLAMP 指令类似,它允许使用适当的内核包装器的 WBR(可能是某种寄存器)应用安全静态值,但在测试应用期间不会将这些寄存器保留在串行路径中。

接着以一个示例说明使用 WS_SAFE 指令创建安全静态信号的过程:

- 将 WS_SAFE 指令移入所有在即将进行的测试中提供安全静态信号的内核包装器,称这个包装器组为 G。如果不在 G 中的包装器(即那些将积极参与即将进行的测试的包装器)需要测试设置数据,可以在将 WS_SAFE 加载到核心组 G 的同时,将另一个指令(例如 WS_EXTEST)加载到这些核心包装器中。

- 从此时起,直到测试结束,每次要将指令扫描到 SoC(系统芯片)中的核心包装器时,都将 WS_SAFE 指令输入到 G 中的包装器。只要 WS_SAFE 指令在 G 的包装器中保持为活动指令,这些包装器的输出信号值将由其 WBR 输出处的安全数据决定。并且由于使用了 WS_SAFE 指令,G 中的包装器在整个测试过程中都选择了它们的 WBY;因此,它们对总体测试时间的贡献非常小。最后,图 5 展示了在 WS_SAFE 指令期间包装器的配置示例。

:

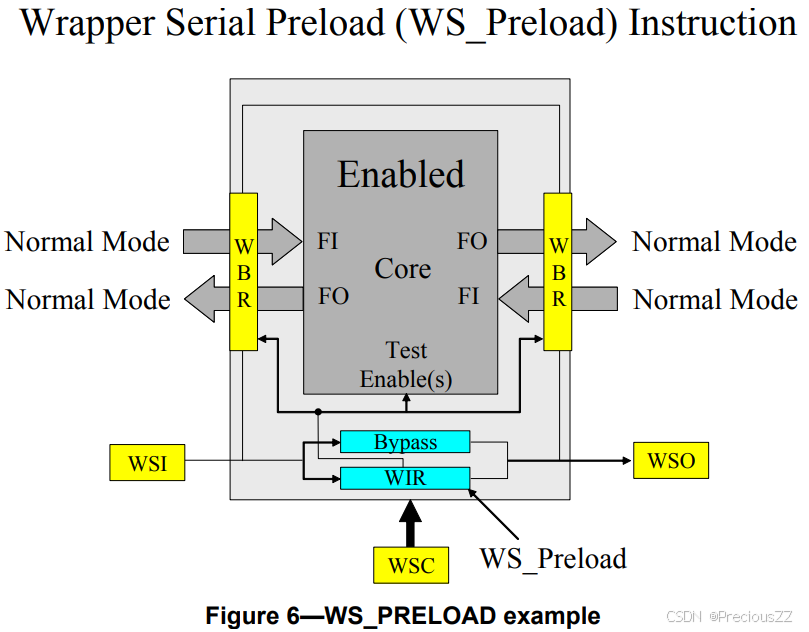

7.9 WS_PRELOAD instruction The WS_PRELOAD instruction enables the wrapper to be functionally configured. Wrappers that have a WBR composed entirely of cells with a silent shift path must include the WS_PRELOAD instruction. The WS_PRELOAD instruction allows data values to be loaded into the latched parallel outputs of the registers in the silent shift path of the WBR. The data are loaded into the silent shift path of wrapper cells, and then the data are loaded into the update stage, if present, during the Update operation. This instruction would typically be utilized before other instructions are selected (e.g., WS_EXTEST, WS_CLAMP). 7.9.1 Specifications Rules a) If the WBR contains a silent shift path, there shall be a WS_PRELOAD instruction. b) While the WS_PRELOAD instruction is selected, only the WBR shall be connected for serial access between WSI and WSO during the Shift operation (i.e., no other test data register may be connected in series with the WBR). c) While the WS_PRELOAD instruction is selected, the Shift operation of the WBR shall have no effect on the operation of the core or UDL. d) While the WS_PRELOAD instruction is selected, the WSC shall be utilized for test control. Recommendations e) While the WS_PRELOAD instruction is selected, if the core is not being used in its normal operation, the core circuitry should be put into a quiet mode (e.g., reset or clock off). Permissions f) The binary code for the WS_PRELOAD instruction may be selected by the wrapper designer.

7.9 WS_PRELOAD 指令:该指令能使包装器在功能上进行配置。如果包装器的 WBR(Wrapper Boundary Register,包装器边界寄存器)完全由具有无声移位路径的单元组成,则必须包含 WS_PRELOAD 指令。WS_PRELOAD 指令允许将数据值加载到 WBR 的无声移位路径中的寄存器的锁存并行输出端。数据被加载到包装器单元的无声移位路径中,然后如果存在更新阶段,则在更新操作期间将数据加载到该阶段。此指令通常在选择其他指令(例如 WS_EXTEST、WS_CLAMP)之前使用。

7.9.1 规范:

规则:

a)如果 WBR 包含无声移位路径,则应有一个 WS_PRELOAD 指令。

b)在选择 WS_PRELOAD 指令时,在移位操作期间,只有 WBR 应连接以在 WSI(Wrapper Serial Input,包装器串行输入)和 WSO(Wrapper Serial Output,包装器串行输出)之间进行串行访问(即,不能有其他测试数据寄存器与 WBR 串联连接)。

c)在选择 WS_PRELOAD 指令时,WBR 的移位操作对内核或用户定义逻辑(UDL)的操作没有影响。

d)在选择 WS_PRELOAD 指令时,应使用 WSC(Wrapper Scan Control,包装器扫描控制)进行测试控制。

建议:

e)在选择 WS_PRELOAD 指令时,如果内核在正常操作中未被使用,内核电路应置于安静模式(例如,复位或关闭时钟)。

权限:

f)WS_PRELOAD 指令的二进制代码可由包装器设计者选择。

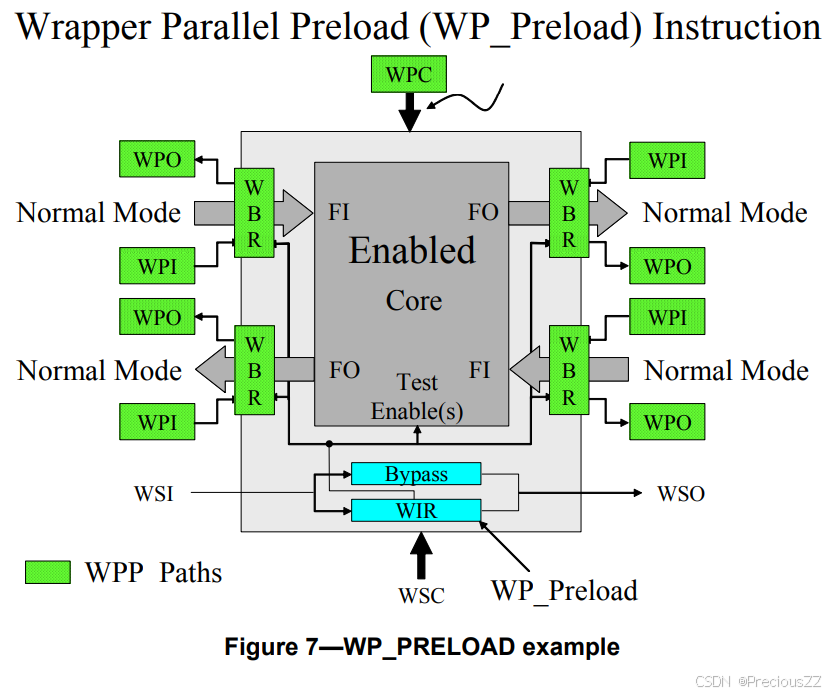

7.9.2 Description The WS_PRELOAD instruction is used to allow shifting of the WBR, via WSI to WSO, without causing interference to the operation of the core or UDL attached to the WBR. WS_PRELOAD allows an initial data pattern to be placed at the latched parallel outputs of the silent shift path register cells through a scan load operation. For example, prior to selection of the WS_EXTEST instruction, data can be loaded onto the latched parallel outputs using WS_PRELOAD. As soon as the WS_EXTEST instruction has been transferred to the update register of the instruction register, the preloaded data are driven from the WFOs. This ensures that known data are driven immediately when the WS_EXTEST instruction is entered. Without WS_PRELOAD, indeterminate data may be driven until the first scan load is complete. Figure 6 shows an example of the configuration of the wrapper during the WS_PRELOAD instruction. 7.10 WP_PRELOAD instruction The WP_PRELOAD instruction enables the wrapper to be functionally configured. Wrappers that have a WBR composed entirely of cells with a silent shift path and have parallel instruction capability, may include the WP_PRELOAD instruction. The WP_PRELOAD instruction allows data values to be loaded into the latched parallel outputs of the registers in the silent shift path(s) of the WBR. The data are loaded into the silent shift paths of wrapper cells, and then the data are loaded into the update stage, if present, during the Update operation. This instruction would typically be utilized before other defined instructions are selected (e.g., WP_EXTEST). The WP_PRELOAD instruction allows the WBR to be divided into segments (multiple scan chains), and may be preferred over the WS_PRELOAD instruction before entering the WP_EXTEST instruction. It also allows wrapper inputs and outputs, other than the WSP, to control WBR inputs and observe WBR outputs. In all other behaviors, WP_PRELOAD mimics the WS_PRELOAD instruction.

这段内容主要介绍了两种预加载指令 WS_PRELOAD 和 WP_PRELOAD。

WS_PRELOAD 指令用于在不干扰核心或连接到 Wrapper Boundary Register(WBR)的用户定义逻辑(UDL)操作的情况下,通过 WBR 的移位实现从 Wrapper Scan In(WSI)到 Wrapper Scan Out(WSO)的移位。它允许通过扫描加载操作将初始数据模式放置在静默移位路径寄存器单元的锁存并行输出上。例如,在选择 WS_EXTEST 指令之前,可以使用 WS_PRELOAD 将数据加载到锁存并行输出上。一旦 WS_EXTEST 指令被传输到指令寄存器的更新寄存器,预加载的数据就从 Wrapper Functional Outputs(WFOs)驱动。这样可以确保在进入 WS_EXTEST 指令时立即驱动已知数据。如果没有 WS_PRELOAD,在第一次扫描加载完成之前可能会驱动不确定的数据。图 6 展示了在 WS_PRELOAD 指令期间包装器的配置示例。

WP_PRELOAD 指令用于对包装器进行功能配置。具有完全由带有静默移位路径的单元组成的 WBR 并且具有并行指令能力的包装器可以包括 WP_PRELOAD 指令。该指令允许将数据值加载到 WBR 的静默移位路径中的寄存器的锁存并行输出上。数据被加载到包装器单元的静默移位路径中,然后在更新操作期间(如果存在更新阶段)被加载到更新阶段。此指令通常在选择其他定义的指令(例如 WP_EXTEST)之前使用。WP_PRELOAD 指令允许将 WBR 分为多个段(多个扫描链),并且在进入 WP_EXTEST 指令之前可能比 WS_PRELOAD 指令更受青睐。它还允许除 WSP 之外的包装器输入和输出控制 WBR 输入并观察 WBR 输出。在所有其他行为方面,WP_PRELOAD 模仿 WS_PRELOAD 指令。

7.10.1 Specifications Rules a) While the WP_PRELOAD instruction is selected, only the WBR shall be connected during the Shift operation (i.e., no other test data register may be connected in series with the WBR). b) While the WP_PRELOAD instruction is selected, the data in the wrapper boundary cell shall be available for the Update operation, if applicable. c) While the WS_PRELOAD instruction is selected, the Shift operation of the WBR shall have no effect on the operation of the core or UDL. d) While the WP_PRELOAD instruction is selected, the WPC shall be utilized for test control. Recommendations e) While the WP_PRELOAD instruction is selected, if the core is not being used in its normal operation, the core circuitry should be put into a quiet mode (e.g., reset or clock off). Permissions f) The WBR may be segmented into one or more scan chains with the input and output port of the scan chains interfaced to the TAM. g) The binary code for the WP_PRELOAD instruction may be selected by the wrapper designer. 7.10.2 Description The WP_PRELOAD instruction is used to allow shifting of the WBR without causing interference to the operation of the core or UDL attached to the WBR. WP_PRELOAD allows an initial data pattern to be placed at the latched parallel outputs of the silent shift path register cells through a scan load operation. For example, prior to selection of the WP_EXTEST instruction, data can be loaded onto the latched parallel outputs using WP_PRELOAD. As soon as the WP_EXTEST instruction has been transferred to the parallel output of the instruction register, the preloaded data are driven from the output wrapper terminals.

- “Specifications/Rules” 部分:

- 当选择 WP_PRELOAD 指令时,在移位操作期间只有边界寄存器(WBR)应被连接,即不能有其他测试数据寄存器与 WBR 串联。

- 当选择 WP_PRELOAD 指令时,包装器边界单元中的数据在适用的情况下应可用于更新操作。

- 当选择 WS_PRELOAD 指令时,WBR 的移位操作对内核或用户定义逻辑(UDL)的操作不应产生影响。

- 当选择 WP_PRELOAD 指令时,应使用包装器端口控制器(WPC)进行测试控制。

- “Specifications/Recommendations” 部分:

- 当选择 WP_PRELOAD 指令时,如果内核在正常操作中未被使用,内核电路应置于安静模式(例如,复位或关闭时钟)。

- “Specifications/Permissions” 部分:

- WBR 可以被分割成一个或多个扫描链,扫描链的输入和输出端口与测试访问机制(TAM)接口。

- WP_PRELOAD 指令的二进制代码可以由包装器设计者选择。

- “Description” 部分:

- WP_PRELOAD 指令用于允许 WBR 的移位而不会对连接到 WBR 的内核或 UDL 的操作造成干扰。WP_PRELOAD 允许通过扫描加载操作将初始数据模式放置在无声移位路径寄存器单元的锁存并行输出上。例如,在选择 WP_EXTEST 指令之前,可以使用 WP_PRELOAD 将数据加载到锁存并行输出上。一旦 WP_EXTEST 指令已传输到指令寄存器的并行输出,预加载的数据将从输出包装器端子驱动。

ensures that known data are driven immediately when the WP_EXTEST instruction is entered. Without WP_PRELOAD, indeterminate data may be driven until the first scan load is complete. Figure 7 shows an example of the configuration of the wrapper during the WP_PRELOAD instruction.

确保在输入 WP_EXTEST 指令时立即驱动已知数据。如果没有 WP_PRELOAD,在第一次扫描加载完成之前可能会驱动不确定的数据。图 7 展示了在 WP_PRELOAD 指令期间包装器的配置示例。

- WP_PRELOAD 指令用于允许 WBR 的移位而不会对连接到 WBR 的内核或 UDL 的操作造成干扰。WP_PRELOAD 允许通过扫描加载操作将初始数据模式放置在无声移位路径寄存器单元的锁存并行输出上。例如,在选择 WP_EXTEST 指令之前,可以使用 WP_PRELOAD 将数据加载到锁存并行输出上。一旦 WP_EXTEST 指令已传输到指令寄存器的并行输出,预加载的数据将从输出包装器端子驱动。

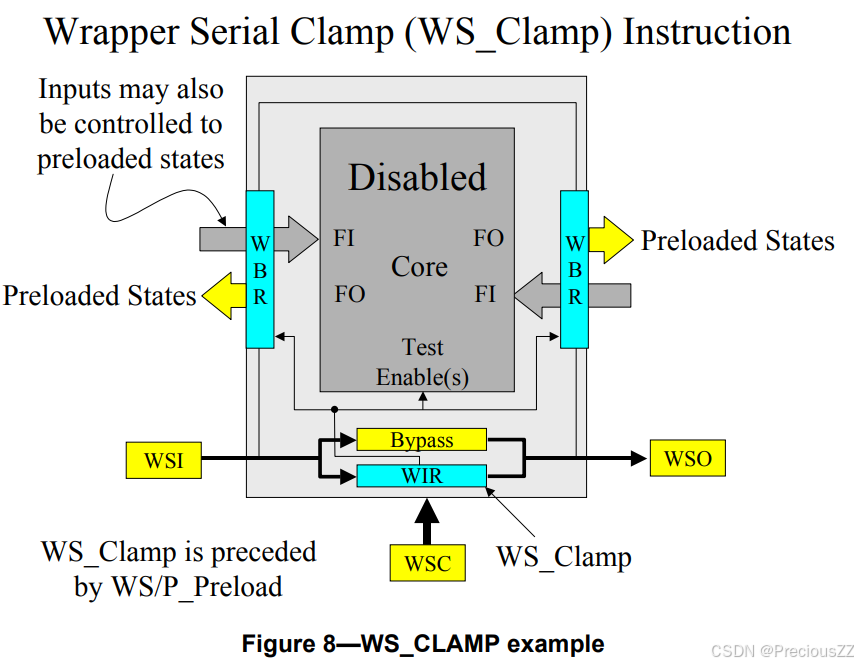

7.11 WS_CLAMP instruction The optional WS_CLAMP instruction allows the state of the signals driven from WFOs to be determined from the WBR while the WBY is selected as the serial path between WSI and WSO. The signals driven from the WFOs will not change while the WS_CLAMP instruction is selected. The rules in 7.11.1 apply where the WS_CLAMP instruction is provided. NOTE—Following use of the WS_CLAMP instruction, the core circuitry may be in an indeterminate state that will persist until a system reset is applied. Therefore, the core circuitry may need to be reset on return to normal (i.e., nontest) operation. 7.11.1 Specifications Rules a) While the WS_CLAMP instruction is selected, the WBY shall be connected for serial access between WSI and WSO. b) While the WS_CLAMP instruction is selected, the state of all signals driven from WFOs shall be completely defined by the data held in the WBR. NOTE—Data held in the WBR might be achieved by the previous use of an instruction (e.g., WS_PRELOAD). c) While the WS_CLAMP instruction is selected, the WSC shall be utilized for test control.

7.11 WS_CLAMP 指令:可选的 WS_CLAMP 指令允许在选择 WBY 作为 WSI 和 WSO 之间的串行路径时,根据 WBR 确定从 WFO 驱动的信号状态。在选择 WS_CLAMP 指令时,从 WFO 驱动的信号不会改变。如果提供了 WS_CLAMP 指令,则适用 7.11.1 中的规则。注意:在使用 WS_CLAMP 指令后,核心电路可能处于不确定状态,这种状态将持续到应用系统复位为止。因此,在恢复正常(即非测试)操作时,核心电路可能需要复位。7.11.1 规范:规则如下:a)在选择 WS_CLAMP 指令时,WBY 应连接以在 WSI 和 WSO 之间进行串行访问。b)在选择 WS_CLAMP 指令时,从 WFO 驱动的所有信号的状态应完全由 WBR 中保存的数据定义。注意:WBR 中保存的数据可能通过先前使用的指令(例如 WS_PRELOAD)实现。c)在选择 WS_CLAMP 指令时,WSC 应用于测试控制。

“Recommendations” 意为 “建议”。

“d) While the WS_CLAMP instruction is selected, the core circuitry should be put into a quiet mode (e.g., reset or clock off).” 这句话的意思是:当选择 WS_CLAMP 指令时,核心电路应置于安静模式(例如,复位或关闭时钟)。

“Permissions” 意为 “权限”。

“e) The binary code for the WS_CLAMP instruction may be selected by the wrapper designer.” 这句话的意思是:WS_CLAMP 指令的二进制代码可以由封装设计者选择。

“Description” 意为 “描述”。

“During testing of a particular core or cluster of cores on a system chip, it may be necessary to place static values on signals that control operation of circuitry not involved in the test, e.g., to place the aforementioned circuitry in a state where it cannot respond to signals received from the circuitry under test.” 这句话的意思是:在对系统芯片上的特定核心或核心集群进行测试期间,可能有必要在控制不参与测试的电路操作的信号上放置静态值,例如,将上述电路置于一种不能响应来自被测电路接收的信号的状态。

“The optional WS_CLAMP instruction allows static values to be applied using the WBRs of the appropriate core wrapper, but does not retain these registers in the serial path during test application.” 这句话的意思是:可选的 WS_CLAMP 指令允许使用适当的核心封装的 WBR(可能是某种寄存器)来应用静态值,但在测试应用期间不会在串行路径中保留这些寄存器。

“In a case in which the WS_CLAMP instruction is used to create static values, the following processes would be used.” 这句话的意思是:在使用 WS_CLAMP 指令创建静态值的情况下,将使用以下过程。

“It is presumed in the following example that every wrapper implements the optional WS_CLAMP instruction.” 这句话的意思是:在以下示例中假定每个封装都实现了可选的 WS_CLAMP 指令。

Example: WBRs having dedicated wrapper boundary cells — Prior to the test, a Wx_EXTEST or Wx_PRELOAD (the x denotes S, P, or H) instruction would be loaded into all core wrappers that will provide specific values during the upcoming test. Call this group of wrappers G. If test setup data are required in wrappers not in G (i.e., in the wrappers that will participate actively in the upcoming test), a Wx_EXTEST or Wx_PRELOAD instruction may be loaded into these core wrappers simultaneously with the loading of WS_CLAMP into core group G. — Shift the desired pattern into all relevant wrapper boundary cells of the wrappers in G. Any test setup data required for the SoC to be tested are also loaded. — Load WS_CLAMP instruction into the wrappers in G. — From this point on, until the test is concluded, every time instructions are to be scanned into core wrappers in the SoC, enter the WS_CLAMP instruction into the wrappers in G. As long as the WS_CLAMP instruction is maintained as the active instruction in the wrappers of G, the output signal values of these wrappers will be determined by the data in their WBRs. Also, as a consequence of the use of the WS_CLAMP instruction, the wrappers in G all have their WBYs selected throughout the test; thus, they contribute very little to the overall test time. Figure 8 shows an example of the configuration of the wrapper during the WS_CLAMP instruction. This instruction would be loaded serially into the core wrappers that drive the signals on which static values are required. The required signal values could be loaded as a part of the complete serial data stream shifted into the chip-level WBR path, both at the start of the test and each time a new test pattern is entered. However, a limitation of this approach is that the length of the data pattern to be shifted for each test is increased by inclusion of the WBR of each core wrapper involved in the process. As a result, the test application rate is reduced. WS_CLAMP reduces overall shift length when the target wrapper does not take an active part in the test. Note that this is just one example of how to clamp a signal. Instructions such as Wx_PRELOAD or Wx_EXTEST can be used to load specific values into the wrapper before WS_CLAMP is enabled.

这段文本主要描述了在集成电路测试中对 WBR(Wrapper Boundary Register,封装边界寄存器)的操作流程及相关注意事项。

首先,在测试前,将特定指令加载到一些核心封装中(称为 G 组)以提供特定值。如果其他不在 G 组但在即将进行的测试中需要测试设置数据的封装,可同时加载特定指令和 WS_CLAMP 到核心组 G。

接着,将所需模式移入 G 组封装的所有相关封装边界单元,并加载 SoC(片上系统)测试所需的任何测试设置数据。然后将 WS_CLAMP 指令加载到 G 组封装中,从此时起直到测试结束,每次要将指令扫描到 SoC 的核心封装中时,都要将 WS_CLAMP 指令输入到 G 组封装中。只要 WS_CLAMP 指令在 G 组封装中保持为活动指令,这些封装的输出信号值将由其 WBR 中的数据决定。并且由于使用了 WS_CLAMP 指令,G 组中的封装在整个测试过程中都选择了 WBY,因此它们对整体测试时间的贡献很小。

图 8 展示了在 WS_CLAMP 指令期间封装的配置示例。该指令将被串行加载到驱动需要静态值信号的核心封装中。所需的信号值可以作为在测试开始时以及每次输入新测试模式时移入芯片级 WBR 路径的完整串行数据流的一部分加载。但是,这种方法的一个限制是,由于每个参与该过程的核心封装的 WBR 都包含在内,每次测试要移位的数据模式的长度增加了,从而降低了测试应用速率。当目标封装在测试中不积极参与时,WS_CLAMP 可减少整体移位长度。

最后提到这只是夹紧信号的一个示例,在启用 WS_CLAMP 之前,可以使用诸如 Wx_PRELOAD 或 Wx_EXTEST 之类的指令将特定值加载到封装中。

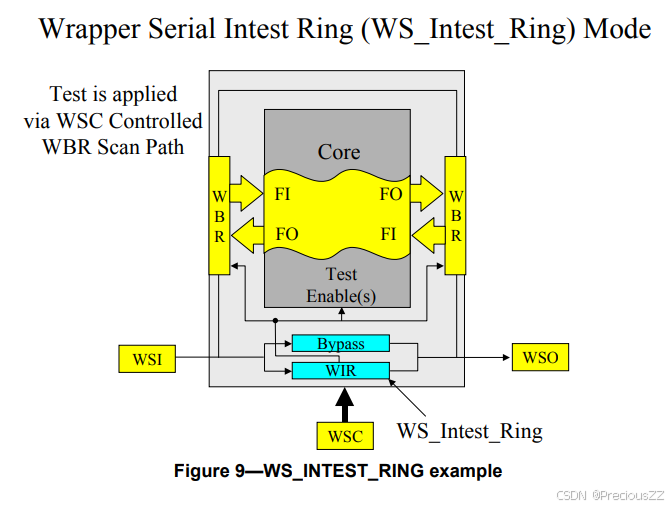

7.12 WS_INTEST_RING instruction The optional serial wrapper core test WS_INTEST_RING instruction allows testing of the core circuitry. During the WS_INTEST_RING instruction, test stimuli are shifted in 1 bit at a time and applied to the core functional terminals via the WBR only. The test results are captured into the WBR and are shifted out 1 bit at a time for examination. The rules in 7.12.1 apply where the WS_INTEST_RING instruction is provided. NOTE—Following the use of the WS_INTEST_RING instruction, the core circuitry may be in an indeterminate state that will persist until a core reset is applied. Therefore, the core circuitry may need to be reset on return to normal operation. 7.12.1 Specifications Rules a) The WS_INTEST_RING instruction shall select only the WBR to be connected for serial access between WSI and WSO (i.e., no other test data register may be connected in series with the WBR). b) While the WS_INTEST_RING instruction is selected, the WBR shall be in IF mode. c) While the WS_INTEST_RING instruction is selected, the WSC shall be utilized for test control. Recommendations d) While the WS_INTEST_RING instruction is selected, all WFOs should be placed in a safe or static drive state. e) While the WS_INTEST_RING instruction is selected, for core input terminals provisioned with wrapper boundary cells per rule 12.1.1(a), the data loaded during the Capture event should be independent of the operation of off-core circuitry or chip-level interconnections. Permissions f) The binary code for the WS_INTEST_RING instruction may be selected by the wrapper designer.

7.12 WS_INTEST_RING 指令是一种可选的串行包装器核心测试指令,它允许对核心电路进行测试。在 WS_INTEST_RING 指令执行期间,测试激励每次一位地移入,并通过 WBR(Wrapper Boundary Register,包装器边界寄存器)仅应用于核心功能终端。测试结果被捕获到 WBR 中,并每次一位地移出以供检查。如果提供了 WS_INTEST_RING 指令,则适用 7.12.1 中的规则。注意,在使用 WS_INTEST_RING 指令后,核心电路可能处于不确定状态,这种状态将持续到应用核心复位为止。因此,在恢复正常操作时,核心电路可能需要复位。

7.12.1 具体规则如下:

规则 a)WS_INTEST_RING 指令应仅选择 WBR 以便在 WSI(Wrapper Serial Input,包装器串行输入)和 WSO(Wrapper Serial Output,包装器串行输出)之间进行串行访问(即,不可以有其他测试数据寄存器与 WBR 串联连接)。

规则 b)当选择 WS_INTEST_RING 指令时,WBR 应处于 IF 模式。

规则 c)当选择 WS_INTEST_RING 指令时,WSC(Wrapper Serial Control,包装器串行控制)应用于测试控制。

建议 d)当选择 WS_INTEST_RING 指令时,所有 WFO(Wrapper Functional Output,包装器功能输出)应置于安全或静态驱动状态。

建议 e)当选择 WS_INTEST_RING 指令时,对于按照规则 12.1.1 (a) 配备了包装器边界单元的核心输入终端,在捕获事件期间加载的数据应独立于片外电路或芯片级互连的操作。

权限 f)WS_INTEST_RING 指令的二进制代码可以由包装器设计者选择。

7.12.2 Description The WS_INTEST_RING instruction allows single-step testing of core circuitry with each test pattern and response being shifted through the WBR. The WS_INTEST_RING instruction requires that the core circuitry can be operated in a single-step mode, where the circuitry moves one step forward in its operation each time shifting of the WBR is completed. While the WS_INTEST_RING instruction is selected, the WBR assumes the role of virtual test points. Cells at nonclock core input terminals are used to apply the test stimulus, while those at core output terminals capture the response. Stimuli and responses are moved into and out of the circuit by shifting through the WBR. Note that this requires that the core input terminals provisioned with wrapper boundary cells per rule 12.1.1(a) are able to drive signals into the core circuitry. Typically, the core circuitry will receive a sequence of clock events between application of the stimulus and capture of the response so that single-step operation is achieved. The specification of wrapper boundary cells for core clock input terminals allows the clocks for the core circuitry to be obtained in several ways while the WS_INTEST_RING instruction is selected. The following are offered as examples: a) The signals received at core clock terminals can be fed directly to the core circuitry as during normal operation of the core. Where this option is selected, the core design shall guarantee that precisely one single step of operation of the core circuitry occurs between each shifting (filling) of the WBR. b) Circuitry may be built into the core that allows the core circuitry to complete one step of operation on completion of shifting in data into the WBR. If the core were a microprocessor, it would be permitted to complete a single processing cycle by, for example, internal generation of a pulse on the hold signal. In this case, the clock(s) applied at the core clock terminal(s) during the test could be free-running. While the WS_INTEST_RING instruction is selected, the state of all WFOs is determined by the wrapper circuitry. Every WFO should be forced to a static or inactive drive state. This ensures that surrounding circuitry on an SoC is supplied known, safe signal levels while the core circuitry test is in progress. Recommendation 7.12.1(e), where followed, ensures that data shifted out of the core in response to the WS_INTEST_RING instruction are not altered by the presence of defects in off-core circuitry, chip-level interconnections, etc. This simplifies diagnosis, since any errors in the output bit stream can be caused only by defects in the core circuitry or in the WBR. Figure 9 shows an example of the configuration of the wrapper during the WS_INTEST_RING instruction.

这段文本主要介绍了 WS_INTEST_RING 指令的功能和特点,以及在使用该指令时核心电路和封装电路的一些要求和操作方式。

- WS_INTEST_RING 指令允许通过每个测试模式对核心电路进行单步测试,测试模式和响应通过 WBR(Wrapper Boundary Register,封装边界寄存器)移位。该指令要求核心电路能够在单步模式下运行,即每次 WBR 移位完成时,电路在其操作中向前推进一步。

- 当选择 WS_INTEST_RING 指令时,WBR 充当虚拟测试点。非时钟核心输入终端的单元用于施加测试激励,而核心输出终端的单元捕获响应。激励和响应通过在 WBR 中移位进出电路。这要求按照规则 12.1.1 (a) 为核心输入终端配备封装边界单元的核心输入终端能够将信号驱动到核心电路中。

- 通常,在施加激励和捕获响应之间,核心电路将接收一系列时钟事件,以实现单步操作。为核心时钟输入终端指定封装边界单元允许在选择 WS_INTEST_RING 指令时以多种方式获得核心电路的时钟。例如:

- 可以直接将核心时钟终端接收的信号馈送到核心电路,就像核心正常运行时一样。在选择此选项时,核心设计应确保在每次 WBR 移位(填充)之间恰好发生核心电路的一个单步操作。

- 可以在核心中构建电路,使得在将数据移入 WBR 完成时,核心电路完成一个操作步骤。如果核心是微处理器,可以通过例如在保持信号上内部生成脉冲来完成单个处理周期。在这种情况下,测试期间应用于核心时钟终端的时钟可以自由运行。

- 当选择 WS_INTEST_RING 指令时,所有 WFO(Wrapper Functional Output,封装功能输出)的状态由封装电路确定。每个 WFO 应被强制为静态或非活动驱动状态。这确保了在核心电路测试进行时,SoC 上的周围电路被提供已知的、安全的信号电平。

- 遵循建议 7.12.1 (e),可确保响应 WS_INTEST_RING 指令从核心移出的数据不会因片外电路、芯片级互连等中的缺陷而改变。这简化了诊断,因为输出位流中的任何错误只能由核心电路或 WBR 中的缺陷引起。图 9 显示了在 WS_INTEST_RING 指令期间封装的配置示例。

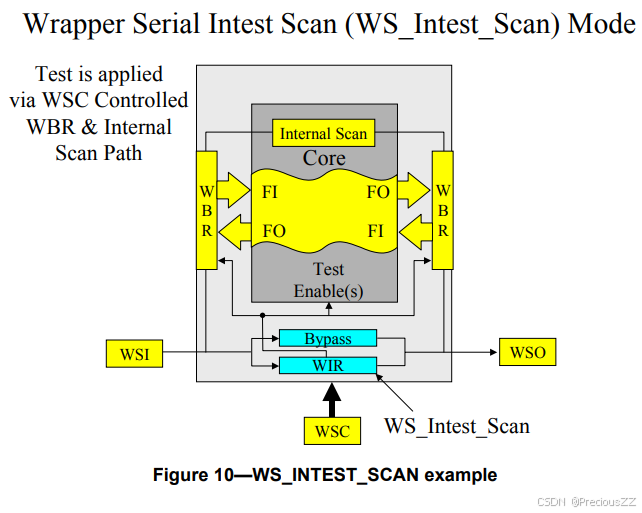

7.13.1 Specifications Rules a) While the WS_INTEST_SCAN instruction is selected, the WBR concatenated with an internal scan chain, which includes all internal scan cells, shall be connected for serial access between WSI and WSO. b) While the WS_INTEST_SCAN instruction is selected, the WBR shall be in IF mode. c) While the WS_INTEST_SCAN instruction is selected, the WSC shall be utilized for test control. Recommendations d) While the WS_INTEST_SCAN instruction is selected, all WFOs should be placed in a safe or static drive state. e) While the WS_INTEST_SCAN instruction is selected, for core input terminals provisioned with wrapper boundary cells per rule 12.1.1(a), the data loaded during the Capture event should be independent of the operation of off-core circuitry or chip-level interconnections. f) The serial scan chain should comprise the WBR and every scanned element in the core. Permissions g) The binary code for the WS_INTEST_SCAN instruction may be selected by the wrapper designer.

这段内容是关于某种技术规范的说明,具体涉及到特定指令 “WS_INTEST_SCAN” 被选中时的各种规则、建议和权限。

规则部分:

- 当 “WS_INTEST_SCAN” 指令被选中时,WBR 与包括所有内部扫描单元的内部扫描链连接,在 WSI 和 WSO 之间进行串行访问。

- 此时 WBR 应处于 IF 模式。

- WSC 应被用于测试控制。

建议部分:

- 当 “WS_INTEST_SCAN” 指令被选中时,所有 WFO 应处于安全或静态驱动状态。

- 对于按照规则 12.1.1 (a) 配备包装边界单元的核心输入终端,在捕获事件期间加载的数据应独立于芯片外部电路或芯片级互连的操作。

权限部分:

- “WS_INTEST_SCAN” 指令的二进制代码可以由包装设计者选择。

7.13.2 Description The WS_INTEST_SCAN instruction allows single-step testing of core circuitry with each test pattern and response being shifted through the serial scan chain. While the WS_INTEST_SCAN instruction is selected, the serial scan chain assumes the role of virtual test points. Cells at nonclock core input terminals are used to apply the test stimulus, while those at core output terminals capture the response. Stimuli and responses are moved into and out of the circuit by shifting the

“7.13.2 描述:WS_INTEST_SCAN 指令允许使用每个测试模式对核心电路进行单步测试,并且响应通过串行扫描链进行移位。当选择 WS_INTEST_SCAN 指令时,串行扫描链承担虚拟测试点的角色。位于非时钟核心输入终端的单元用于施加测试激励,而位于核心输出终端的单元捕获响应。通过移位将激励和响应移入和移出电路。”

serial scan chain. This operation requires that the core input terminals provisioned with wrapper boundary cells per rule 12.1.1(a) are able to drive signals into the core circuitry. Typically, the core circuitry will receive a sequence of clock events between application of the stimulus and capture of the response so that single-step operation is achieved. The specification of wrapper boundary cells for core clock input terminals allows the clocks for the core circuitry to be obtained in several ways while the WS_INTEST_SCAN instruction is selected. The following are offered as examples: a) The signals received at core clock terminals can be fed directly to the core circuitry as during normal operation of the core. Where this option is selected, the core design shall guarantee that precisely one single step of operation of the core circuitry occurs between each shifting (filling) of the serial scan chain. b) Circuitry may be built into the core that allows the core circuitry to complete one step of operation on completion of shifting in data into the serial scan chain. If the core were a microprocessor, it would be permitted to complete a single processing cycle by, for example, internal generation of a pulse on a hold signal. In this case, the clock(s) applied at the core clock terminal(s) during the test could be free-running. While the WS_INTEST_SCAN instruction is selected, the state of all WFOs is determined by the wrapper circuitry. Every WFO should be forced to a static or inactive drive state. This ensures that surrounding circuitry on an SoC is supplied known, safe signal levels while the core circuitry test is in progress. Recommendation 7.13.1(e), where followed, ensures that data shifted out of the core in response to the WS_INTEST_SCAN instruction are not altered by the presence of defects in off-core circuitry, chip-level interconnections, etc. This simplifies diagnosis, since any errors in the output bit stream can be caused only by defects in the core circuitry or in the WBR. Figure 10 shows an example of the configuration of the wrapper during the WS_INTEST_SCAN instruction.

这段文本主要描述了关于串行扫描链以及在特定指令下的核心电路和封装电路的相关要求和操作。

首先提到了串行扫描链的操作要求核心输入终端按照规则配备封装边界单元,并且核心电路在施加激励和捕获响应之间通常会接收一系列时钟事件以实现单步操作。对于核心时钟输入终端的封装边界单元的规范允许以多种方式获得核心电路的时钟,例如:a)核心时钟终端接收的信号可以像核心正常操作时一样直接馈送到核心电路,并且核心设计要保证在串行扫描链每次移位填充之间恰好发生核心电路的一个单步操作;b)可以在核心中构建电路,使得在数据移入串行扫描链完成后,核心电路完成一个操作步骤,例如微处理器可以通过在保持信号上内部生成脉冲来完成一个处理周期,此时测试期间核心时钟终端的时钟可以自由运行。

接着指出在选择 “WS_INTEST_SCAN” 指令时,所有的 WFO(wrapper force output,封装强制输出)状态由封装电路决定,每个 WFO 应被强制为静态或非活动驱动状态,以确保在核心电路测试进行时,SoC 上的周围电路获得已知的安全信号电平。遵循建议 7.13.1 (e) 可以确保响应 “WS_INTEST_SCAN” 指令从核心移出的数据不会因片外电路、芯片级互连等中的缺陷而改变,这简化了诊断,因为输出位流中的任何错误只能由核心电路或 WBR(wrapper boundary register,封装边界寄存器)中的缺陷引起。最后提到图 10 展示了在 “WS_INTEST_SCAN” 指令期间封装的配置示例。

7.14 Wx_INTEST instruction One core test instruction that allows the core to be tested according to a test procedure specified by the core provider or core user is required. IEEE Std 1500 does not describe how to test individual cores; this is the responsibility of the core provider. The core test invoked by the Wx_INTEST instruction (the x in Wx is a place holder for an S, P, or H to indicate whether the instruction is serial, parallel, or hybrid) is completely specified with the CTL provided for the core. The Wx_INTEST CTL describes the attributes of the core test such as the following: a) Number of cell test input (CTI) and cell test output (CTO) terminals, b) Test pattern set, including control and/or data, that is applied to the core via associated TI and TO terminals,

c) Protocol used to input and output the test patterns,

d) Condition or state of core input and output terminals during the core test, excluding the TI and TO terminals, and

e) Whether the WBR is used during the core test, and if used, in what configuration it is placed. The Wx_INTEST instruction encompasses the WS_INTEST_RING and the WS_INTEST_SCAN instruction. The rules in 7.14.1 apply for the Wx_INTEST instruction.

7.14 Wx_INTEST 指令是一种核心测试指令,要求有一个能让核心按照核心提供者或核心用户指定的测试程序进行测试的指令。IEEE Std 1500 没有描述如何测试单个核心,这是核心提供者的责任。由 Wx_INTEST 指令调用的核心测试(Wx 中的 x 是占位符,可以是 S、P 或 H,分别表示该指令是串行、并行或混合的)完全由为核心提供的 CTL 来指定。Wx_INTEST 的 CTL 描述了核心测试的属性,例如:

a)单元测试输入(CTI)和单元测试输出(CTO)终端的数量;

b)通过相关的 TI 和 TO 终端应用于核心的测试模式集,包括控制和 / 或数据;

c)用于输入和输出测试模式的协议;

d)在核心测试期间核心输入和输出终端的条件或状态,不包括 TI 和 TO 终端;

e)在核心测试期间是否使用 WBR,如果使用,它以何种配置放置。Wx_INTEST 指令包括 WS_INTEST_RING 和 WS_INTEST_SCAN 指令。7.14.1 中的规则适用于 Wx_INTEST 指令。

7.14.1 Specifications Rules

a) Each wrapper shall provide at least one Wx_INTEST instruction.

b) While the Wx_INTEST instruction is selected, the WBR shall be in IF mode. Recommendations

c) While the Wx_INTEST instruction is selected, the operation of the core should not disturb circuitry external to the core. d) While the Wx_INTEST instruction is selected, all WFOs should be placed in a safe or static drive state. e) While the Wx_INTEST instruction is selected, for core input terminals provisioned with wrapper boundary cells per rule 12.1.1(a), the data loaded during the Capture event should be independent of the operation of off-core circuitry or chip-level interconnections. Permissions f) The WBR may be segmented into one or more scan chains with the input and output port of the scan chains interfaced to the TAM.

g) The binary code for the Wx_INTEST instruction may be selected by the wrapper designer.

h) Any number of Wx_INTEST instructions (Wx_INTEST_user_defined)) may be included by the wrapper designer.

这是关于某种技术规范的内容。

具体来说,规则部分:

a)每个包装器应至少提供一个 Wx_INTEST 指令;

b)当选择 Wx_INTEST 指令时,WBR 应处于 IF 模式。

建议部分:

c)当选择 Wx_INTEST 指令时,核心的操作不应干扰核心外部的电路;d)当选择 Wx_INTEST 指令时,所有 WFO 应置于安全或静态驱动状态;

e)当选择 Wx_INTEST 指令时,对于按照规则 12.1.1 (a) 配备包装器边界单元的核心输入终端,在捕获事件期间加载的数据应独立于核心外部电路或芯片级互连的操作。

权限部分:

f)WBR 可以分割成一个或多个扫描链,扫描链的输入和输出端口与 TAM 接口;

g)Wx_INTEST 指令的二进制代码可以由包装器设计者选择;

h)包装器设计者可以包含任意数量的 Wx_INTEST 指令(Wx_INTEST_user_defined)。

7.14.2 Description The Wx_INTEST instruction allows testing of core circuitry. While the Wx_INTEST instruction is selected, the WBR may participate and assume the role of virtual test points. Cells at nonclock core input terminals are used to apply the test stimulus, while those at core output terminals capture the response. Stimuli and responses are moved into and out of the circuit by shifting the

Wx_INTEST 指令允许对核心电路进行测试。当选择 Wx_INTEST 指令时,WBR 可以参与并承担虚拟测试点的角色。位于非时钟核心输入终端的单元用于施加测试激励,而位于核心输出终端的单元捕获响应。通过移位将激励和响应移入和移出电路。

WBR. Note that this requires that the core input terminals provisioned with wrapper boundary cells per rule 12.1.1(a) are able to drive signals into the core circuitry. Typically, the core circuitry will receive a sequence of one or more clock events between application of the stimulus and capture of the response. The specification of wrapper boundary cells for core clock input terminals allows the clocks for the core circuitry to be received in several ways while the Wx_INTEST instruction is selected. The following are offered as examples: a) The signals received at core clock terminals can be fed directly to the core circuitry as during normal operation of the core. b) Circuitry may be built into the core that allows the core circuitry to complete one step of operation on completion of shifting in data into the WBR. If the core were a microprocessor, it would be permitted to complete a single processing cycle by, for example, internal generation of a pulse on the hold signal. In this case, the clock(s) applied at the core clock terminal(s) during the test could be free-running. While the Wx_INTEST instruction is selected, the state of all WFOs is determined by the wrapper circuitry. Every WFO should be forced to a static or inactive drive state. This ensures that surrounding circuitry on an SoC are supplied known, safe signal levels while the core circuitry test is in progress. Recommendation 7.14.1(e), where followed, ensures that data shifted out of the core in response to the Wx_INTEST instruction are not altered by the presence of defects in off-core circuitry, chip-level interconnections, etc. This simplifies diagnosis, since any errors in the output bit stream can be caused only by defects in the core circuitry or in the WBR.

这段文本主要是关于芯片测试的规则和要求说明。首先提到 WBR 需要按照规则 12.1.1 (a),核心输入端子配备包装边界单元,以便能够将信号驱动到核心电路中。通常在施加激励和捕获响应之间,核心电路会接收一个或多个时钟事件序列。对于核心时钟输入端子的包装边界单元的规范允许在选择 Wx_INTEST 指令时以多种方式接收核心电路的时钟。接着举例说明了两种方式:一是在核心正常操作期间,核心时钟端子接收的信号可以直接馈送到核心电路;二是可以在核心中构建电路,使得在将数据移入 WBR 完成后,核心电路完成一步操作,例如通过在保持信号上内部生成脉冲,如果核心是微处理器,在测试期间应用于核心时钟端子的时钟可以是自由运行的。当选择 Wx_INTEST 指令时,所有 WFO 的状态由包装电路决定,每个 WFO 应被强制为静态或非活动驱动状态,以确保在核心电路测试进行时,SoC 上的周围电路被提供已知的安全信号电平。遵循建议 7.14.1 (e) 可确保响应 Wx_INTEST 指令从核心移出的数据不会因芯片外电路、芯片级互连等中的缺陷而改变,这简化了诊断,因为输出位流中的任何错误只能由核心电路或 WBR 中的缺陷引起。

6132

6132

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?