本文的主要内容是分析S32K144的时钟系统并验证配置的正确性。由于S32K144的时钟系统与电源管理系统相互有很多牵连,所以本篇只讨论时钟的基本配置,有关于时钟与模式切换的内容在后续文章中讨论。

1.S32K144的系统时钟分析

1.1 时钟模块总览

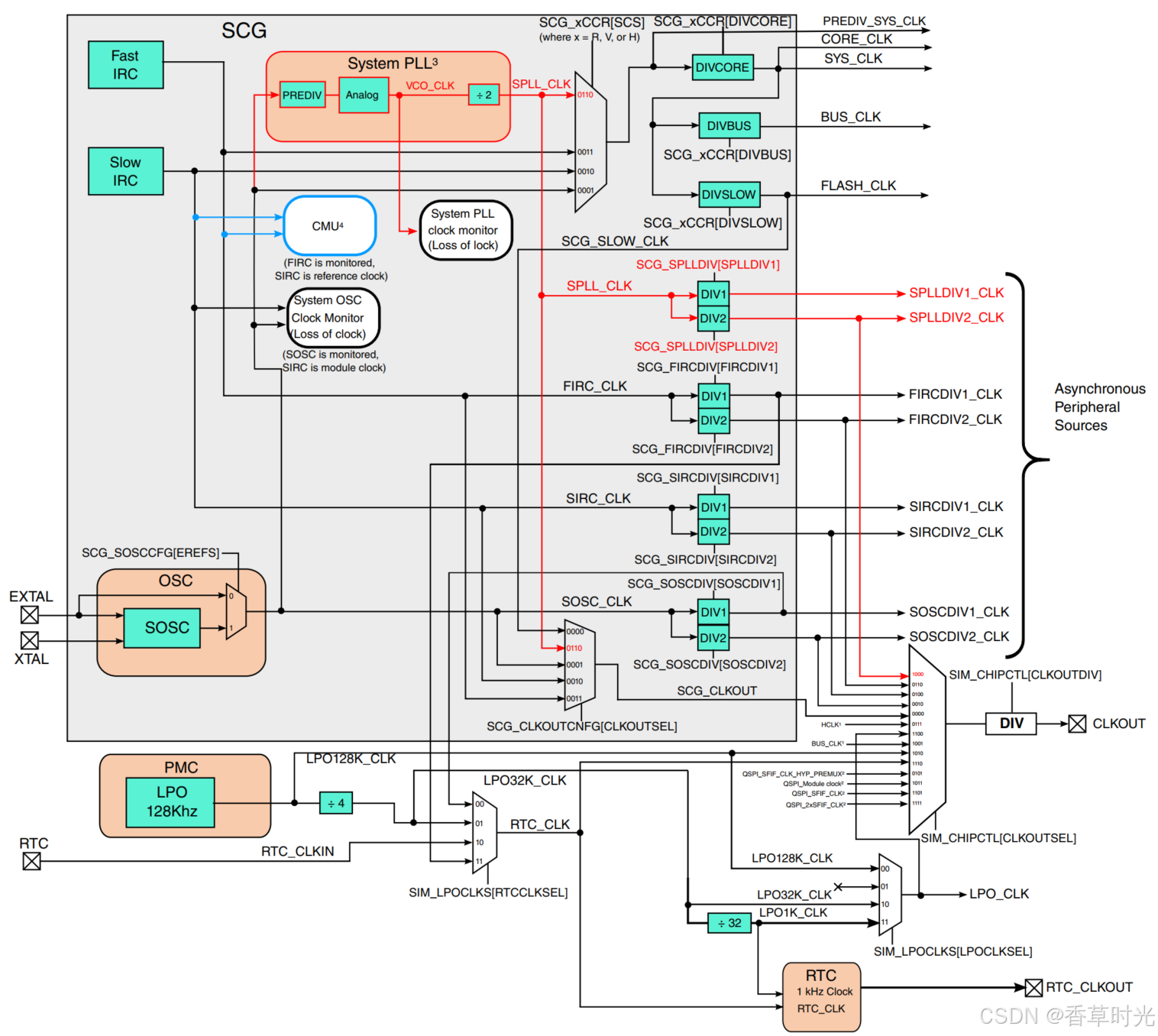

首先根据S32K144的用户参考手册中的描述,贴出芯片的时钟架构,其中时钟的配置的主要模块是SCG,如下图。

从图中可以看出,S32K144的系统时钟架构还是比较清晰的,片上自带三个内部时钟源:Fast IRC、Slow IRC以及LPO;当然也可以使用两个外部时钟源:EXTAL(外部时钟输入或晶振振荡器)、RTC(外部时钟)。内核、系统、外设时钟及可以来源于外部时钟源、内部时钟源或者锁相环(SPLL),此外,时钟系统有两个输出I/O:CLKOUT和RTC_CLKOUT(这两个引脚不但可以向外提供时钟基准还可以测试时钟输出是否正确和稳定,本文将利用这个引脚输出来进行时钟配置验证)。

时钟系统还是比较灵活的(笔者没有使用过ST的Cortex-M4的芯片,不知道两者有多大区别,与国产的雅特力的Cortex-M4的AT32F4系列相比差别还是很大的)。

1.2 时钟定义说明

| 时钟名称 | 描述 |

|---|---|

| PREDIV_SYS_CLK | 在HSRUN 80模式下为QSPI存储器提供时钟 |

| CORE_CLK | 内核时钟 |

| SYS_CLK | 为Crossbar、NVIC、Flash控制器、FTM、PDB等提供时钟 |

| BUS_CLK | 外设时钟 |

| FLASH_CLK(SCG_SLOW_CLK in SCG) | FLASH时钟 |

| SPLL_CLK | SPLL输出时钟 |

| SIRC_CLK | 内部慢速时钟 |

| FIRC_CLK | 内部快速时钟 |

| SOSC_CLK | 外部时钟(晶振、时钟源) |

| RTC_CLKOUT | RTC时钟外部输出 |

| LPO32K_CLK | RTC时钟源 |

| LPO128K_CLK | PMC生成的始终开启的低功耗振荡器时钟。 |

| SCG_CLKOUT | SCG输出时钟 |

| LPO_CLK | LPO三个时钟源的选择输出时钟 |

| CLKOUT | 内部八种时钟的选择输出时钟 |

| VCO_CLK | SPLL倍频时钟,最大320MHz |

| SPLLDIV1_CLK | SPLL分频时钟,RUN模式最高80MHz,HSRUN模式i最高112MHz |

| SPLLDIV2_CLK | SPLL分频时钟,RUN模式最高40MHz,HSRUN模式i最高56MHz |

| FIRCDIV1_CLK | 内部高速时钟分频,RUN/HSRUN模式最高48MHz |

| FIRCDIV2_CLK | 内部高速时钟分频,RUN/HSRUN模式最高48MHz |

| SIRCDIV1_CLK | 内部低速时钟分频,RUN/HSRUN模式最高8MHz,VLPR/VLPS模式最高4MHz |

| SIRCDIV2_CLK | 内部低速时钟分频,RUN/HSRUN模式最高8MHz,VLPR/VLPS模式最高4MHz |

| SOSCDIV1_CLK | 外部时钟分频,RUN/HSRUN模式最高40MHz |

| SOSCDIV2_CLK | 外部时钟分频,RUN/HSRUN模式最高40MHz |

此处需要特别注意一点,SPLL_DIV1和SPLL_DIV2两个分频时钟在使用时要注意分频后的频率,笔者发现即使配置为160MHz,配置工具也不会提示错误。

1.3 时钟配置注意事项

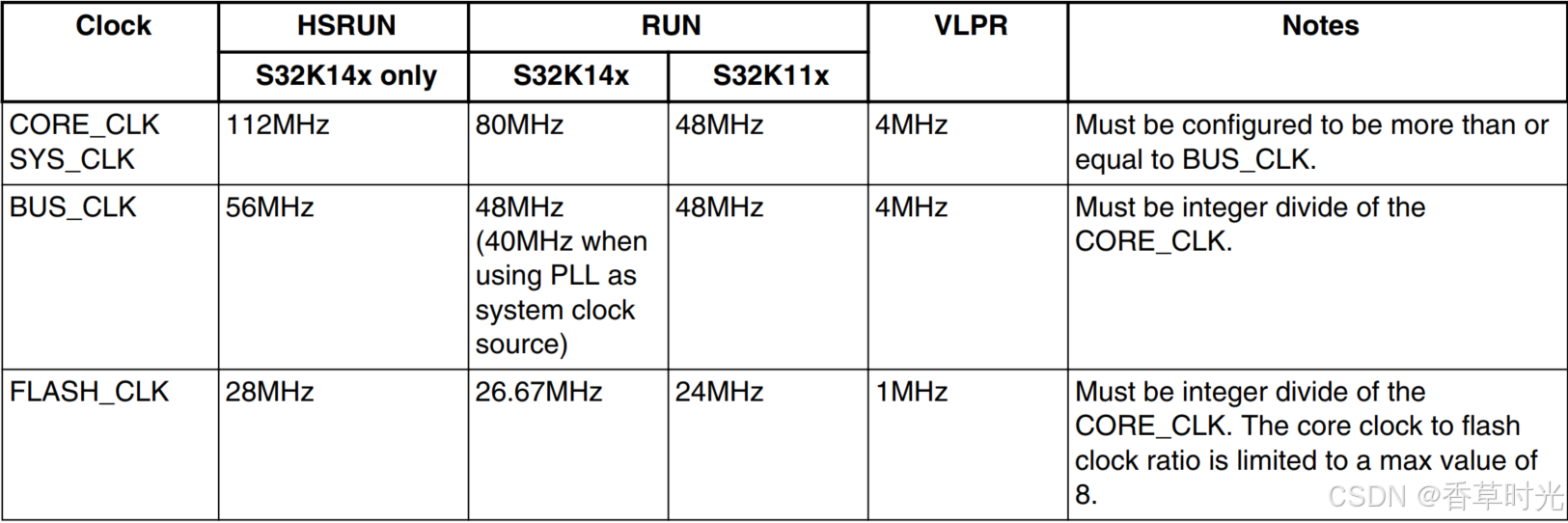

S32K144的时钟配置有一点要注意,那就是运行模式,系统运行相关的模式主要有3种(不包含STOP模式,关于系统的运行模式会单独开一篇文章讲解),分别是:

- HSRUN:高速运行模式,内核与系统时钟最高可达112MHz

- RUN:普通运行模式,内核与系统时钟最高可达80MHz,在S32K11X系列中可达48MHz

- VLPR:极低功耗运行模式,内核与系统时钟最高可达4MHz

下图是截取参考手册中关于各个模式的时钟频率说明,需要注意各个模式下的最高时钟频率限制。

根据参考手册中的描述,在做系统时钟的总体配置时需要注意以下原则:

- 系统上电初始化后使用的是内部高速时钟FIRC_CLK(也就是48MHz)并没有使用SPLL

- 所有外设时钟都由PCC模块控制,系统复位后,PCC模块会默认设置所有的外设时钟都关闭。所以和ST的芯片一样,在使用外设前需要开启对应的模块时钟

- 如果使用SPLL的话,外部的振荡器必须设置为高范围模式(中范围:4-8MHz;高范围:8-40MHz),且锁相环的VCO输出不能大于320MHz,SPLL_CLK不能大于160MHz

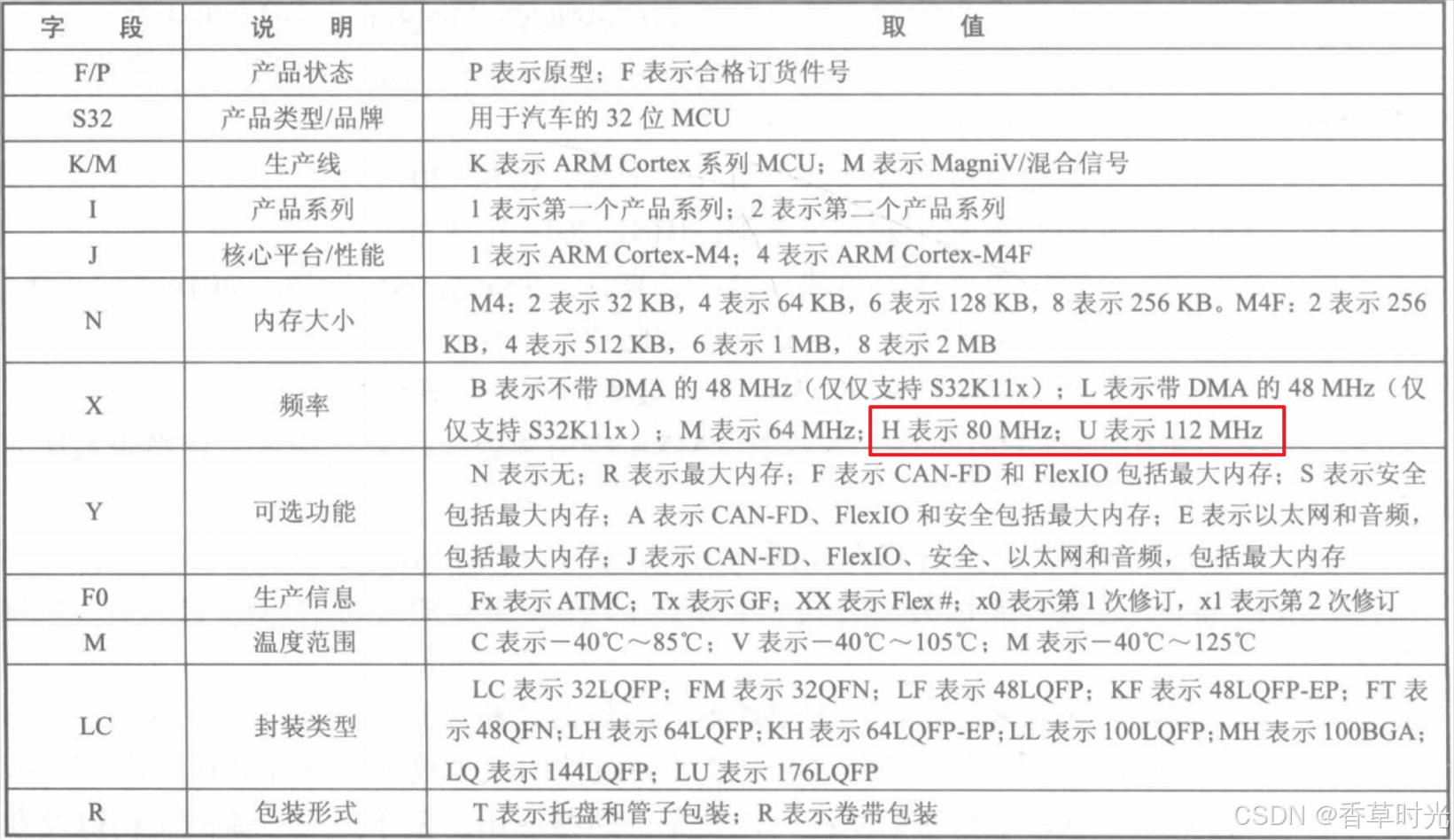

接下来就是和开发板的芯片有关的一些注意事项,官方的开发板使用的芯片是PS32K144HAT0MLLT,根据命名规则可知,开发板上的是H系列,最高频率为80MHz,正好是RUN模式的最高频率,HSRUN模式不适用此芯片(但其实经过笔者测试,不但该芯片可以在HSRUN模型下运行,频率也可以到达112MHz。H后缀和U后缀的差别在于频率和温度,笔者推测可能是由于生产上的原因造成了这样的芯片分类,就类似与X86处理器的I3、I5、I7之类的,只是在过AEC-Q100的时候由于环境条件的标准才做了这样的分类,以上纯属推测)。

2.程序验证

2.1 建立基于SDK的空白工程

单片机的学习特别重视实践,理论研究了半天,终于到验证的时候了,接下来就创建一个工程来验证各种模式下的时钟配置。

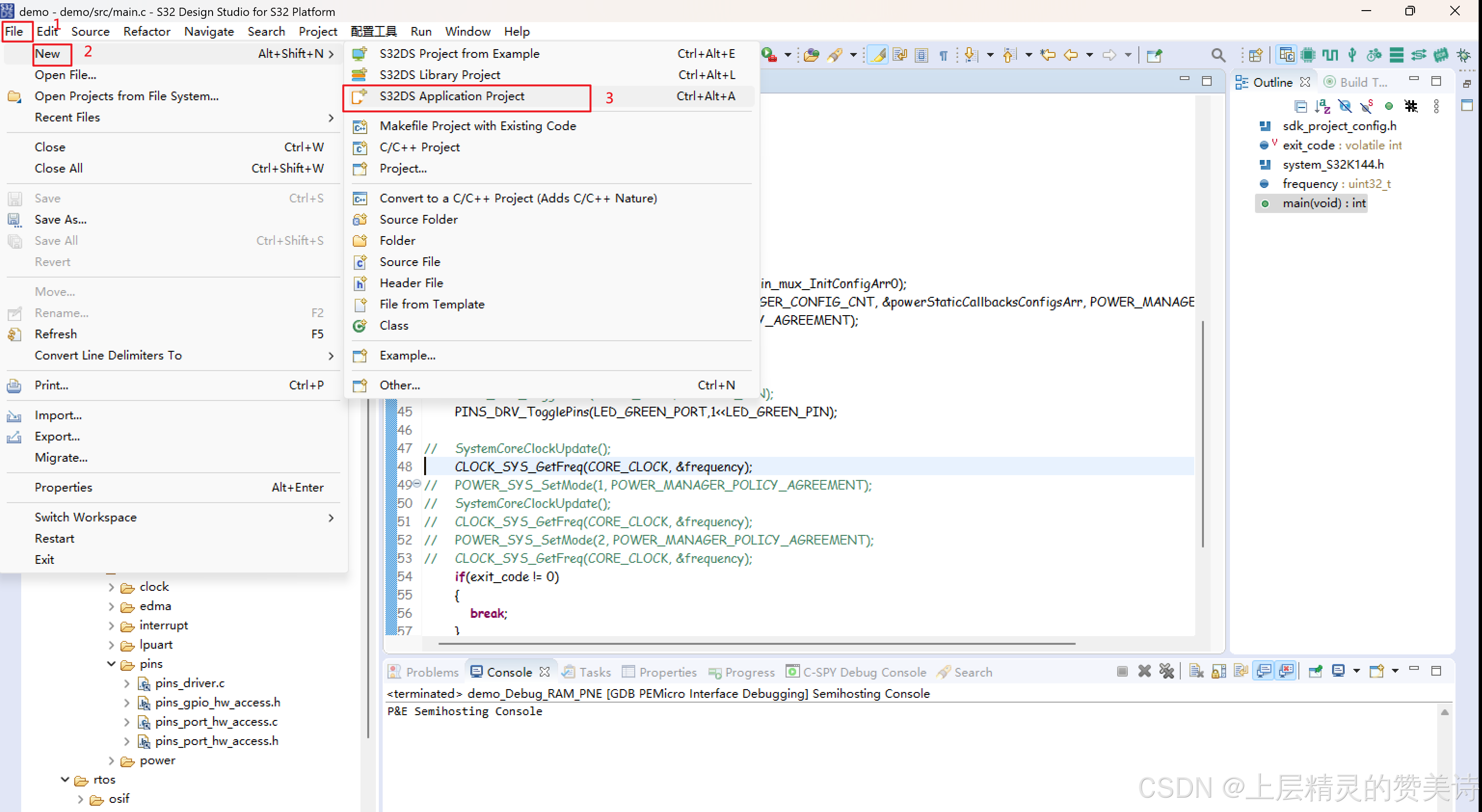

2.1.1 创建工程

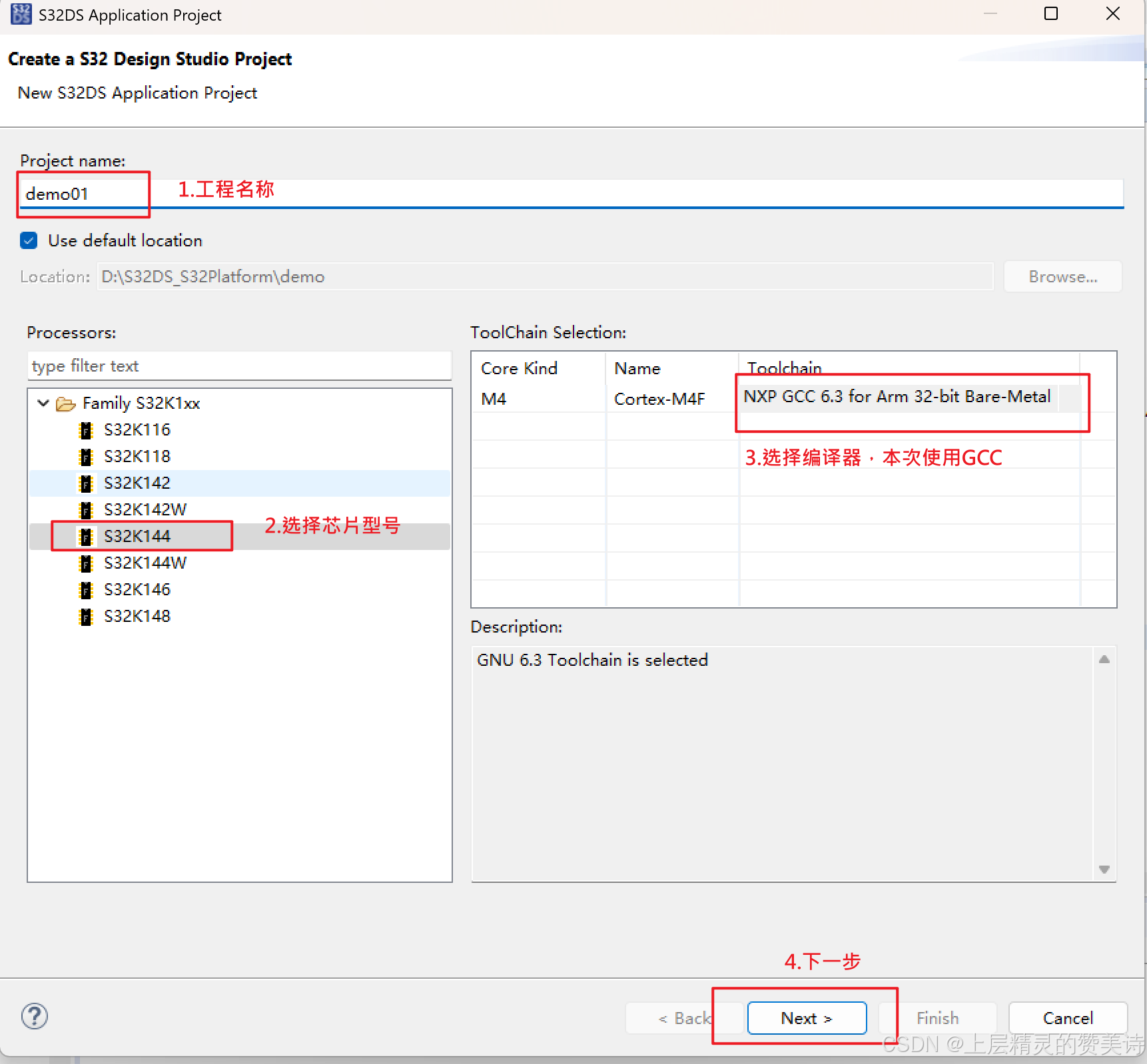

点击“File”->“New”,建立应用工程,如下图所示。

选择芯片型号和编译器,如下图所示

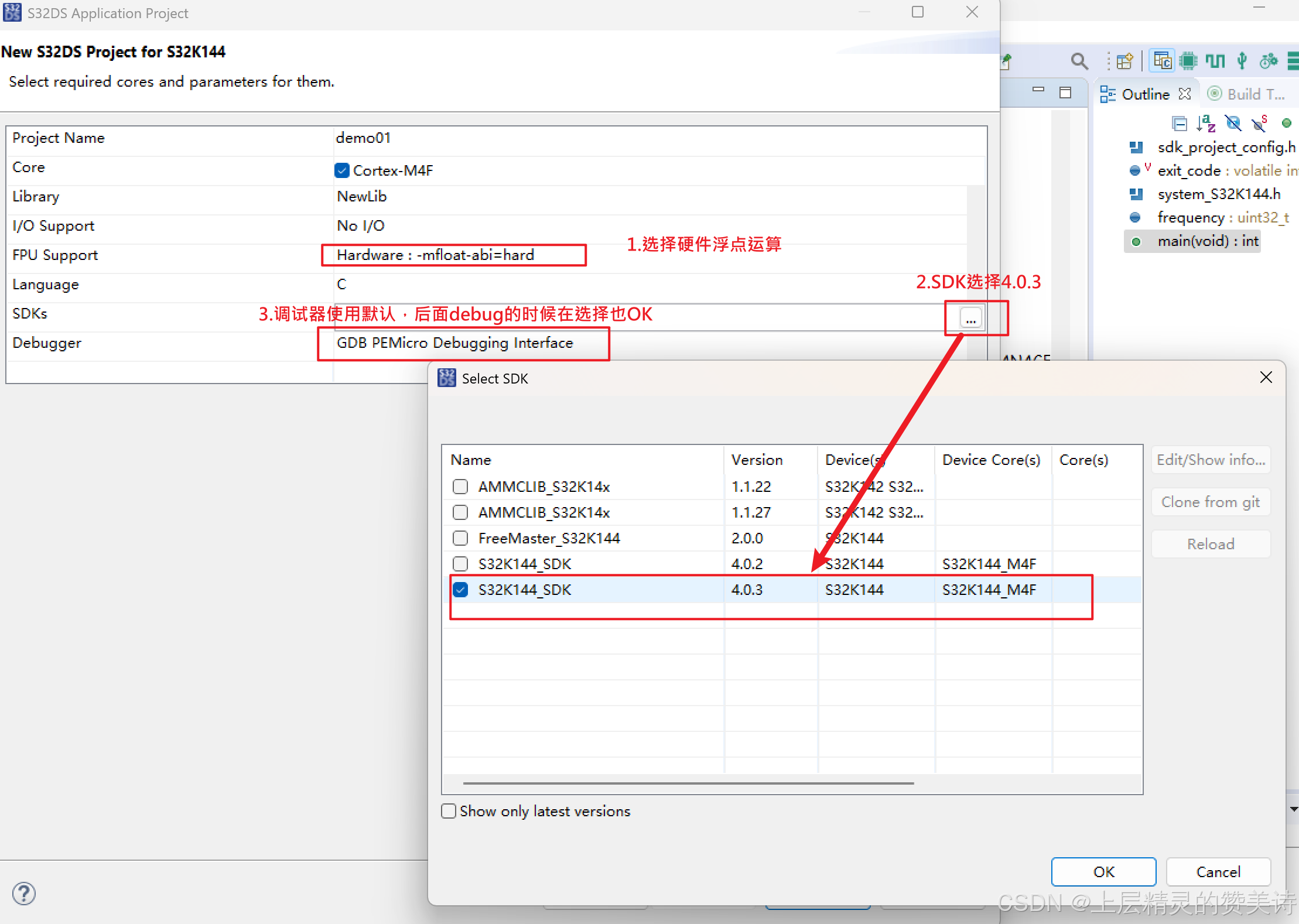

SDK和调试器设置,如下图。

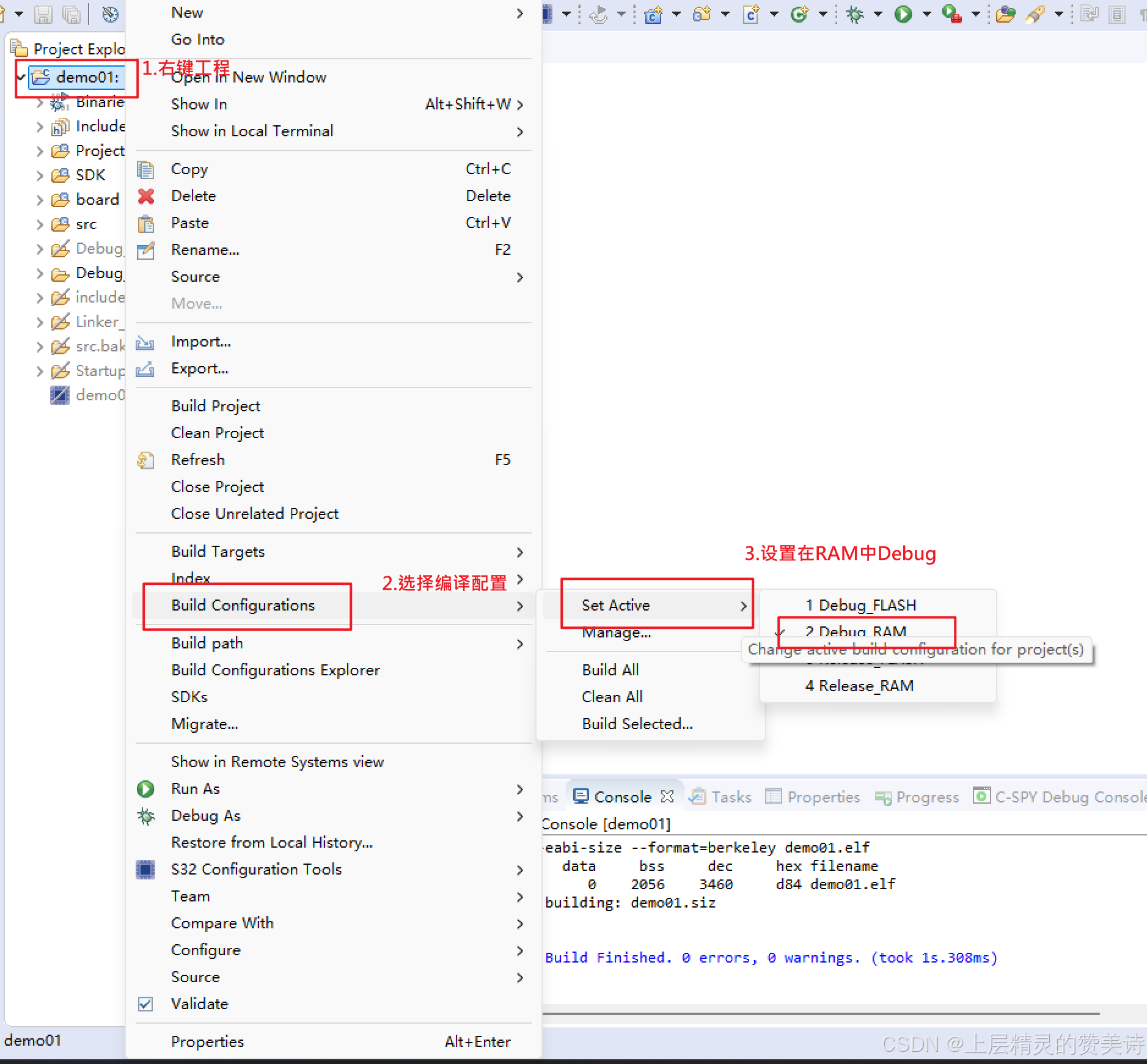

笔者一般在调试中喜欢在RAM中调试,配置如下:

2.1.2 时钟配置

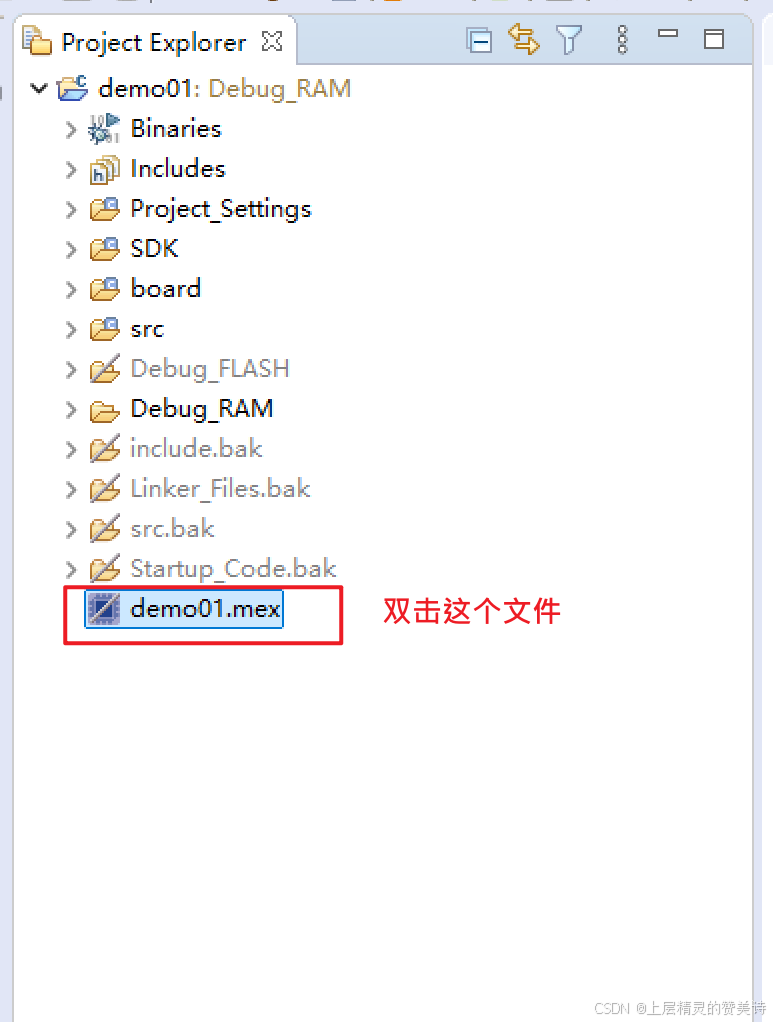

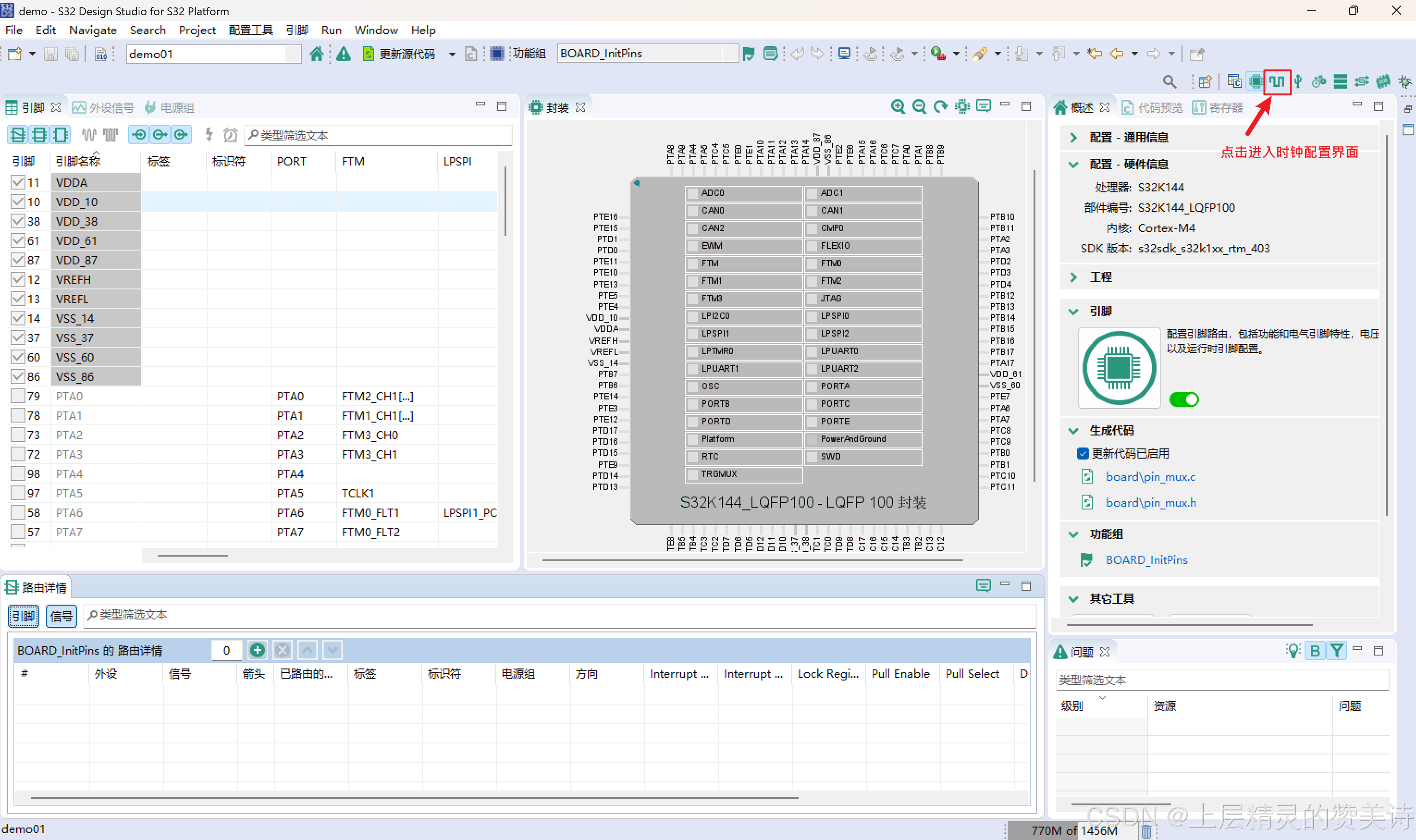

在S32DS for S32 platform环境中,他的时钟配置有点类似于STM32的配置工具,接下来打开配置工具,如下图。

进入配置工具界面,如下图

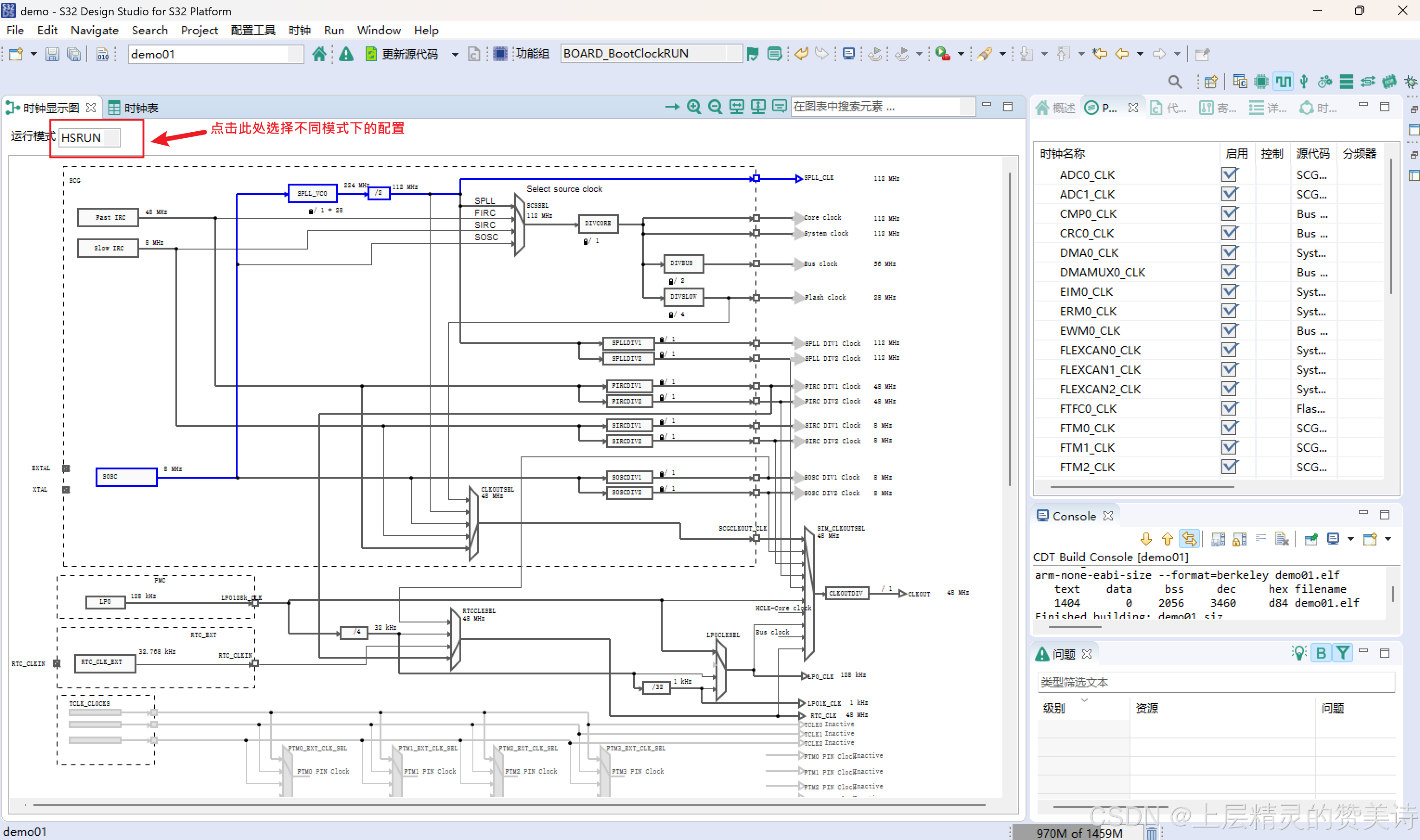

进入时钟配置界面后开始配置时钟,S32DS for S32 platform中的时钟树也是图形化的,很直观,如下图,左上角可以选择配置不同模式下的时钟,默认情况下,HSRUN被配置为112MHz,RUN使用内部48MHz时钟源,内核时钟配置为48MHz,VLPR使用内部8MHz时钟,内核时钟配置为4MHz。经过笔者粗略的看了一下参考手册和对配置工具反复配置之后的理解是:SPLL的倍频因数是不建议在芯片运行过程中更改的,所以在配置工具中也只允许配置一个SPLL,这点需要注意。还有一点需要小心:虽然鼠标悬浮在每个配置上都有一些说明,但是并不是所有的错误配置都会有警告,不知道是不是软件的BUG,所以在配置的时候还是要仔细阅读参考手册。

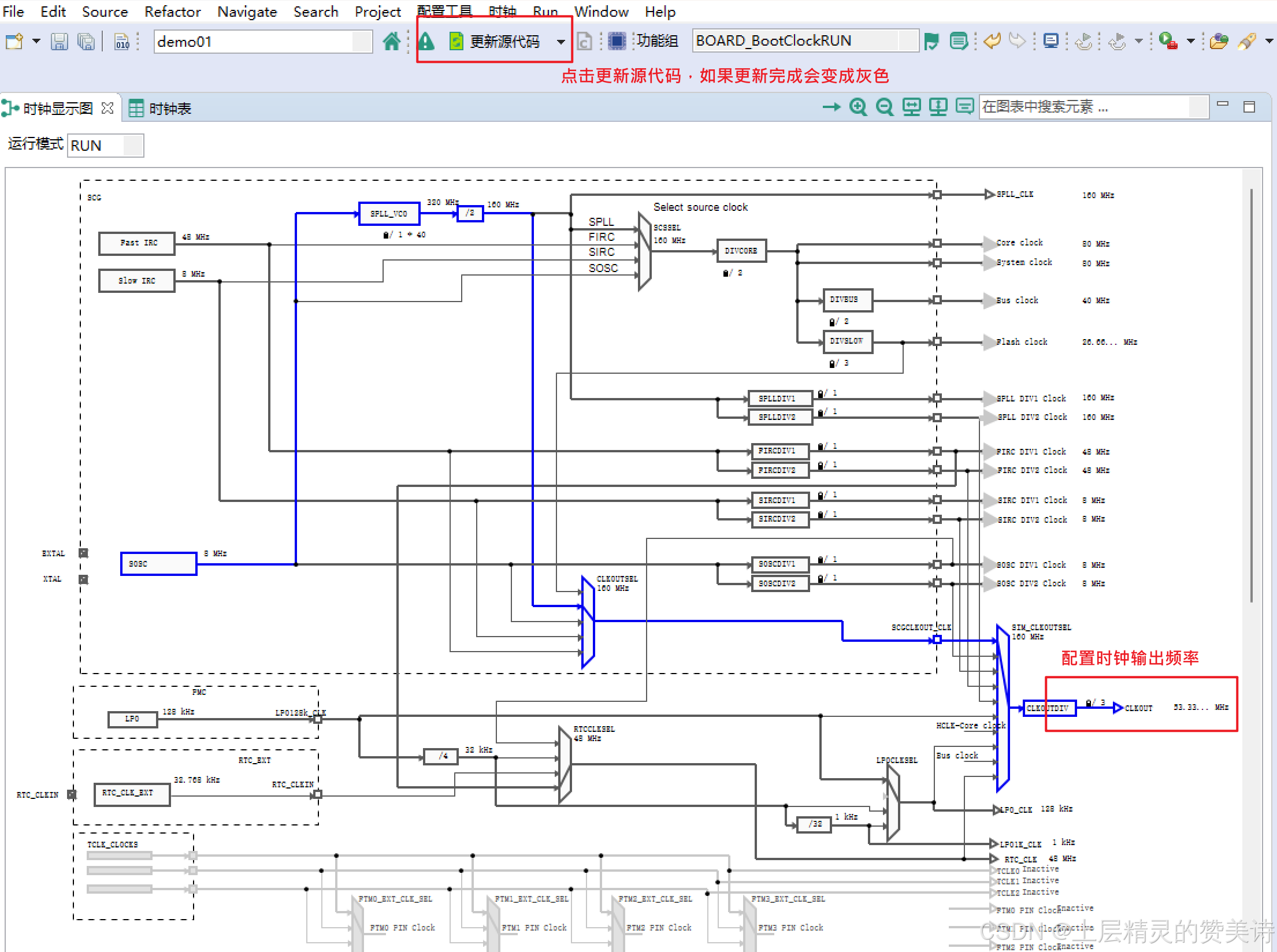

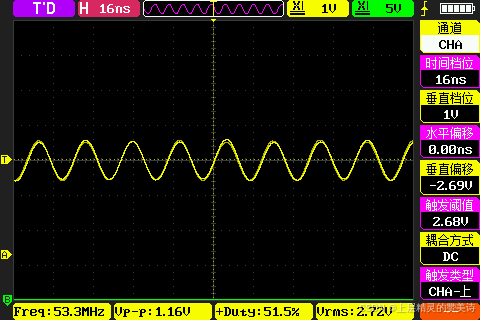

本次笔者配置一个RUN模式下,内核时钟80MHz的配置,此时虽然我们不用HSRUN,但是我们在RUN模式下使用了SPLL,正如上面所述,RUN和HSRUN共用SPLL倍频参数,所以要把HSRUN中报错的部分更改一下参数,因为笔者不使用HSRUN模式,所以随便设置下分频系数,不报错即可,另外,笔者配置时钟输出IO来输出SPLL时钟的3分频(53MHz左右)来测试时钟配置是否成功,配置结果如下图。

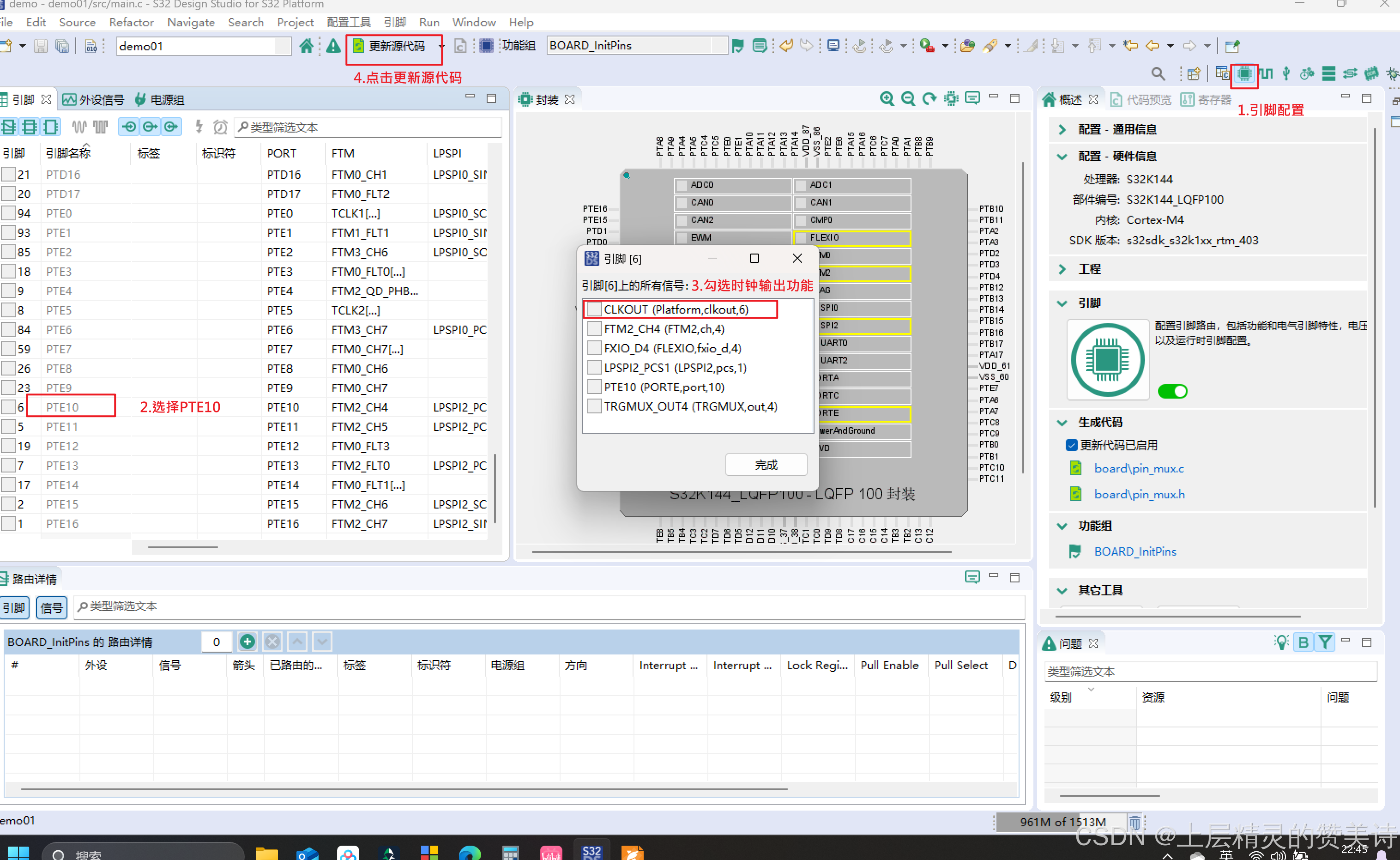

此外,需要配置时钟输出引脚为复用时钟输出模式,如下图。

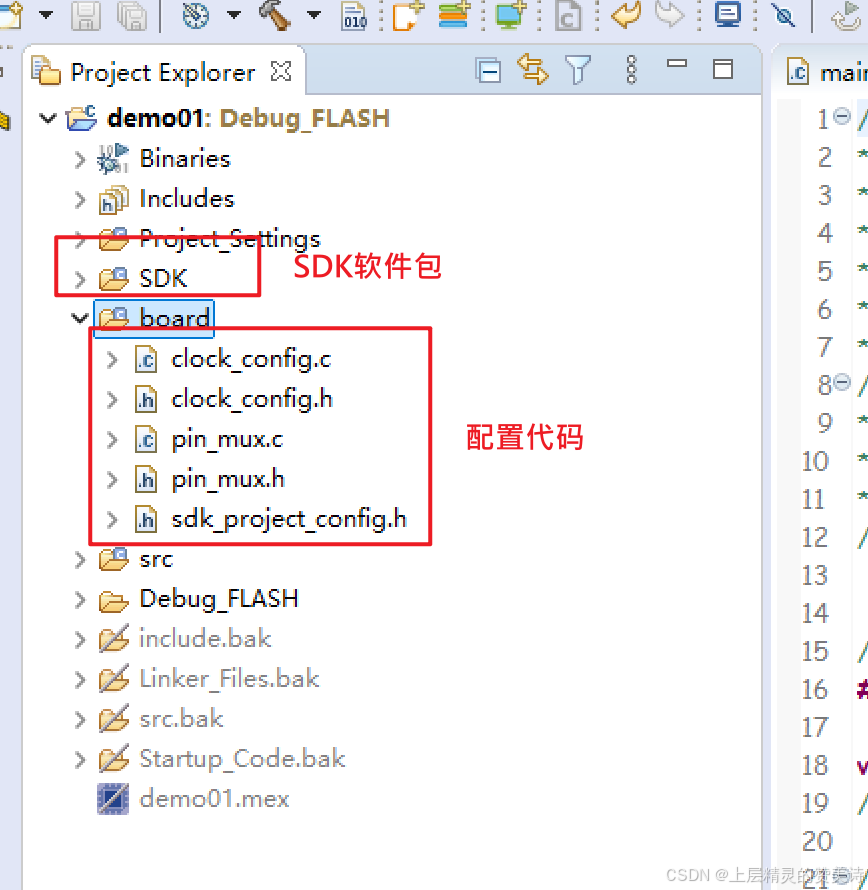

接下来要验证时钟配置,从这里开始,我感觉NXP做的和ST的有很大差别,第一他的工具思路类似于autosar的工具链,他将配置代码分为“静态代码”和“动态代码”两个部分,静态代码就是我们不需要更改的部分,也就是SDK;动态代码是工具生成的,这样也是做了一个代码的解耦。另外在main.c中并没有自动生成任何代码,需要我们自己将配置函数加入到工程中去,生成的配置代码放在“board”文件夹中,如下图所示。

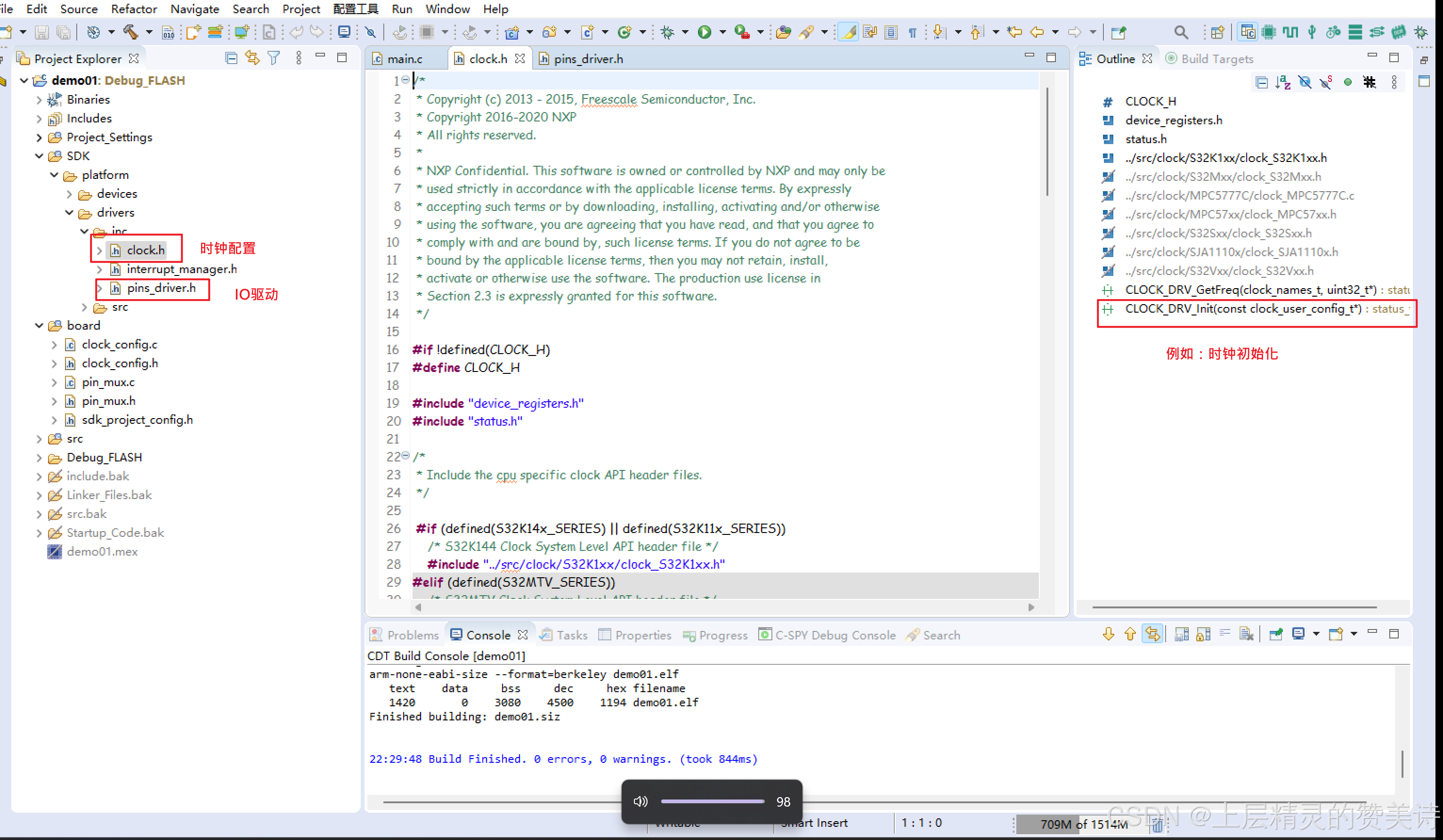

时钟配置的动态代码在clock_config.c和clock_config.h中,其中就是一些宏和结构体的定义,此处不做深入解读,而我们需要用到的函数是在SDK的静态代码包中,如下图。

这些函数都有使用说明注释,命名也很容易理解,此处列出本次实验所使用的函数:

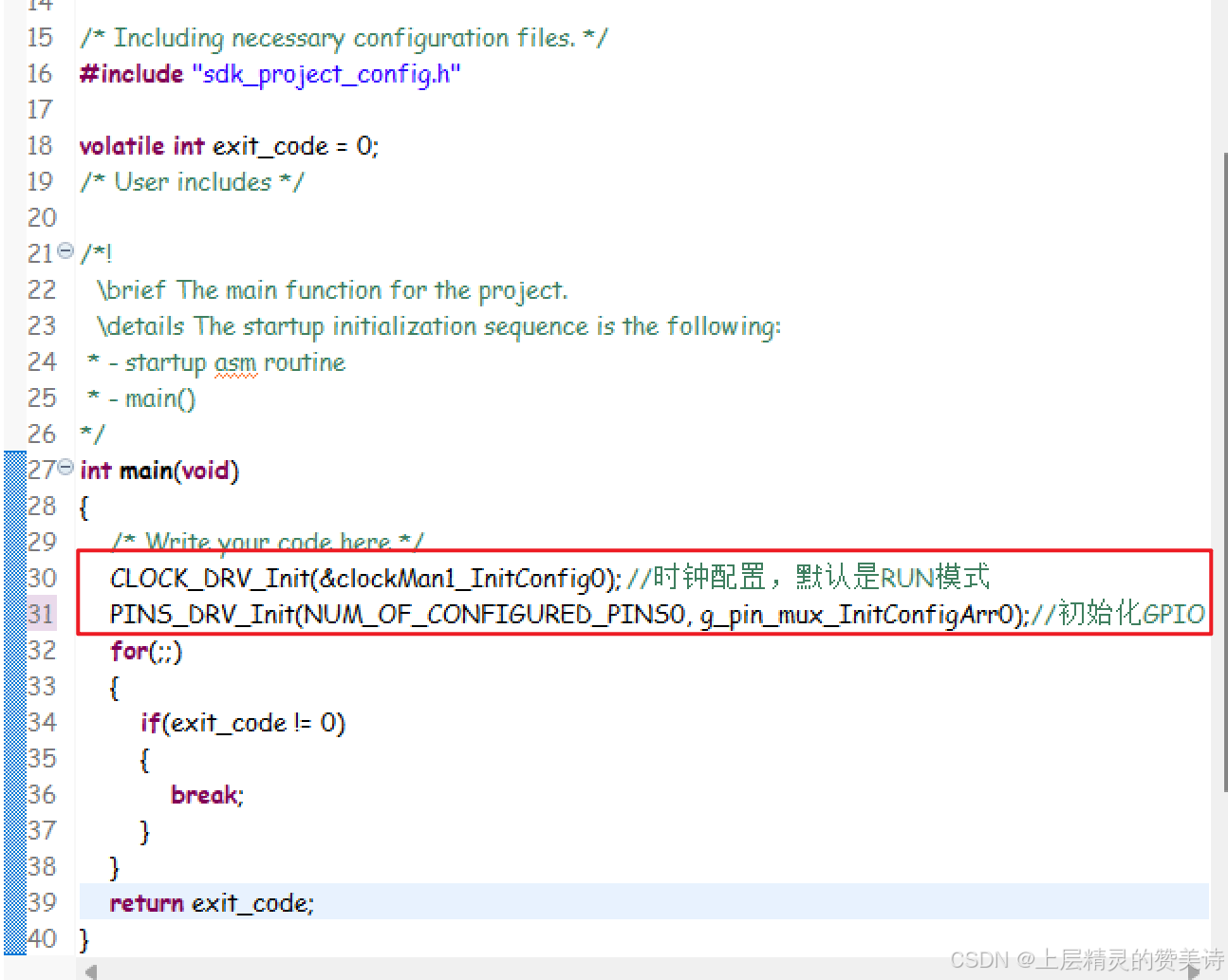

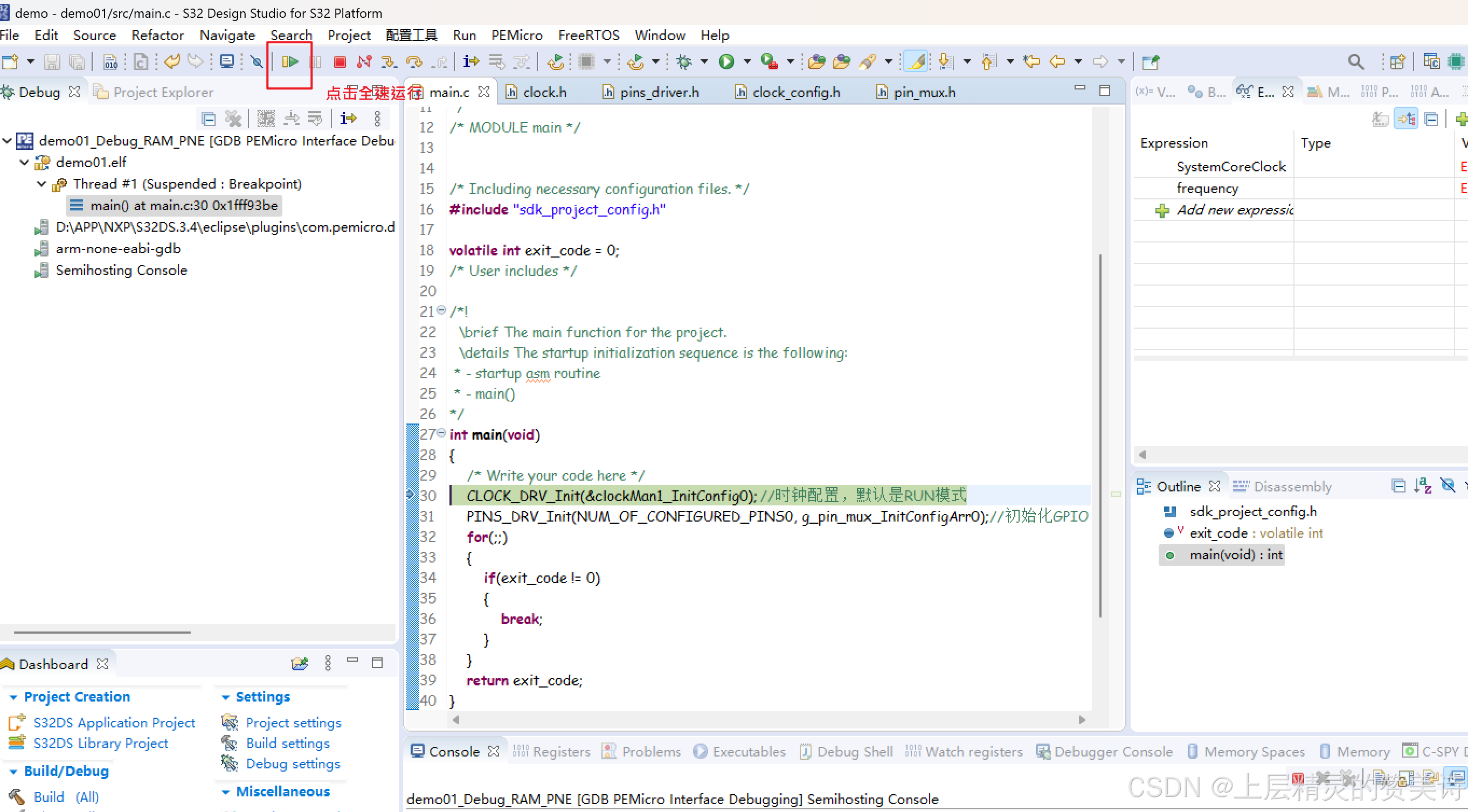

CLOCK_DRV_Init(&clockMan1_InitConfig0); //时钟配置,默认是RUN模式

PINS_DRV_Init(NUM_OF_CONFIGURED_PINS0, g_pin_mux_InitConfigArr0);//初始化GPIOmain函数如图所示。

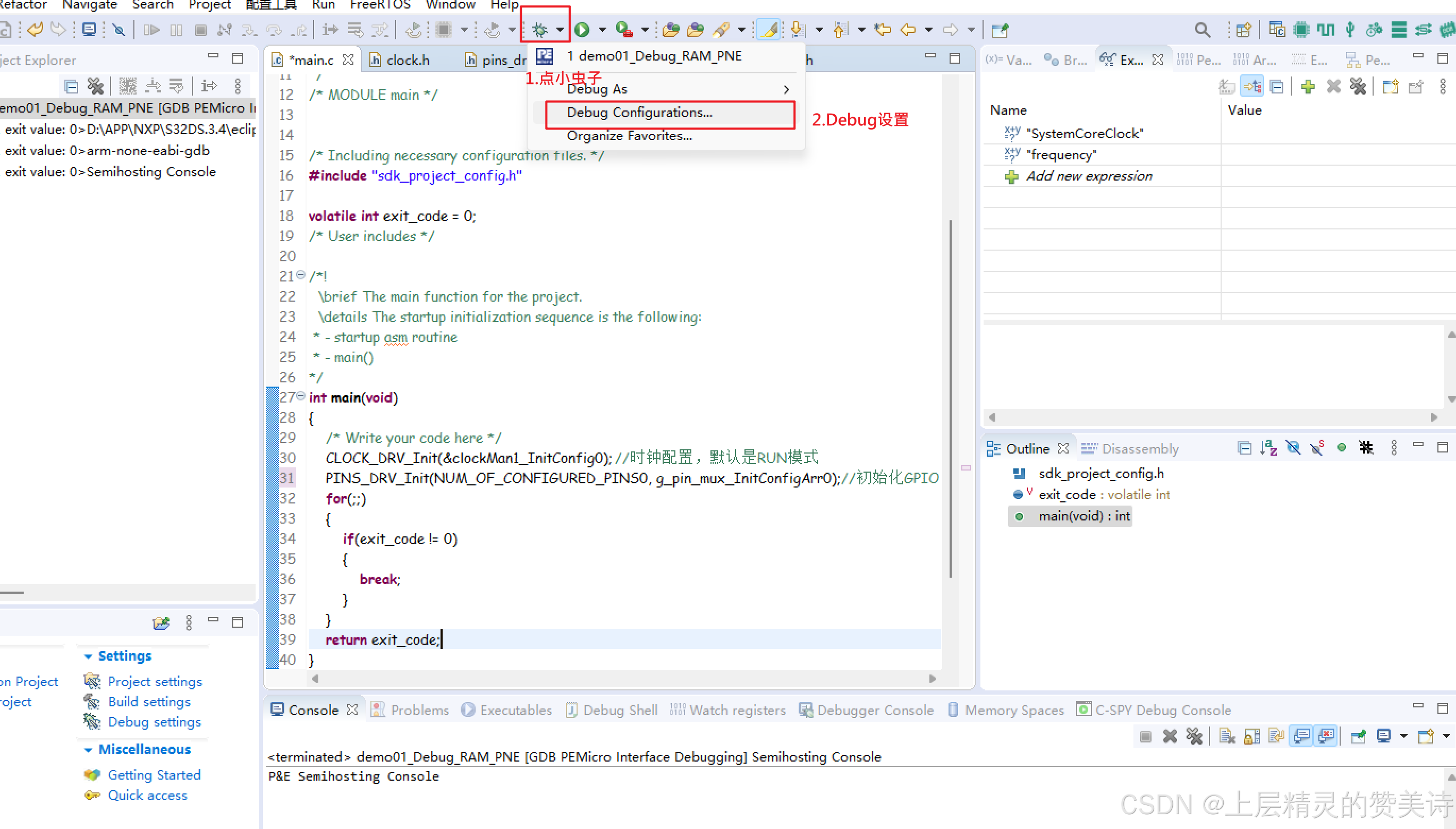

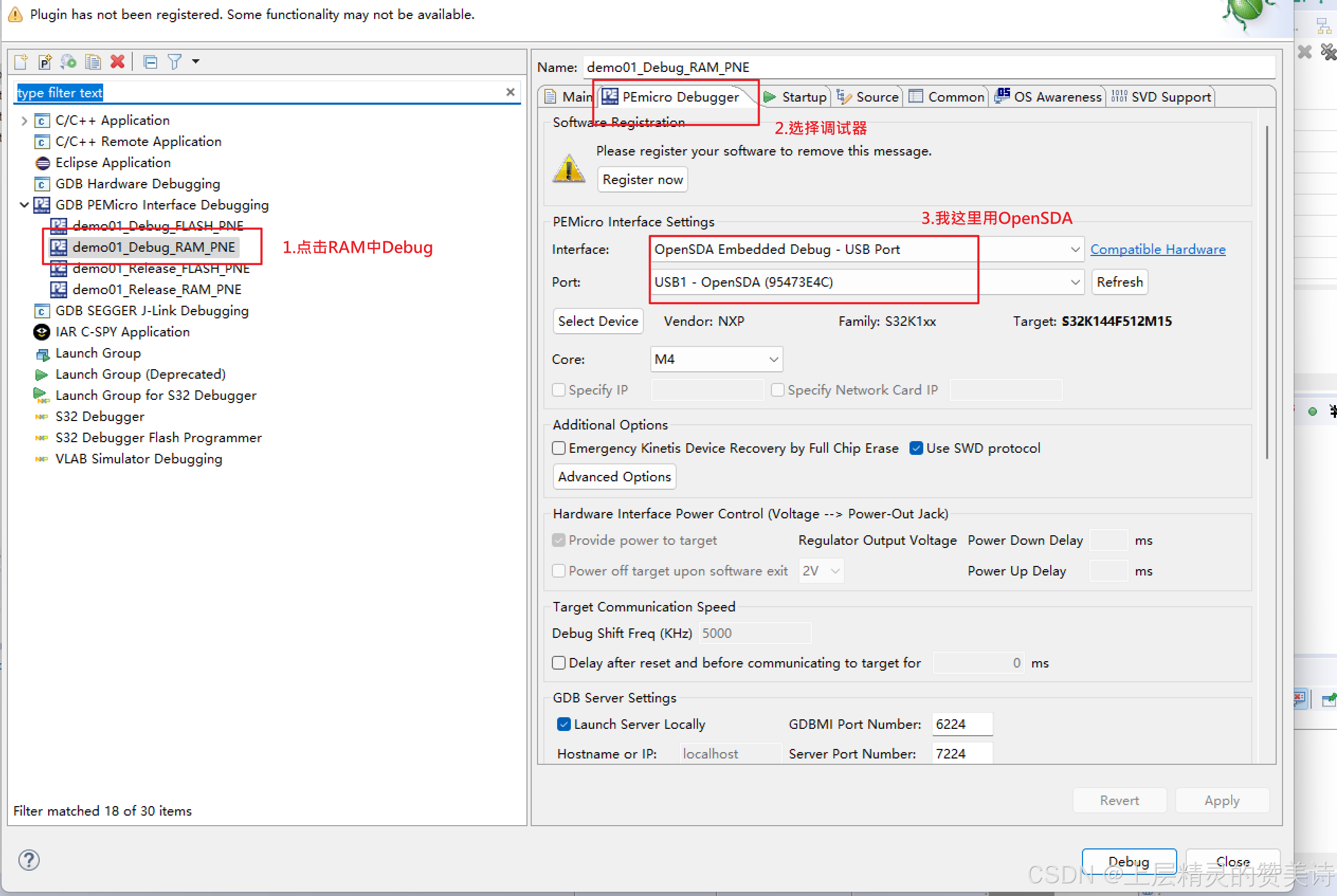

点击debug将代码下载到板子上并通过示波器看时钟输出是否正确。Debug设置如下。

设置调试模式和调试器,如下图。

运行程序,如下图

通过示波器观察时钟输出引脚的频率,如下图

输出波形53MHz左右,与理论相互印证,本次实验结束。

想了解笔者使用的开发环境请参考上一篇文章。

上一篇文章:S32K144入门笔记(一):环境搭建与配置

3075

3075

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?