第十一步,编写Makefile

all: compile simulate dve_wave log open dve_cov

rnd_seed = $(shell data+%s) //随机种子,随着时间的变化而不断变化

tc_num = 0 //默认的make测试是tc_num=0

compile: //编译

vcs -full64 -l comp.log -sverilog -f rtl.f -debug_pp -timescale=1ns/1ns \

-cm line+cond+fsm+tgl \

../tb/ahb_slv_if.sv \

../env/transaction.sv \

../env/generator/generator.sv \

../env/agent/agent.sv \

../env/driver/driver.sv \

../env/monitor/monitor.sv \

../env/scoreboard/scoreboard.sv \

../env/environment.sv \

../tests/ahb_sram_test.sv \

../tb/ahb_sramc_svtb_top.sv

simulate: //生成一个./simv的文件,然后开始simulate,不同的种子产生不同的log.

./simv -l sim_$(tc_num).log +plusargs_save \ //plusargs_save 表示rnd_seed和tc_num可以传递给后面的代码

+ntb_random_seed=$(rnd_seed) \

+tc_num=$(tc_num)

dve_wave: //通过dve_wave产生波形

dve -vpd vcdplus.vpd&

dve_cov: //coverage产生覆盖率

dve -full64 -covdir simv.vdb&

log:

sed '/^[^*].*/d' sim_$(tc_num).log > rslt.log

open: //打开gvim可以看到

gvim rslt.log

clean: //清除文件

rm -rf work mti_lib transcript modelsim.ini *.log *.wlf test.ucdb 更多的Makefile文件可以参考这篇文章https://blog.youkuaiyun.com/weixin_38967029/article/details/125906452

第十二步,编写rtl.f文件

文件中存放的是rtl代码,可以用于添加文件目录表,一遍用于Makefile 方式的操作

../../rtl/ahb_slave_if.v

../../rtl/mbist_8kx8.v

../../rtl/RA1SH.v

../../rtl/sram_bist.v

../../rtl/sram_core.v

../../rtl/sramc_top.v

第十三步,VCS编译仿真

scoreboard部分的check部分出现较多错误

但是观察总体读写信号,hwdata和hrdata没有发生错误,应该是scoreboard部分写的有问题,sram_gld_rdata和sram_dut_rdata的比较和数据写读放在一起,还在if的条件中,可能造成了时序上的影响,单独把check拿出来,分为start和check两个部分,重新运行。

修改后的scoreboard部分,没什么问题了,运行tc000, 显示TEST PASS

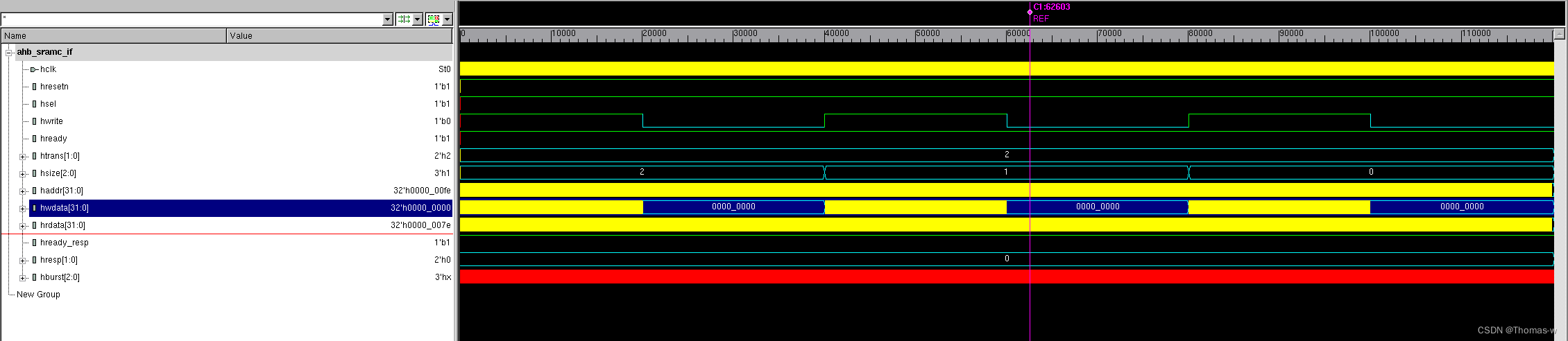

add wave之后和tc000代码比较,发现没有出入,整体上分为六个部分,先写在读,读的时候hwdata数值为0,

hsize数值变化,改变了数值递增的大小。

功能覆盖率:haddr中只有ahddr_0被覆盖到,且次数为5999次 ,这是因为tc000是从低位开始往高位开始写,此时数6000个,haddr_0 = {[32'h0:32'h0000_1FFF]};,32'h0000_1FFF=32'd8191,所以只覆盖到haddr_0

测试案例1 :地址递减,数据固定

测试案例2:地址递增,数据随机写入

测试案例3:插入无效操作,写一个数据,插入一个无效操作,读也是一样。无效操作会随机化所有的transaction数据,hsel和htrans拉低。

测试案例4:写+无效周期+读+无效周期,分32、16、8三组进行。

测试案例5:地址递增,数据随递增,写读32位数据

运行tc_num=5案例的时候,会发现终端一直没有显示仿真结束时间,ctrl+c打断发现一直在运行,仿真中应该遇到错误了,结合相关代码发现32位数据时候,我们限制了haddr[1:0]==2'b00,32'd100=32'h64,所以错误发生在这里,取消或者重新编写约束c4就可以了。

测试案例6:定向用例7.遍历整个SRAM空间(写全0、全1、全5、全A)

本文详细介绍了如何编写Makefile、rtl.f文件,以及VCS编译过程中的调试与优化,重点讨论了scoreboard部分的修复、覆盖率测试和多案例分析,包括地址递减、数据随机写入等。通过实例演示了如何解决时序问题并提高测试覆盖率。

本文详细介绍了如何编写Makefile、rtl.f文件,以及VCS编译过程中的调试与优化,重点讨论了scoreboard部分的修复、覆盖率测试和多案例分析,包括地址递减、数据随机写入等。通过实例演示了如何解决时序问题并提高测试覆盖率。

4275

4275

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?