1、概念域:

硬件世界:module-endmodule 、interface-endinterface

软件世界:program-endprogram、class-endclass

initial的使用域:initial过程块可以在module、interface和program中使用,对于过程块的书写用begin-end包裹住

always的使用域:always过程块的是用来描述硬件时序电路和组合电路的正确打开方式,因此只可以在module或者interface中使用

2、函数function

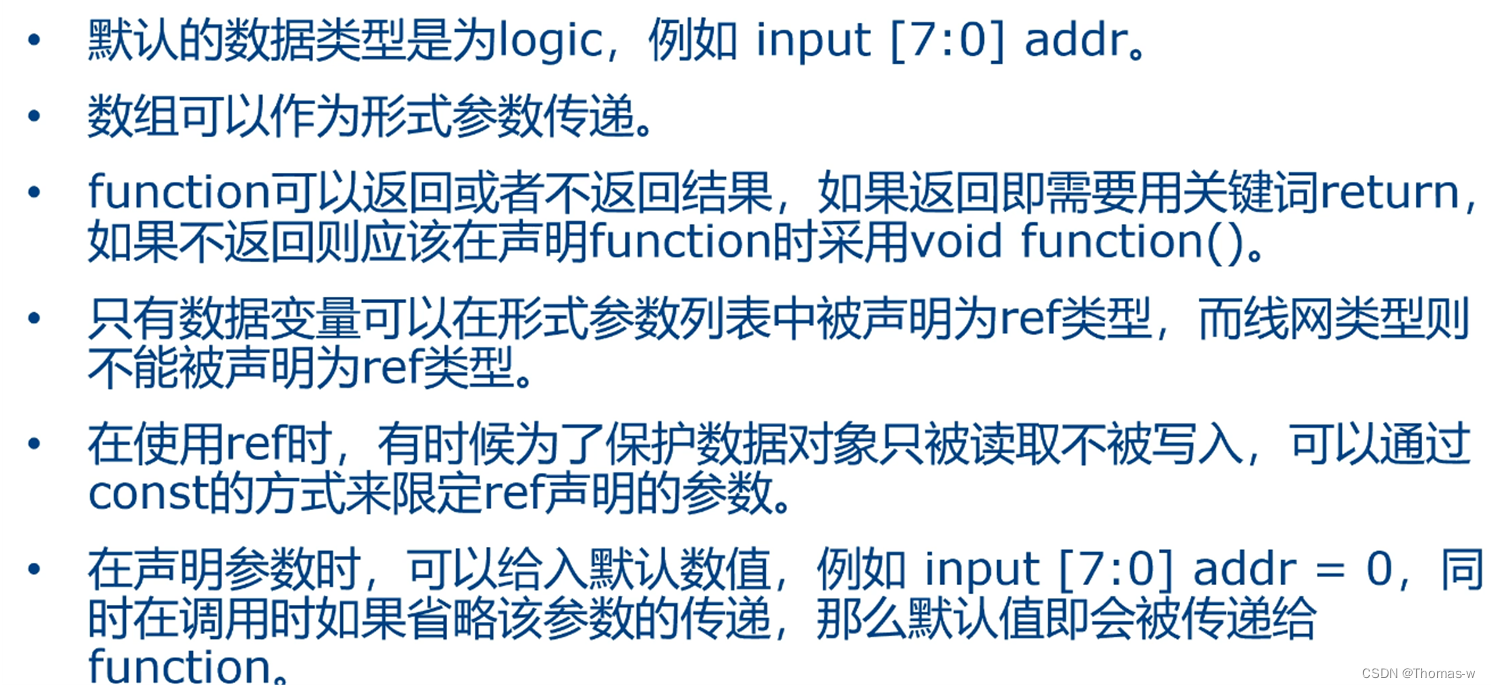

function可以在参数列表中指定input、output、onout和ref,可以返回数值后者不返回数值(void)

3.方法task

task无法通过return返回结果,只能通过output、inout或者ref的参数来返回,task可以内置耗时语句,而function却不可以,常见的耗时语句有@event、wait event 、#delay等等

| 函数function | 任务task |

| 不消耗仿真时间 | 消耗仿真时间 |

本文详细介绍了Verilog和SystemVerilog中的关键概念和语句。包括module、interface、program的使用,initial和always过程块的域,以及function和task的区别。此外,还讨论了子程序的返回机制、动态数据与静态数据的生命周期,以及高级参数类型如ref和const的作用。同时,时间值的表示、时间和变量的处理也被提及,强调了在设计中如何控制仿真时间。

本文详细介绍了Verilog和SystemVerilog中的关键概念和语句。包括module、interface、program的使用,initial和always过程块的域,以及function和task的区别。此外,还讨论了子程序的返回机制、动态数据与静态数据的生命周期,以及高级参数类型如ref和const的作用。同时,时间值的表示、时间和变量的处理也被提及,强调了在设计中如何控制仿真时间。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

5438

5438

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?