在verilog代码中有这样一段,rst_n 对 led 异步复位:

always@(posedge clk or negedge rst_n)

if(rst_n == 1'b0)

led <= 4'b1111;

else

led <=led ;

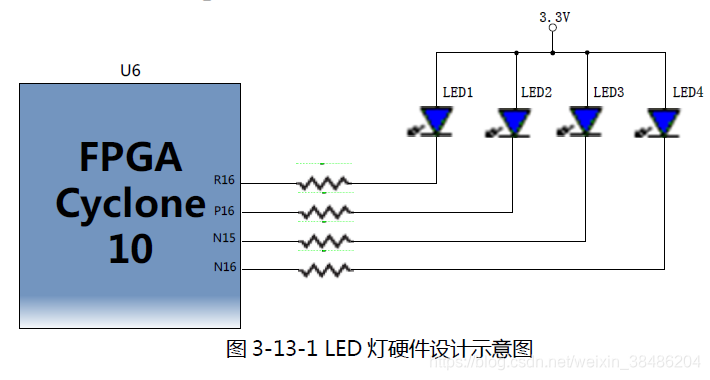

开发板LED是共阳极连接的,如下图:

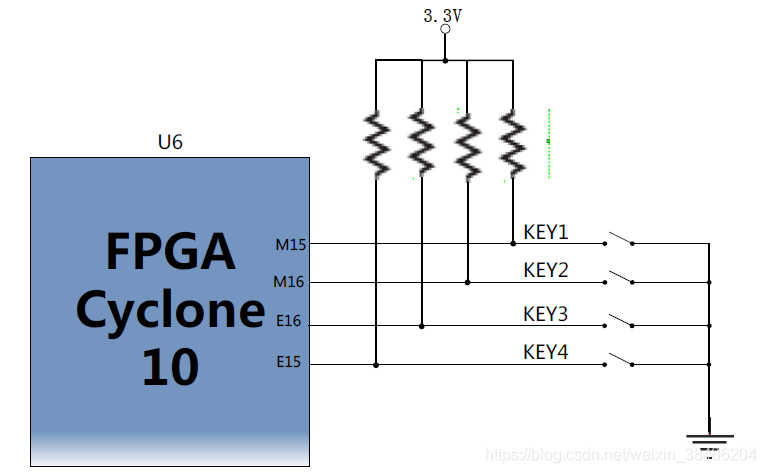

开发板按键是上拉到VCC连接的,如下图:

将rst_n配置到KEY1,程序下载后,KEY1按键未按下,led应当全部点亮才对,但是led全部熄灭(led的初始值应该是4'b0000)。

针对以上问题,可能出现以下几种情况导致异步复位执行了:

情况1:KEY1按键在下载程序后被误触发了?

情况2:FPGA对rst_n信号敏感,自动执行?

情况3:FPGA默认输入引脚为低电平?

对以上问题进行验证,用signal_tap对rst_n信号进行采样,未发现它存在下降沿,排除KEY1按键误触发的可能。

添加key信号,将代码修改为:

always@(posedge clk or negedge rst_n)

if(rst_n == 1'b0)

led[3:2] <= 2'b11;

else

led[3:2] <= led;

always@(posedge clk or negedge key)

if(key == 1'b0)

led[1:0] <= 2'b11;

else

led[1:0] <= led[1:0];

key按键未按下,同样能让led信号变高,排除FPGA对rst_n信号敏感的可能。

下载程序后,FPGA默认输入引脚为低电平???----FPGA上电后默认寄存器的值为0。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?