今天分享在数字IC芯片设计实现做timing signoff阶段必须要看的report。check_timing的报告必须是clean的,否则芯片回来大概率是废片!!!实际上一堆公司的芯片败在不看这个report了。

我们知道primetime(简称PT)做时序检查是基于我们给定的signoff sdc时序约束。所以timing结果的准确性就取决于sdc的完备性。如果sdc有漏洞,自然这个timing结果就不可信。但好在PT会报出当前设计sdc可能存在的问题。

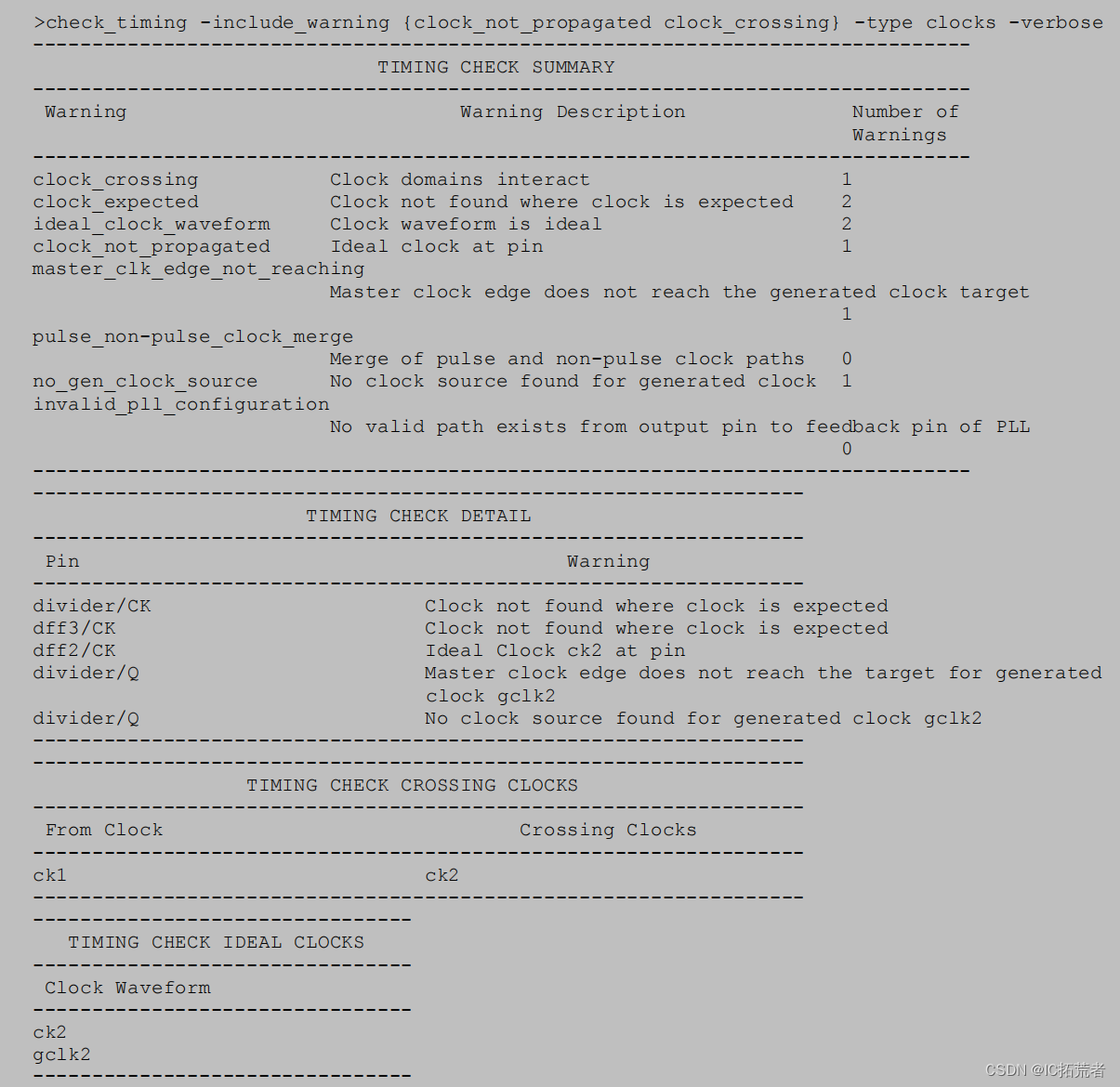

所以我们在跑完pt必须带上check_timing检查下sdc的完备性。如果sdc有问题,工具会报出如下图所示的警告!记住每个警告都必须review一遍。如果认为是假的或无关紧要,请签字画押!

如果是用的cadence的tempus工具检查timing,也会报出类型的警告信息。原理是一样的,只不过叫法可能不太一样。

PT check_timing主要检查以下这些item。

● generated_clocks

检查generated_clocks的定义是否合理,有没有源时钟,是否存在相互循环定义的情况。

对于如下所示电路施加下面的sdc约束,在check_timing时就会报generated clock定义问题。

数字IC后端设计实现之时序约束generated clock约束

create_clock -name ck1 -period 10

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

7502

7502

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?