提要:

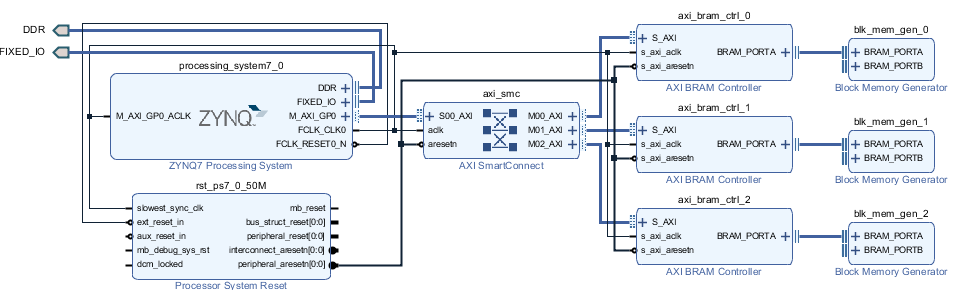

如果想通过axi总线控制bram,调用axi_bram_ctrl模块,那么后端的bram必须要配置成Bram Ctrl MODE;

如果是全部自己写代码控制bram,建议用stand alone MODE,地址线的分配跟思维一致;

最理想的方式是双口ram一侧是axi的bram-ctrl模式,另一侧是stand-alone模式给user控制,但是mode只能选一种;

True Dual Port RAM TYPE,Width-32,Depth-2048,MemSize-8192;

一、配置

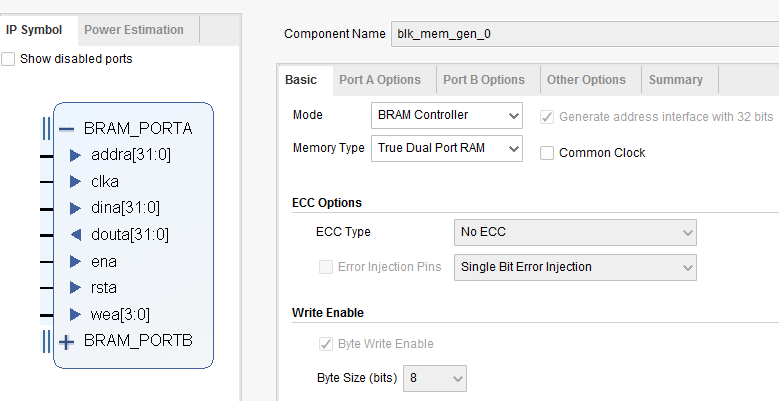

blk_mem_gen_0: Bram Controller MODE;默认使用32bit-addr;默认勾选Byte Write Enable,32bit-width的每个byte都能单独控制,we[3:0];

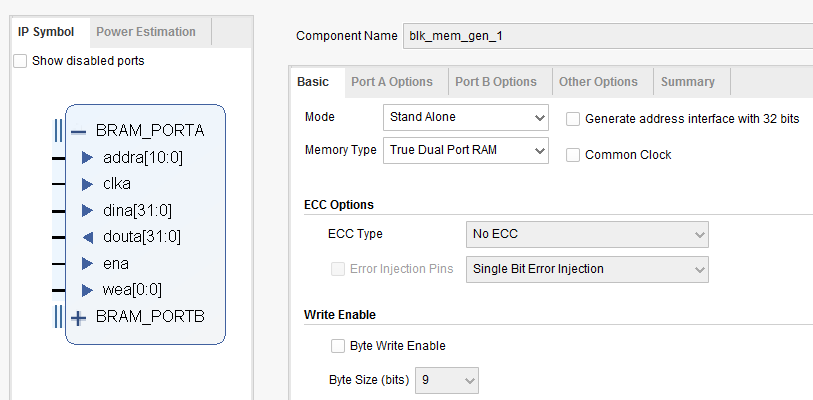

blk_mem_gen_1: Stand Alone MODE,2K-depth对应 11bit-addr,addr[10:0];没有勾选 Byte Write Enable 则是一个we[0:0]控制整条位宽;

blk_mem_gen_2: Stand Alone MODE,勾选了 Byte Wr

本文详细介绍了在FPGA设计中,如何配置BRAM以适应AXI总线的BRAM控制器模式和独立模式。在BRAM控制器模式下,地址线从[2]开始,而在独立模式下,地址从[0]开始。同时,文章讨论了两种模式下地址线和写使能信号的不同连接方式,以及它们如何影响对RAM空间的访问。

本文详细介绍了在FPGA设计中,如何配置BRAM以适应AXI总线的BRAM控制器模式和独立模式。在BRAM控制器模式下,地址线从[2]开始,而在独立模式下,地址从[0]开始。同时,文章讨论了两种模式下地址线和写使能信号的不同连接方式,以及它们如何影响对RAM空间的访问。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1949

1949

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?