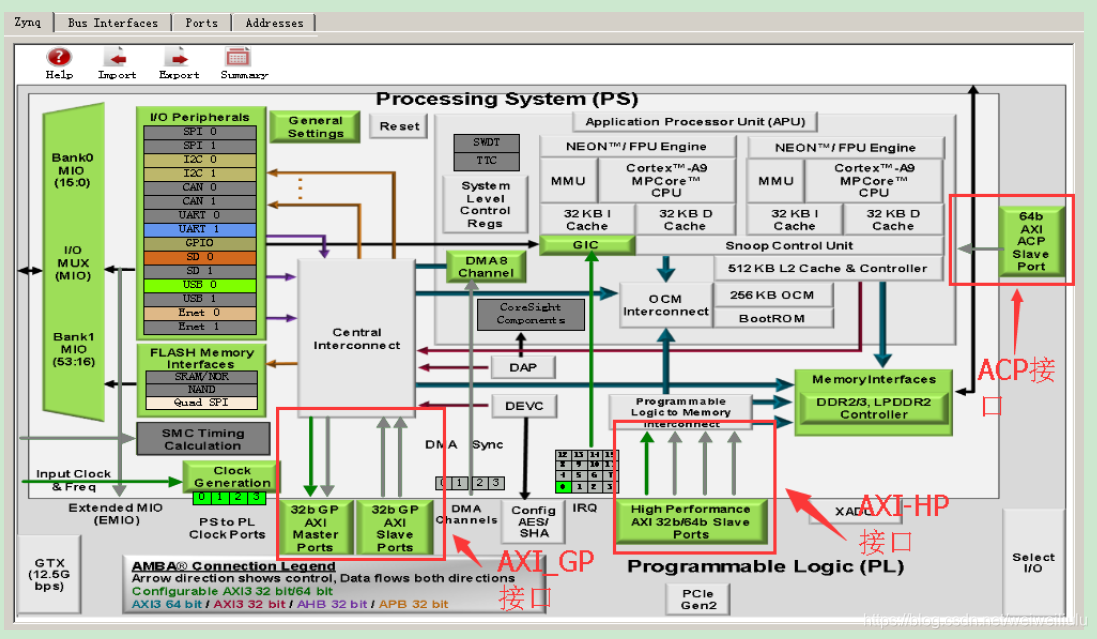

1. ZYNQ 概述

2. AXI 概述

AXI (Advanced eXtensible Interface)是xilinx 从6系列fpga开始引入的一个接口协议,主要描述了主设备和从设备之间的数据传输方式。主设备和从设备之间通过握手信号建立连接。当从设备准备好接收数据时,会发出ready信号。当主设备的数据准备好时,会发出和维持VALID信号,表示数据有效。数据只有在valid 和ready信号都有效的时候才开始传输。

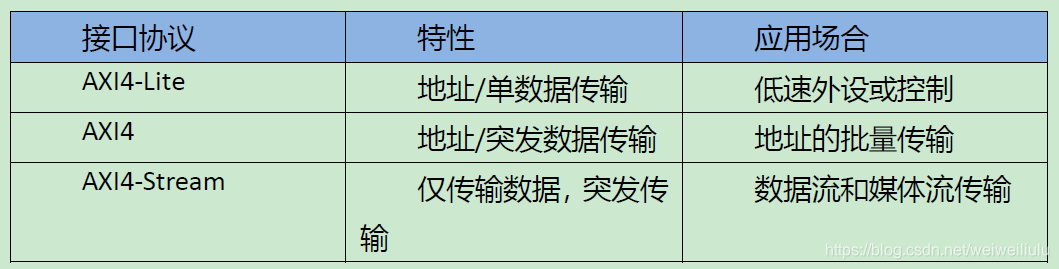

在zynq中,支持AXI-LITE,AXI4 和AXI Stream 三种总线。

AXI4-lite :

具有轻量级,结构简单的特点,适合小批量数据、简单控制场合。不支持批量传输,读写时一次只能读写一个字(32bit)。主要用于访问一些低速外设和外设的控制。

AXI4:和AXI4-lite差不多,只是增加了一项功能就是批量传输,可以连续对一片地址进行一次性读写。也就是说具有数据读写的burst功能。

AXI4-Stream : 这是一种连续流接口,不需要地址线(很像FIFO,一直读或一直写就行)。对于这种没有地址必须有一个转换装置,列如AXI-DMA模块来实现内存映射到流的转换接口。

在zynq芯片内部,使用硬件实现了A

本文介绍了ZYNQ芯片中PS(处理系统)与PL(可编程逻辑)的互联技术——AXI协议,包括AXI-LITE、AXI4和AXI4-Stream三种总线的特性。AXI4-Stream适用于连续流数据传输,而AXI-HP和AXI-GP接口则分别用于高性能和通用传输。文中还提及了AXI-DMA、AXI-FIFO-MM2S等AXI接口IP的功能,用于不同类型的内存到PL的数据传输。

本文介绍了ZYNQ芯片中PS(处理系统)与PL(可编程逻辑)的互联技术——AXI协议,包括AXI-LITE、AXI4和AXI4-Stream三种总线的特性。AXI4-Stream适用于连续流数据传输,而AXI-HP和AXI-GP接口则分别用于高性能和通用传输。文中还提及了AXI-DMA、AXI-FIFO-MM2S等AXI接口IP的功能,用于不同类型的内存到PL的数据传输。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

7136

7136

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?