用于仪器仪表应用的低功耗容错型闪速模数转换器设计

摘要

技术的发展显著推动了电子世界向更强大方向的进步。模数转换器(ADC)被认为是将模拟信息转换为数字形式领域的先驱,是射频和混合信号设计中不可或缺的组件。本文提出了一种紧凑型基于NOR的CMOS线性可调跨导元件(NOR‐LTE)比较器和动态优先级编码器(DPE)。NOR‐LTE比较器降低了功耗和偏移误差,从而提高了整个电路设计的电源抑制比(PSRR)。动态优先级编码器减少了闪速型模数转换器(Flash ADC)所需的晶体管数量。所提出的容错型闪速ADC(FT‐FADC)架构采用Tanner EDA工具及0.25 μm CMOS技术实现。上述建议的FT‐FADC在1.5伏电源下针对500 MHz分辨率带宽(RSB)实现了3.44位有效位数(ENOB)。由于高达1.3 GS/s的采样率,其吞吐量提升了60%,同时功耗降低了47%。

1. 引言

自然发生的实时信号转换为数字码,这极大地推动了数字世界的发展。由于具有强大的功能,数据采集系统、宽带无线电接收机、多集成电路以及现代数字通信系统正变得越来越普及。然而,所有人类交互的事物,如语音、视频、音乐等,都是连续信号。模拟信号通过模数转换器(ADC)被转换为数字码。实时模拟信息被转化为数字码以提高确定性和质量。该转换过程包括采样、量化和编码。模数转换器的性能参数包括分辨率、传播时间、功耗和速度。目前存在多种类型的模数转换器发展方案。其中,闪速型ADC架构在高速条件下几乎保持恒定的分辨率,适用于将实时变化的信号转换为数字码。

电阻梯形网络(2^N)、比较器(2^N‐1)和温度计码转二进制编码器(2^N ‐1:N)是传统闪速型模数转换器中的三个主要组成部分,其受到面积需求和操作延迟的限制。比较器与由电阻链(2^N)生成的参考电压相关联,这些电阻在低分辨率下消耗更多功率且成本较高[1]。

在这方面,设计了一种高效的互补金属氧化物半导体NOR‐LTE比较器,以降低功耗并减少处理延迟。该比较器中的量化等级由参考电压设定水平决定。输入信号与此量化电平进行比较。当输入电压大于参考电压时,比较器输出高电平。比较器的这种输出模式对应于温度计码,也称为一进制编码。该码通过2^N ‐1转换为N位编码器的二进制输出。

一进制编码到二进制的编码器是闪速型模数转换器的标准组件。近年来,已在闪速型模数转换器设计中引入了偏移校准技术。该技术不再依赖高精度的实时模拟电路比较器,而是对具有近似显著偏移误差的比较器进行计算和补偿。当施加检测信号时,每个比较器的偏移量被评估并控制在模数转换器最低有效位(LSB)值以下。另一个需要解决的常见设计问题是如何使电路具备抵抗气泡误差[2]的能力。气泡误差(BE)定义为输入一进制编码中缺少的“10”。

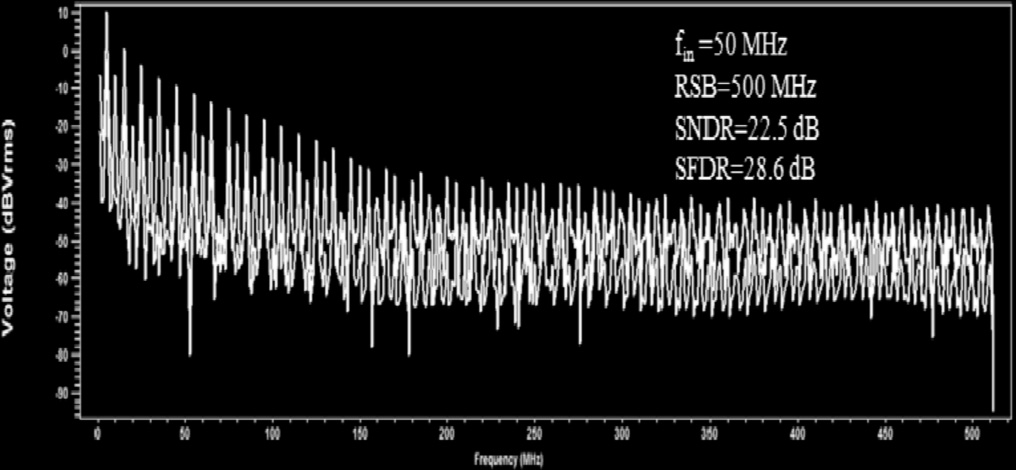

所提出的容错型闪速ADC(FT‐FADC)并非一种并行架构,而是包含NOR‐LTE比较器以及带有气泡误差校正器(BEC)的动态优先级编码器(DPE)。NOR‐LTE比较器将模拟输入信号转换为一进制编码。动态优先级编码器(DPE)通过三输入或门构成的气泡误差校正器(BEC)对冒泡错误进行校正后,从一进制编码精确生成数字输出码。所提出的4位FT‐FADC核心显示出对简单的模拟输入级进行了广泛的结构考虑,并深入探讨了模数转换器所有子模块的电路实现。根据该架构估算的结果,在输入信号频率为50兆赫、采样速率为1.3千兆采样每秒时,有效位数(ENOB)达到3.44位,信噪失真比为22.5分贝。由于分辨率带宽(RSB)为500兆赫兹,该模数转换器在1.5伏电源下功耗为2.77毫瓦,优值为每转换步骤0.25皮焦耳。

2. 相关工作

在论文[3]中,展示了对采样保持电路和连续缓冲级的深入研究,并为传输容量计算提供了数学表示。这些结果表明主导边沿速度代表了一个单元件ADC核心。该模数转换器能够在无需时间交织的情况下实现更高的采样率,使其成为CMOS技术中最快的单元件ADC。论文[4]描述了一种混合信号多位随机闪速模数转换(ADC)以及一种推测性评估仪器,作为指定采样ADC的替代方案。它提供了实际测量依赖于采用组合分析方法(抖动噪声)的高速低分辨率闪速ADC,以补偿平坦分辨率。随机仪器测量两个符号结果的平均值。基于该方法,针对多位情况进行了检验,并对最高标准和相对测量不确定度进行了评估。

在论文[5]中,该ADC架构采用两级结构。第一阶段为3位子量程结构,第二阶段为基于比较器异步二进制搜索(CABS)的5位时间交织4通道结构。采样与保持电路和电容式数模转换器相结合,用于执行子量程操作的采样。同时采用了线性校正方法,以实现高效节能和高速操作。采样网络具有误差减小技术,可缓解自举开关的时钟馈通问题。通过内部生成的参考信号调节比较器偏移,并利用过采样通道实现该功能。

固有比较器偏移以及工艺变化引起的不平衡问题被用作参考电平源,且采用递归方式以获得期望分辨率。为了计算基于数字误差校正逻辑的闪速型模数转换器架构中ADC功耗的下限[6]。高分辨率ADC的功耗急剧上升,而自动化是分辨率受限器件的制约因素。

模数转换器(ADC)[7]的设计可根据链路调制格式(2PAM/4PAM)和链路损耗灵活实现节能。比较器可随着折叠级阶段单独启用或禁用,其中最高有效位(MSB)由一位折叠级确定,最低有效位(LSB)由五位闪速模数转换器确定。本文[8]提出了一种高速截断电压CMOS闪速模数转换器(ADC)的优化设计。该设计规格利用了针对不同功能模块的优化步骤,并介绍了数字误差校正技术。

卷积元件与互补金属氧化物半导体结合使用,在功耗和面积方面的性能提升令人印象深刻。卷积元件[9]被用作互补金属氧化物半导体电路的替代信息。一种基于电流感应的出色开关机制——畴壁运动,能够确保降低功耗、提高面积效率,并实现高速电路,与其他互补金属氧化物半导体模数转换器形成对比。为了同时实现更快的性能和降低功耗,采用二分查找和闪速型模数转换器重构ADC架构,以优化转换延迟[10]。

论文[11]中提出了一种针对1.75吉萨每秒模数转换器采用5位动态折叠方法。这两种动态折叠技术可减少比较器数量并简化编码过程。文中实现了固有参考电压比较器,进一步降低了功耗。高阶模数转换器设计包含基于源极跟随器[12]的自举采样保持电路,以减小输入失调误差和噪声,并提高带宽。为了有效提升模数转换器分辨率,本文还阐述了在最大输入频率下采用四相时钟作用于交错通道的方法。通过传输门从奈奎斯特频率输入时钟推导出四相时钟方程,并经由简单的占空比调整,获得精确的时序偏置维度。

一种更便宜的比较器偏移数字校准技术在采用流水线结构的模数转换器(ADC)中实现。比较器通过单冗余策略来抵消超过大部分级间最低有效位裕度的误差是合理的,因此确定了比较器的设计要求,同时适用于低功耗、高性能和低输入电容的应用场景。该技术[13]还使得电路设计需要带有放大器的流水线队列,因此输出波动和驱动能力无疑会降低。

本文提出了一种重组的混合信号处理(MSP)方案,用于快速脉冲压缩雷达(PCR)。混合信号处理(MSP)设计技术结合了分析与自适应机制,以提升PCR接收机的响应能力。通过采用自适应带宽PCR,提高了低功耗雷达系统的有效作用距离。在采样保持电路中,采用通道时间交错方案使放大器的预定运行速度提高了一倍。具有双输入对的转换级和共用运算放大器在无需额外串联开关的情况下放大每个通道信号,同时减小了各通道之间的增益、带宽和失调差异。具有50%占空比的低抖动检测时钟显著提升了宽带输入信号的动态响应。闪存型模数转换器(Flash ADC)采用前置放大器类型差分放大器用于频繁处理双通道输出。

通过高效的功率设计,4路交错ADC配置可实现无与伦比的适应性以及更低的预期亚稳态错误率。该配置包含一对可变增益放大器(VGA),用于驱动6位比较器阵列,并采用基于华莱士树的加法器作为热码到二进制编码器[16]。已提出一种5位流水线结构ADC的设计方案,适用于低电平信号所需的固态有源像素传感器[17]。其典型直流功耗为1.7毫瓦,预计动态范围为25分贝。

在本文中,渐进偏置伪差分THA缓冲器的支持实现了更大的输出摆幅、更高的电压增益以及更快的建立速度。通过调节环路,进一步提高了ADC线性度和低转换能量(1.4皮焦耳/转换步)。由于具有24吉采样每秒的高采样率,该模数转换器在结合中等时间交错后可适用于超高速架构。这是一种微小的努力且低功耗(0.4瓦)的数字互补金属氧化物半导体创新。快速模数转换器和基于时间数字转换器(TDC)的游标结构采用流水线化设计以加快转换速度。通过使用电荷导向放大器和电平调节模块实现的低功耗残差传输被添加到电荷导向放大器的输出级,以在工艺、电压和温度变化下平衡输出常规电平。

比较器采用IDUDGMOS器件[21],以使模数转换器在射频范围的高精度应用中实现低功耗、可编程和面积优化。该模型的最高传输速率为1吉赫兹,功耗为15 μW。通过调整晶体管尺寸,高效设计了带有反相器的四晶体管CMOS跨导元件[22],以生成内部参考电压。结合CMOS‐LTE和多路复用编码器的闪速型模数转换器,采样频率为1998兆赫兹,在1.8伏电源电压下总功耗为0.28毫瓦。基于量子电压(QV)比较器的闪速ADC[23]通过有意识且持续地调整差分晶体管对的晶体管尺寸来提升信息并平衡补偿电压。与时间交织量化闪速ADC相比,其在6位情况下可节省58.1%的功耗,在8位情况下可节省62.1%的功耗。

一种采用一维到二维转换的高性能大规模优先级编码器(PE)的可适应性设计。通过该设计,大幅改善了在大尺寸PE情况下性能下降的问题,每当PE尺寸加倍时,频率仅逐渐降低11%[24]。高速流水线型ADC[25]采用两相非重叠时钟与180°相移以及开关电容电路实现,利用互补金属氧化物半导体的电荷存储能力,实现了精确的信号处理和每时钟周期单个样本的高吞吐量。通过比较器冗余设计以及基于传输门的全加器应用于闪速型模数转换器,实现在2.5 GS/s速度下的整体能效,并实现低功耗损耗,仅为30 mW[26]。

该论文[27]研究了静态和动态比较器,并进一步采用了改进的模数转换器结构。动态比较器在0.055 μ伏特范围内具有优异的性能,且非线性较低,错误减少,驱动力减弱,并且对于任何高速工作的设备来说,逐步合理的结构选择。使用在此模型中设计的双通道F‐ADC的直接子采样接收机[28]以提高能效效率而不降低系统性能。对于限制

| 带气泡的一元码错误 (B15 到 B0) | 泡错误校正输出 (I15 到 I0) | Gray码 (G3 到 G0) | DPE输出 (D3 到 D0) |

|---|---|---|---|

| 0000000000000001 | 0000000000000001 | 0000 | 0000 |

| 0000000000000011 | 0000000000000011 | 0001 | 0001 |

| 0000000000000111 | 0000000000000111 | 0011 | 0010 |

| 0000000000001111 | 0000000000001111 | 0010 | 0011 |

| 0000000000011110 | 0000000000011111 | 0110 | 0100 |

| 0000000000111111 | 0000000000111111 | 0111 | 0101 |

| 0000000001111111 | 0000000001111111 | 0101 | 0110 |

| 0000000011111011 | 0000000011111111 | 0100 | 0111 |

| 0000000111111011 | 0000000111111111 | 1100 | 1000 |

| 0000001111101111 | 0000001111111111 | 1101 | 1001 |

| 0000011111101111 | 0000011111111111 | 1111 | 1010 |

| 0000110111101111 | 0000111111111111 | 1110 | 1011 |

| 0001110111111111 | 0001111111111111 | 1010 | 1100 |

| 0011110111111111 | 0011111111111111 | 1011 | 1101 |

| 0111110111111111 | 0111111111111111 | 1001 | 1110 |

| 1111111111111111 | 1111111111111111 | 1000 | 1111 |

表1 气泡错误校正的真值表。

| 各种比较器 | 功耗 (μW) | 处理延迟 (Sec) |

|---|---|---|

| 量化差分比较器(QDC) | 79.64 | 3.75 |

| 带反相器的开环比较器(OLC‐I) | 52.14 | 2.20 |

| CMOS‐LTE比较器 | 46.36 | 2.03 |

| NOR‐LTE比较器 | 30.15 | 1.43 |

表2 各种比较器技术的功耗和处理延迟调查。

3. 提出的容错闪速ADC(FT‐FADC)

为了实现高速和低功耗的容错型闪速ADC(FT‐FADC),本文提出并设计了一种容错型闪速ADC。该设计适用于射频和混合信号应用。

FT‐FADC的模块表示如图1(a)所示。FT‐FADC包含三个功能模块阶段。第一阶段为NOR‐LTE比较器,它将模拟输入信号转换为一进制编码(温度计码),并减小偏移误差。第二阶段是气泡误差校正器(BEC),采用三输入或门设计,用于纠正一进制编码中出现的气泡。静态或动态比较器误差会导致一进制编码中产生气泡。在纠正气泡后,通过动态优先级编码器(DPE)将一进制编码转换为二进制码,DPE是该模数转换器的最后一个阶段。所提出的容错型闪速ADC(FT‐FADC)的设计流程以流程图形式展示,如图1(b)所示。

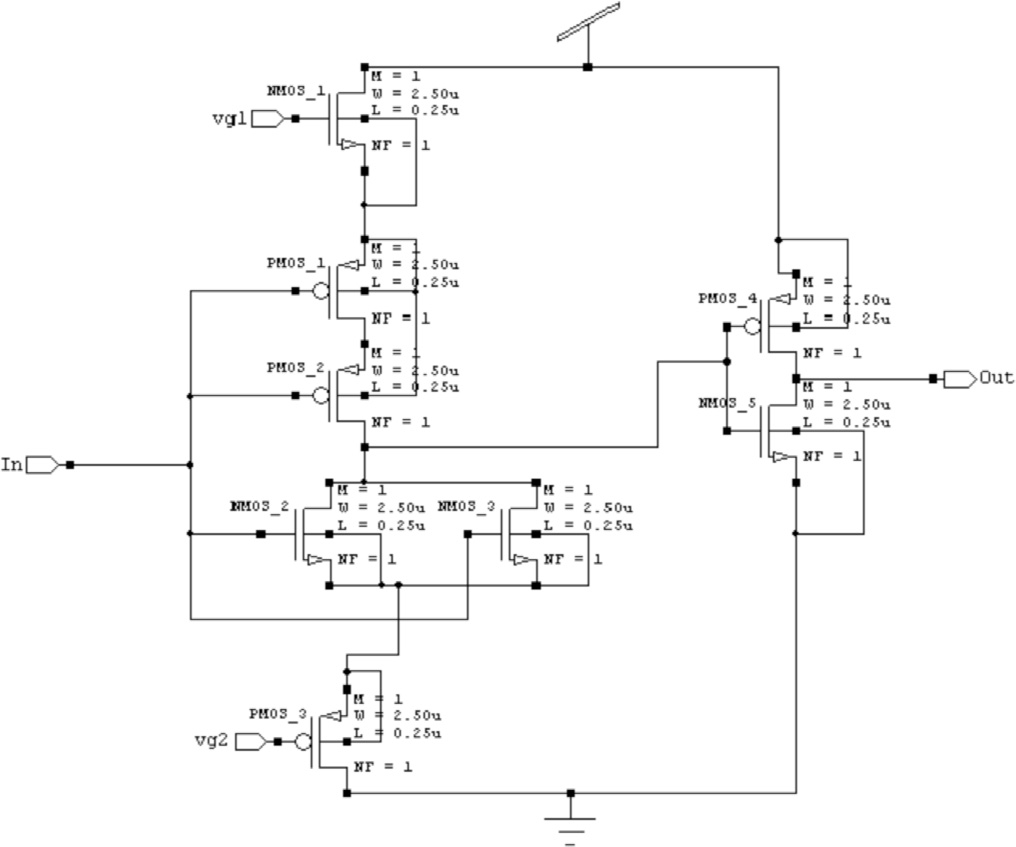

3.1. NOR‐LTE比较器

NOR‐LTE比较器研究输入电压(Vin)与固有参考电压(Vref)之间实时信号的对比。如果Vin高于Vref,则输出为高,否则输出为低。该NOR‐LTE单元的所有晶体管尺寸在该结构中均不可区分,其中Vg1和Vg4为恒定电压。为了增强比较器的电势强度并减小偏移误差,将NOR‐LTE的输出连接至CMOS反相器。N位闪速型模数转换器需要2^N ‐1个比较器来设计4位闪速ADC。NOR‐LTE比较器的原理结构如图2所示。

通过使用CMOS NOR‐LTE比较器,与传统CMOS比较器相比,我们能够在输出端获得更好的线性度并减小偏移误差。该比较器根据其晶体管尺寸将切换电压(Vm)在内部固定为固有的参考电压。反相器的切换电压(Vm)可通过公式(1)–(4)进行数学计算。

$$ Vm = \frac{r \cdot Vdd - |Vtp| + Vtn}{(1 + r)} $$ (1)

$$ r = \sqrt{\frac{K_p}{K_n}} $$ (2)

NOR‐LTE比较器的切换电压根据PMOS和NMOS晶体管的宽长比而变化。

$$ K_n = \left(\frac{W}{L}\right) n \cdot \mu_n \cdot C {ox} $$ (3)

$$ K_p = \left(\frac{W}{L}\right) p \cdot \mu_p \cdot C {ox} $$ (4)

其中Vm是切换电压。其中r是Kn与Kp比值的平方根。Vdd是电源电压。Vtn是NMOS晶体管的阈值电压。Vtp是PMOS晶体管的阈值电压。μn是NMOS晶体管的迁移率。μp是PMOS晶体管的迁移率。(W/L)n是NMOS晶体管的宽长比。(W/L)p是PMOS晶体管的宽长比。Cox是单位面积栅氧化层电容。

3.2. 动态优先级编码器(DPE)

16到4动态优先级编码器(DPE)的框图如图3所示。DPE的原理图由四个输入的或门CMOS晶体管逻辑构成。16 × 4优先级编码器通过使用两个 8 × 3优先级编码器设计而成,与传统方法相比减少了20%的晶体管数量。动态优先级编码器可将并行二进制输入压缩为较少数量的输出,并生成基于实际数字二进制表示的输出。编码器中的最高优先级通常用于调节中断请求。当同时向编码器提供两个或更多输入时,具有最高优先级的输入优先处理。相较于现有的胖树编码器、基于多路复用器的编码器和优先级编码器,动态优先级编码器更适用于实现高速性能。

3.3. 气泡误差校正器(BEC)

如果一进制编码中有一个或多个无效位,则称为冒泡错误。由于逻辑电平可能被数字门误解释,以及静态/动态比较器误差会导致一进制编码中出现气泡。此外,比较器之间的源偏移电压差异大于1 LSB时也会引入冒泡错误。根据无效位的数量,冒泡错误的存在范围从一阶到n阶。

所提出的BEC包含四阶气泡误差校正方案。第4阶气泡误差校正器的示意图如图4所示。另一个称为亚稳态的因素出现在比较器的数字输出中,表现为模糊状态(既非1也非0)。这种亚稳态可以通过允许多次再生来减弱。格雷码编码策略适用于减少亚稳态,因为它允许每次仅发生单比特变化。因此,比较器输出首先转换为格雷码,然后在需要时再解码为二进制。表1展示了冒泡错误校正的真值表。从该表中,B15到B0表示带气泡的一元码,而I15到I0表示泡错误校正后的输出。D3到D0是动态优先级编码器的二进制码输出,由格雷码G3到G0转换而来。第一、第二、第三和第四阶误差校正是通过使用气泡误差校正电路实现的。

3.4. PSRR测量

电源抑制比(PSRR)主要是模数转换器中被忽视的决定因素之一。系统的整体噪声性能和精度由PSRR定义。此外,任何电路的PSRR都是其对电源变化抗干扰能力的一部分。高PSRR意味着对电源变化具有更强的抑制能力。模数转换器的PSRR是电源电压变化与输出电压变化之比,其中输出电压对应于输出计数值。因此,闪速型模数转换器的PSRR公式(5)如下所示。

$$ PSRR (dB) = 20 \log \frac{\text{Change in supply voltage}}{\text{Change in output voltage}} $$ (5)

| 编码方案 | 晶体管数量 | 功耗 (W) |

|—|—|—|

| 胖树编码器 | 156 | 1.544 |

| 基于多路复用器的编码器 | 154 | 1.062 |

| 优先级编码器 | 104 | 0.860 |

| 动态优先级编码器 | 84 | 0.402 |

表3 各种编码方案的晶体管数量和功耗分析。

| 技术 | 位数 | 功耗 (mW) | ADC电压分辨率 (v) | 吞吐量(兆赫兹) | 可靠性 (%) |

|---|---|---|---|---|---|

| QDC ADC | 1 | 8.18 | 5 | 55.5 | 76 |

| OLC‐I ADC | 2 | 7.62 | 2.5 | 48.4 | 85 |

| 互补金属氧化物半导体‐LTE ADC | 3 | 5.24 | 1.25 | 24.6 | 92 |

| NOR‐LTE ADC | 4 | 2.77 | 0.625 | 9.8 | 98 |

表4 各种模数转换器的功耗、电压分辨率和可靠性分析比较。

差分非线性和 (b) 积分非线性(b) 在输入频率 = 50兆赫兹时。)

| 规格 | 测量值 |

|---|---|

| 工艺技术(纳米) | 250 |

| 处理延迟(秒) | 3.97 |

| 晶体管数量 | 204 |

| 速度(吉样本每秒) | 1.3 |

| 吞吐量(兆赫) | 9.8 |

| 功耗(毫瓦) | 2.77 |

| 参考采样带宽(兆赫) | 500 |

| 信噪失真比(dB) | 22.5 |

| 无杂散动态范围(dB) | 28.6 |

| 差分非线性/积分非线性 (± 最低有效位(LSB)) | 1/1.5 |

| 品质因数( pJ/转换步) | 0.25 |

| ENOB | 3.44 |

| 能效性能积(FDP)(pJ · 纳秒/转换步(ns/conv.‐step)) | 0.192 |

表5 FT‐FADC模型的性能指标。

4. 结果与讨论

使用S‐Edit(Tanner EDA工具)在0.25 μm CMOS技术下实现了4位 FT‐FADC的原理图设计,并通过T‐Spice进行仿真。输出波形由W‐edit获得。

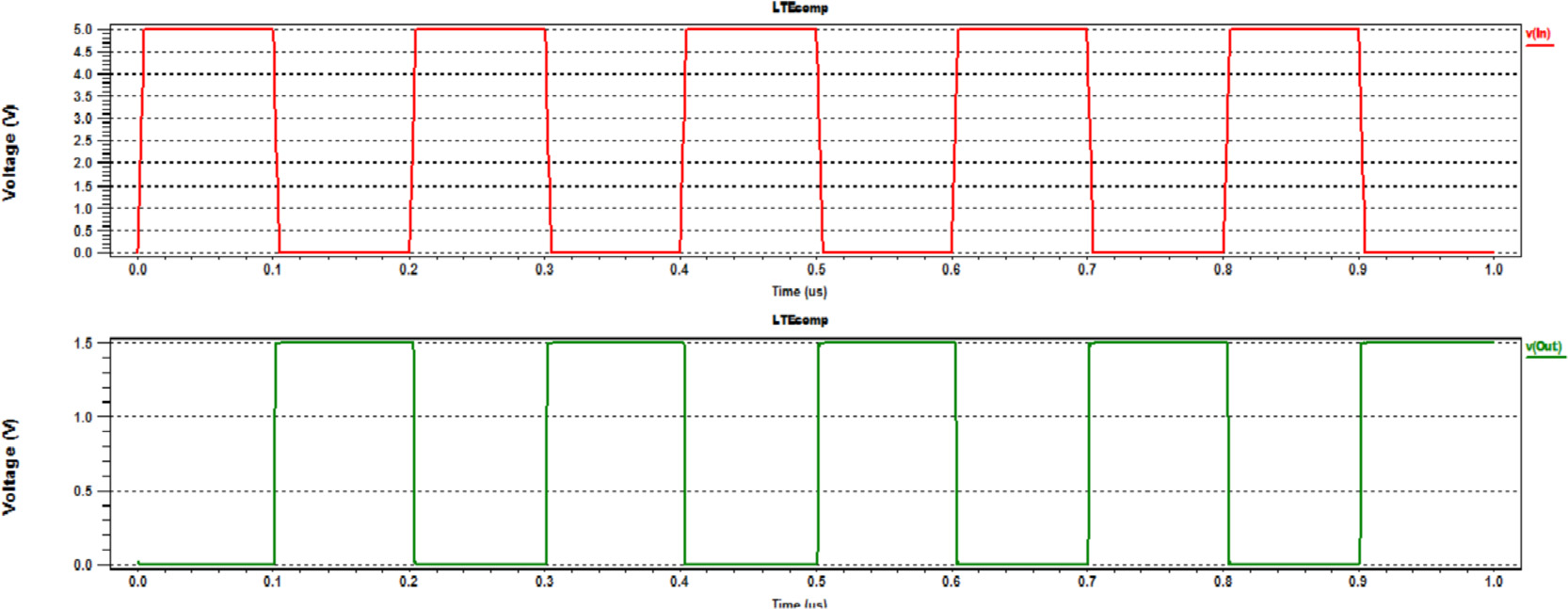

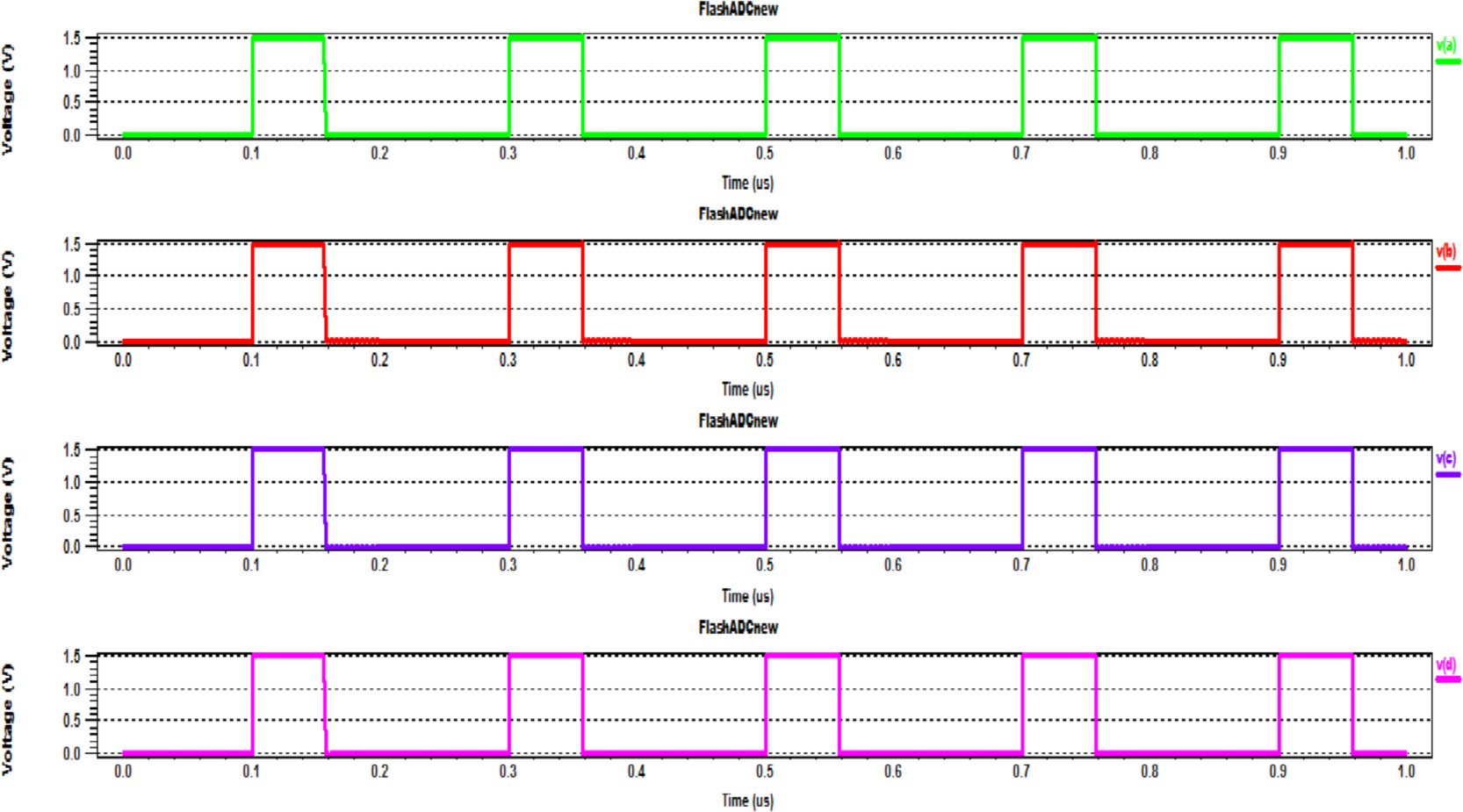

4.1. NOR‐LTE比较器的仿真结果

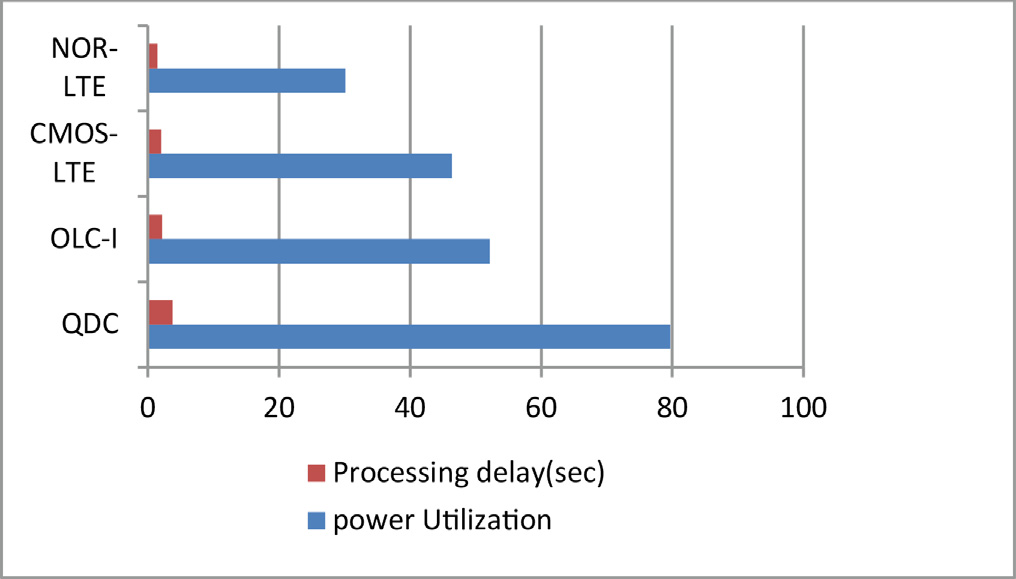

表2说明了不同比较器技术的功耗和处理延迟调查。从该表可以看出,所提出的NOR‐LTE比较器相较于QDC、OLC‐I和CMOS‐LTE比较器分别降低了62.14%、42.17%和34.96%的功耗。NOR‐LTE比较器的图形响应如图5所示。不同比较器技术的功耗与处理延迟对比图表[22,23,25]如图6所示。从该图中可以观察到,用于FT‐FADC的预期比较器结构相较于QDC、OLC‐I和CMOS‐LTE比较器分别将处理延迟降低了61.86%、35%和29.55%。

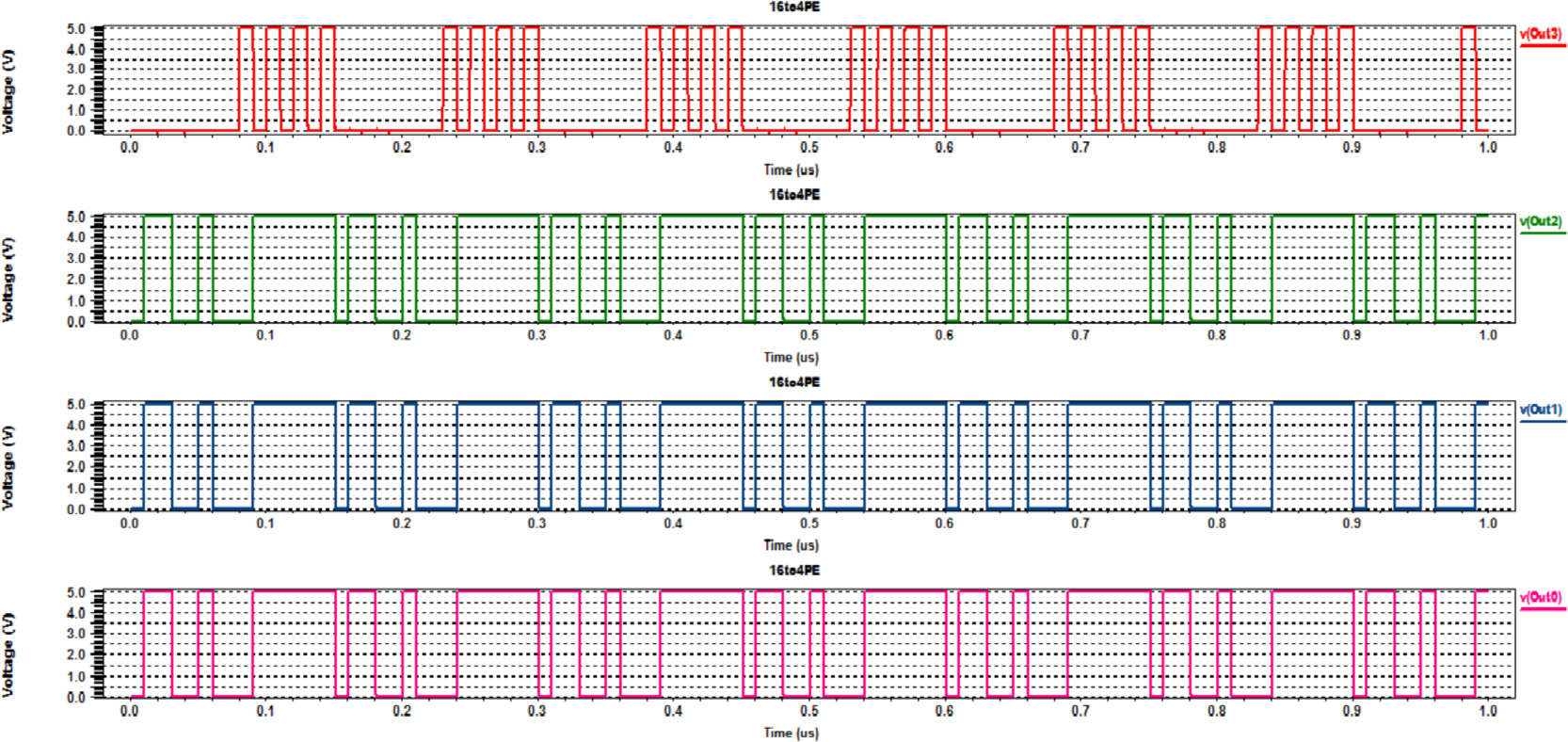

4.2. 动态优先级编码器的仿真结果

各种编码方案的晶体管数量和功耗分析[24,25,27]如表3所示。从该表可以看出,所提出的动态优先级编码器相比胖树编码器、基于多路复用器的编码器和优先级编码器,芯片面积分别减少了46.15%、45.4% 和19.2%,功耗分别降低了73.96%、62.14%和53.25%。图7显示了16到4动态优先级编码器的仿真结果。

4.3. 容错型闪存ADC的仿真结果

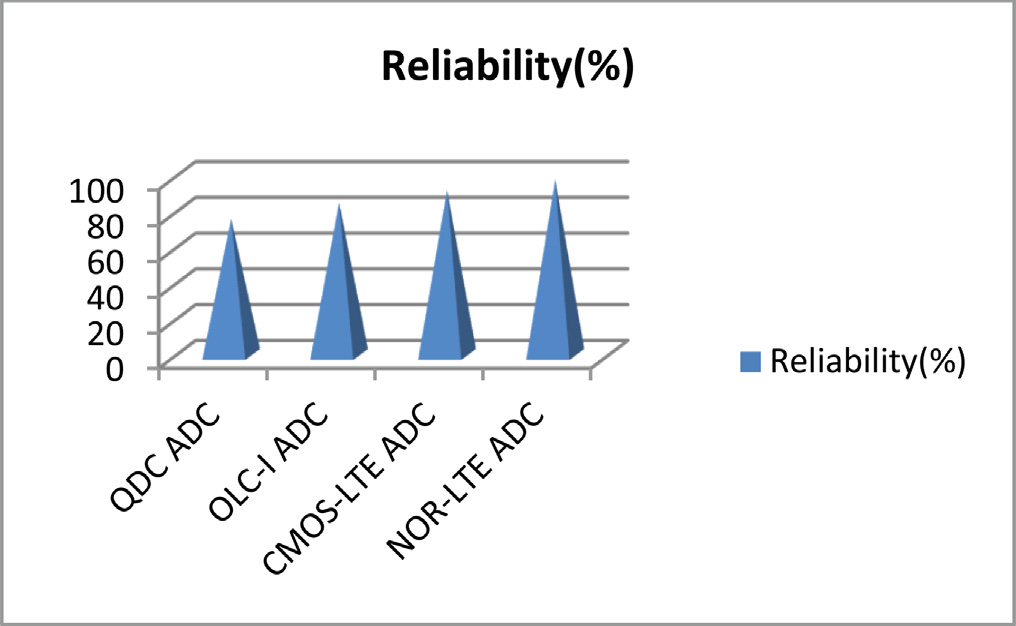

容错型闪速ADC(FT‐FADC)的仿真结果如图8所示,各种模数转换器的功耗、电压分辨率和可靠性分析比较记录在表4中。从该表可知,与QDC ADC、OLC‐I ADC和CMOS‐LTE ADC相比,FT‐FADC整体功耗分别降低了66.13%、63.64%和47.13%,同时通过将吞吐量分别提高82.3%、79.7%和60.1%来提升速度。图9展示了基于功耗和吞吐量的不同类型模数转换器的性能分析。所提出的FT‐FADC可校正最高至四阶的冒泡错误,并实现98%的可靠性。根据这些评估结果可以看出,推荐的闪速型模数转换器在可靠性方面优于其他现有的闪存型模数转换器。可靠性分析的对比图表如图10所示。从该图表可知,与现有技术QDC ADC、OLC‐I ADC和CMOS‐LTE ADC相比,该模数转换器的可靠性分别提高了28.94%、15.29%和6.5%。

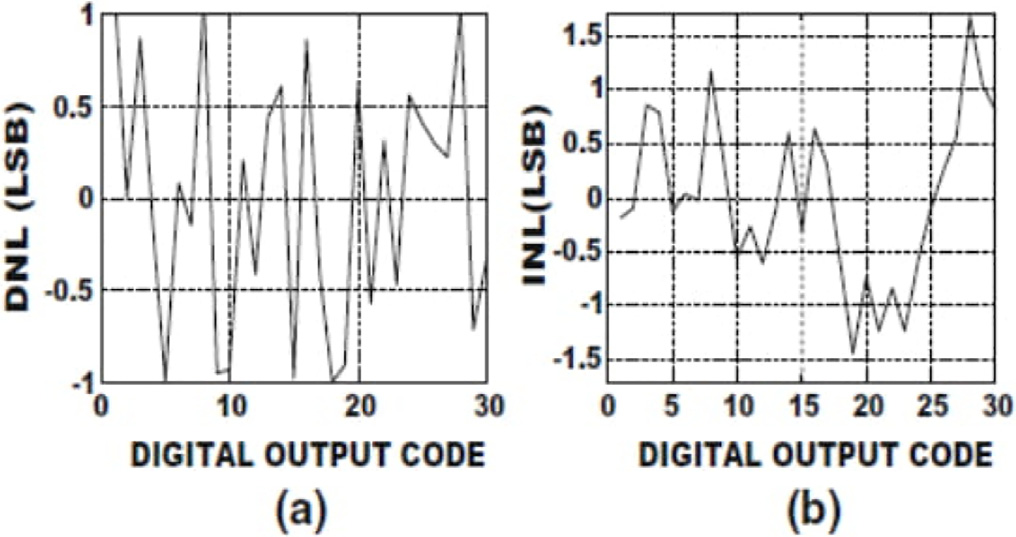

在500 MHz分辨率带宽(RSB)和50 MHz输入频率下获取了FT‐FADC的微分非线性(DNL)和积分非线性(INL)结果。图11(a和b)展示了峰值DNL和INL分别为 ±1和 ±1.5 最低有效位(LSB)。测得的无杂散动态范围(SFDR)为满量程(FS)28.6 分贝,受限于第十次谐波,通过快速傅里叶变换(FFT)得到的信噪失真比(SNDR)为22.5 分贝,如图12所示。在1.3 千兆采样每秒下,该模数转换器实现3.44 有效位数(ENOB),采用1.5 伏特电源供电,功耗为2.77毫瓦。

优值(FOM)定义为

$$ FOM = \frac{Power}{2 \cdot RSB \cdot 2^{ENOB}} $$ (6)

以这种方式,优值(FOM)通过公式(6)确定为0.25 pJ/转换步长,FT‐FADC模型的性能指标记录在表5中。FDP的结果提升了能效,而没有实质牺牲速度性能。利用FDP项,可以清晰评估电路在能效与速度性能之间的权衡。考虑到转换延迟,所设计的FDP项表明,FT‐FADC达到了0.192 pJ · 纳秒/转换步(ns/conv.‐step)。

| 速度(GS/s) | 供电 (v) | 功耗 (mW) | 分辨率 (位) | 工艺 (nm) | 参考采样带宽 (兆赫) | SNDR (dB) | SFDR (dB) | 差分非线性/积分非线性 (±最低有效位(LSB)) | 品质因数 (pJ/Conv‐step) |

|---|---|---|---|---|---|---|---|---|---|

| 1.3 | 1.5 | 2.77 | 4 | 250 | 500 | 22.5 | 28.6 | 1/1.5 | 0.25 |

| 0.2 | 0.5 | 2.1 | 7 | 90 | 200 | 38 | 50 | 0.95/0.97 | 0.19 |

| 1.1 | 1.2 | 13.4 | 8 | 130 | 491 | 48.15 | 61.59 | – | 0.064 |

| 1.3 | 2.5 | 600 | 6 | 250 | 500 | 30 | 41 | 0.8/0.42 | – |

| 1.75 | 1 | 2.2 | 5 | 90 | 878 | 25.8 | 40 | 0.3/0.3 | 0.05 |

| 0.2 | 1.8 | 54 | 10 | 180 | – | 52.8 | 60.4 | 0.62/0.99 | 1.11 |

| 10.3 | 0.9 | 242 | 6 | 40 | 3500–6000 | 34 | – | 0.5/0.4 | 0.49–0.84 |

| 0.9 | 1 | 3.5 | 8 | 65 | 900 | 41.9 | 49.5 | 0.7/0.9 | 0.037 |

| 2.5 | 1.2 | 30.2 | 6 | 90 | 300 | 25.5 | 31.3 | 0.48/0.54 | 3.28 |

| 2.5 | 1 | 2.4 | 6 | 45 | 2500 | 57.7 | 61 | 0.2/0.4 | 0.015 |

表6 所提出的模数转换器与其他已公布的闪存型模数转换器(Flash ADC)的性能比较。

结果表明,所设计的闪速型模数转换器在速度、功耗、参考采样带宽(RSB)和品质因数(FOM)之间实现了优异的独特性能和更优的权衡。本工作相比参考文献功耗更低,为2.77毫瓦,且分辨率带宽(RSB)达到500兆赫,优于[5,8,15,16,20,26]和作者[11,16,20,27]。

结论

建议并采用0.25 μ微米CMOS工艺实现了一款4位低功耗容错型闪存ADC,可在1.5伏电源下工作。通过使用动态优先级编码器(DPE)和NOR‐LTE比较器,该设计实现了最高1.3千兆采样每秒的转换速率,参考采样带宽为500兆赫兹。与QDC、OLC‐I和CMOS‐LTE比较器相比,NOR‐LTE比较器分别降低了62.14%、42.17%和34.96%的功耗,并将处理延迟分别减少了61.8%、35%和29.5%。FT‐FADC相较于QDC ADC、OLC‐I ADC和CMOS‐LTE ADC的整体功耗分别降低了66.13%、63.64%和47.13%。经测试,该FT‐FADC具有较低的优值0.25pJ/转换步,与参考文献[15,16,26]相比表现优异。所提出的容错闪存型模数转换器的电源抑制比为60分贝。

908

908

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?