阻塞和非阻塞是FPGA硬件编程中需要了解的一个概念,绝大部分时候,因为非阻塞的方式更加符合时序逻辑设计的思想,有利于时钟和信号的同步,更加有利于时序收敛,所以除非特殊情况,尽量采用非阻塞方式。

一,非阻塞代码

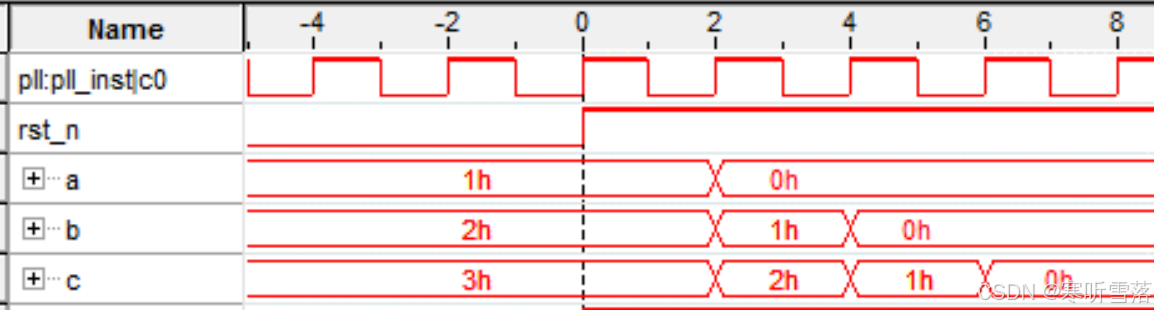

符号“<=”用于非阻塞赋值,非阻塞赋值是由时钟节拍决定,在时钟上升到来时,执行赋值语句右边,然后将 begin-end之间的所有赋值语句同时赋值到赋值语句的左边,注意:是begin—end之间的所有语句,非阻塞赋值,A和B和C是同时被赋值的,具体是说在时钟的上升沿来的时刻,A和B和C同时被置1,一起执行且一个时钟只执行一次,属于并行执行语句。

always@(posedge clk or negedge rst n)

begin

if(!rst n)

begin

a <= 1;

b <= 2;

c <= 3;

end

else

begin

a <= 0:

b <=

本文介绍了FPGA硬件编程中的阻塞和非阻塞赋值概念,强调非阻塞赋值在时序逻辑设计中的优势,并通过实例分析两者在时序上的差异。非阻塞赋值在时钟上升沿后同时更新,而阻塞赋值存在先后顺序,可能导致时序违规。在高速设计中,这种延迟不容忽视。

本文介绍了FPGA硬件编程中的阻塞和非阻塞赋值概念,强调非阻塞赋值在时序逻辑设计中的优势,并通过实例分析两者在时序上的差异。非阻塞赋值在时钟上升沿后同时更新,而阻塞赋值存在先后顺序,可能导致时序违规。在高速设计中,这种延迟不容忽视。

订阅专栏 解锁全文

订阅专栏 解锁全文

3502

3502

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?