阻塞赋值

阻塞赋值符号为“=”,对应电路结构常与触发沿无关,之与输入电平有关。在执行阻塞赋值时不允许有其他语句执行,知道现执行的赋值完成才会允许下一条语句执行。

串行块-----begin-end中,阻塞赋值语句为顺序执行。

例如:

begin

a=b+1;

b=a+1;

c=a+1;

end

在上述代码中先执行b+1赋值给a后再执行a+1赋值给b以此类推。

非阻塞赋值

非阻塞赋值符号为“<=”,对应电路结构常与触发沿有关,只有在触发沿时刻才可以进行非阻塞赋值。

非阻塞赋值过程为:(1)赋值开始时刻计算赋值号右边赋值语句

(2)赋值结束时刻更新左边语句

在非阻塞语句执行过程中允许其他语句执行。

非阻塞赋值只能用于对寄存器类型变量进行赋值,因此只能用于initial和always块中,不可用于assign中。例如:

a=1,b=2,c=3

begin

a=b+1;

b=a+1;

c=a-1;

end

计算结果为:a=3,b=2,c=0

Verliog HDL代码验证

阻塞赋值:

module block_and_no_block

(

input wire sys_rst_n,

input wire sys_clk ,

input wire [1:0] in ,

output reg [1:0] out

);

reg [1:0] in_reg;

always@(posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

begin

in_reg = 2'b0;

out = 2'b0;

end

else

begin

in_reg = in;

out = in_reg;

end

endmodule

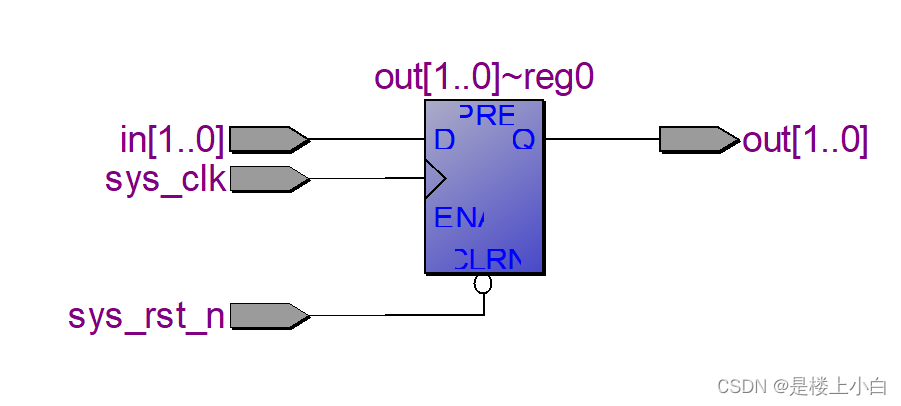

RTL视图

阻塞赋值可综合出的为一个寄存器

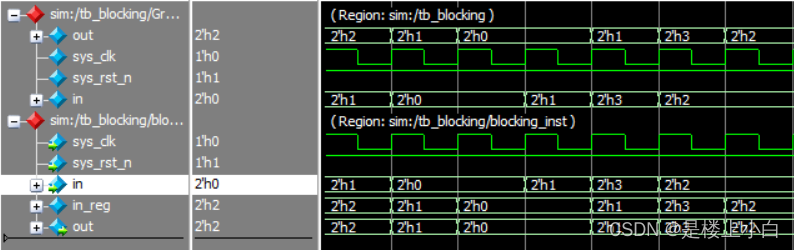

modelsim仿真波形

由仿真波形可以清晰的看出当阻塞赋值右边数值改变时左边立即改变

非阻塞赋值:

module block_and_no_block

(

input wire sys_rst_n,

input wire sys_clk ,

input wire [1:0] in ,

output reg [1:0] out

);

reg [1:0] in_reg;

always@(posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

begin

in_reg <= 2'b0;

out <= 2'b0;

end

else

begin

in_reg <= in;

out <= in_reg;

end

endmodule

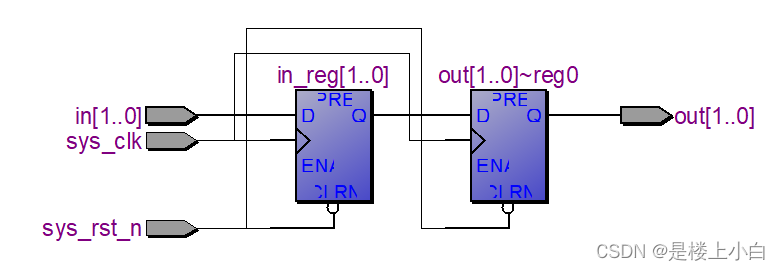

RTL视图

非阻塞赋值可综合出的为两个寄存器

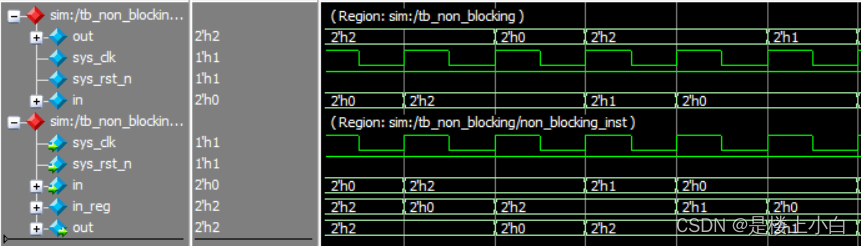

modelsim仿真波形

由仿真波形可知非阻塞赋值的有效时钟沿到来一次赋值一次

1512

1512

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?