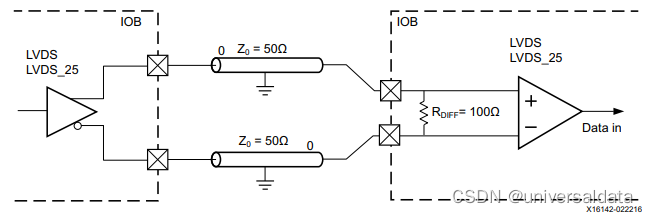

在调试FMC-704 3Gsps采集回放卡时,发现在K7平台上调试完成后,放到KU平台上工作不正常。经测试发现,KU的FPGA接收HMC7044送过来的Globle_clk "300MHz" 时钟不正确。把HMC7044输出的该时钟更改为150MHz,则KU FPGA能正常接收。这就说明是信号幅度和匹配问题。后通过打开KU IBUFDS的差分终结电阻解决。

大家经常使用的KU085、KU115中,使用了IBUFDS来接收差分信号。但是我们发现,该源语没有终结电阻选项了。

IBUFDS IBUFDS_inst (

.O(O), // 1-bit output: Buffer output

.I(I), // 1-bit input: Diff_p buffer input (connect directly to top-level port)

.IB(IB) // 1-bit input: Diff_n buffer input (connect directly to top-level port)

);

根据xilinx的官方的资料,UltraScale的器件是支持100欧的差分终结电阻的。

该差分Rdiff可以在I/O Ports设置界面下开,也可以在XDC文件中进行设置。

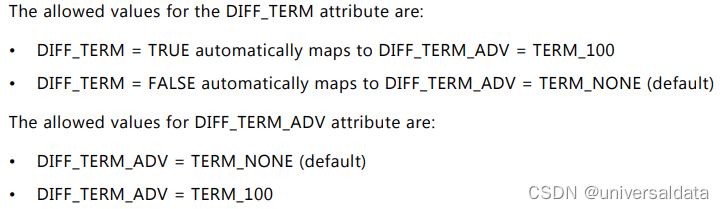

Differential termination can either be invoked using the DIFF_TERM or DIFF_TERM_ADV attributes. DIFF_TERM is used if specified in the instantiated primitive. DIFF_TERM_ADV is used if specified in the XDC constraints file. DIFF_TERM values specified in the instantiated primitive gets translated to the corresponding DIFF_TERM_ADV setting in the XDC file.

The DIFF_TERM_ADV attribute uses the following syntax in the XDC file:

set_property DIFF_TERM_ADV value [get_ports port_name]

实际项目中,由于输入的差分信号时P端和N端,我们只需要设置P端即可。

set_property DIFF_TERM_ADV TERM_100 [get_ports {FMC_CLK_M2C_P[0]}]

2868

2868

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?