在FPGA芯片设计公司中,硬件开发负责FPGA芯片的设计(电路,版图,后端),软件负责FPGA 的 EDA软件的设计(综合,实现,下载)。还有一个部门是生产测试中心,生产测试,对于刚涉足制造业的我,比较陌生,它实际上是有别于软件研发的非常重要的部门,它在其中起到什么作用呢?

首先,它的职责一定是贯穿整个芯片设计、验证、生产和交付的全流程的。核心职责在于保证设计芯片质量、控制量产芯片质量,并提供客户支持,它是FPGA芯片设计公司成功运作的关键环节之一。

对芯片的封装,测试和量产进行交付,应该要建立标准化,模块化的测试体系。建立标准化的仿真流程。确保测试的完备性和准确性,以确保芯片的功能,性能。确保可以和硬件,软件,市场协同工作,以保证芯片研发和销售。

这听起来是非常理论化的说明,具体会做哪些事情,好像一件也没说。

在仔细看具体要做什么之前,既然说到测试,首先,我们先看看芯片都要测试些什么?

一:测试什么?

站在通用的集成电路芯片角度下,测试主要集中在WAT,CP,FT,SLT几个环节。

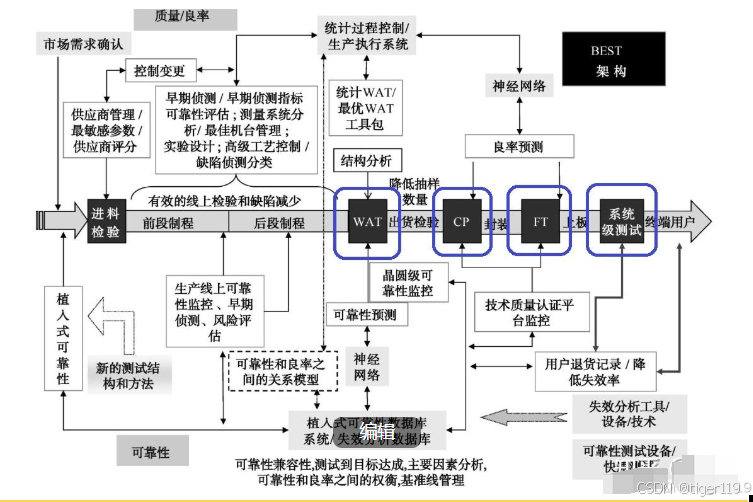

如下图:

这是一个芯片生产和测试流程的综合框架,展示了从市场需求确认到芯片量产测试的各个环节。

1.1:WAT

WAT 是英文 Wafer Acceptance Test 的缩写,意思是晶圆接受测试,业界也称 WAT 为工艺控制监测(Process Control Monitor,PCM)。

WAT 是在晶圆产品流片结束之后和品质检验之前,测量特定测试结构的电性参数。WAT 的目的是通过测试晶圆上特定测试结构的电性参数,检测每片晶圆产品的工艺情况,评估半导体制造过程的质量和稳定性,判断晶圆产品是否符合该工艺技术平台的电性规格要求。WAT 数据可以作为晶圆产品交货的质量凭证,另外 WAT 数据还可以反映生产线的实际生产情况,通过收集和分析 WAT 数据可以监测生产线的情况,也可以判断生产线变化的趋势,对可能发生的情况进行预警。

WAT测试由晶圆制造工厂执行,但设计方在流片前需要向工厂提供工艺规格要求(Process Design Kit,PDK),这些规格直接影响WAT的测试标准。

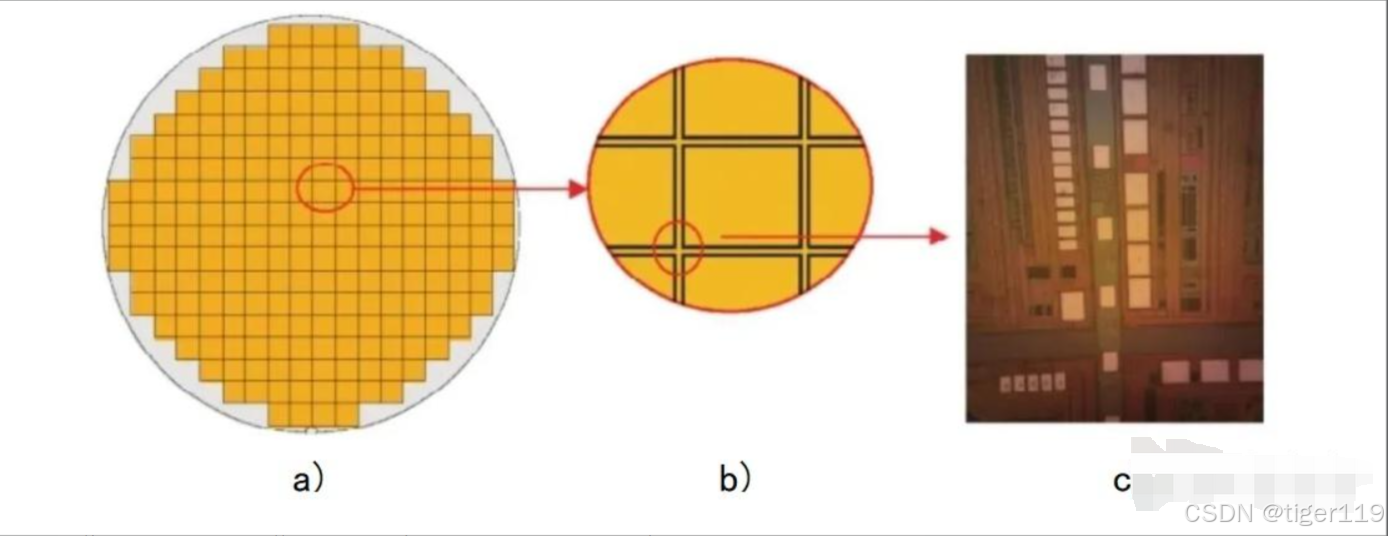

晶圆上用于收集 WAT 数据的测试结构称为 WAT 测试结构(WAT testkey)。WAT 测试结构并不是设计在实际产品芯片内部的,因为设计在芯片内部要占用额外的芯片面积,而额外的芯片面积会增加芯片的成本,芯片代工厂仅仅把 WAT 测试结构设计在晶圆上芯片(die)之间的划片槽(Scribe Line)

如下是WAT的测试项:

因为WAT测试主要是晶圆制造工厂的事情,所以,芯片设计公司不用太多关注,只要正常使和工艺方提供的PDK即可。

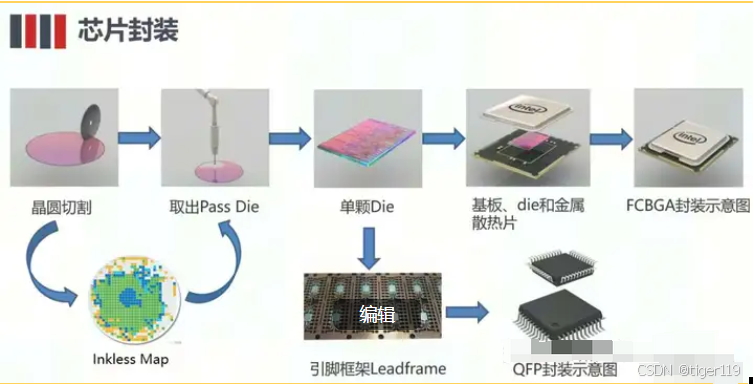

1.2:CP

CP(Chip Probing)也叫 “Wafer Probe” 或者“Die Sort”,是对整片Wafer的每个Die的基本器件参数进行测试,例如Vt(阈值电压),Rdson(导通电阻),BVdss(源漏击穿电压),Igss(栅源漏电流),Idss(漏源漏电流)等,把坏的Die挑出来,会用墨点(Ink)标记,可以减少封装和测试的成本,CP pass才会封装,一般测试机台的电压和功率不高,CP是对Wafer的Die进行测试,检查Fab厂制造的工艺水平。

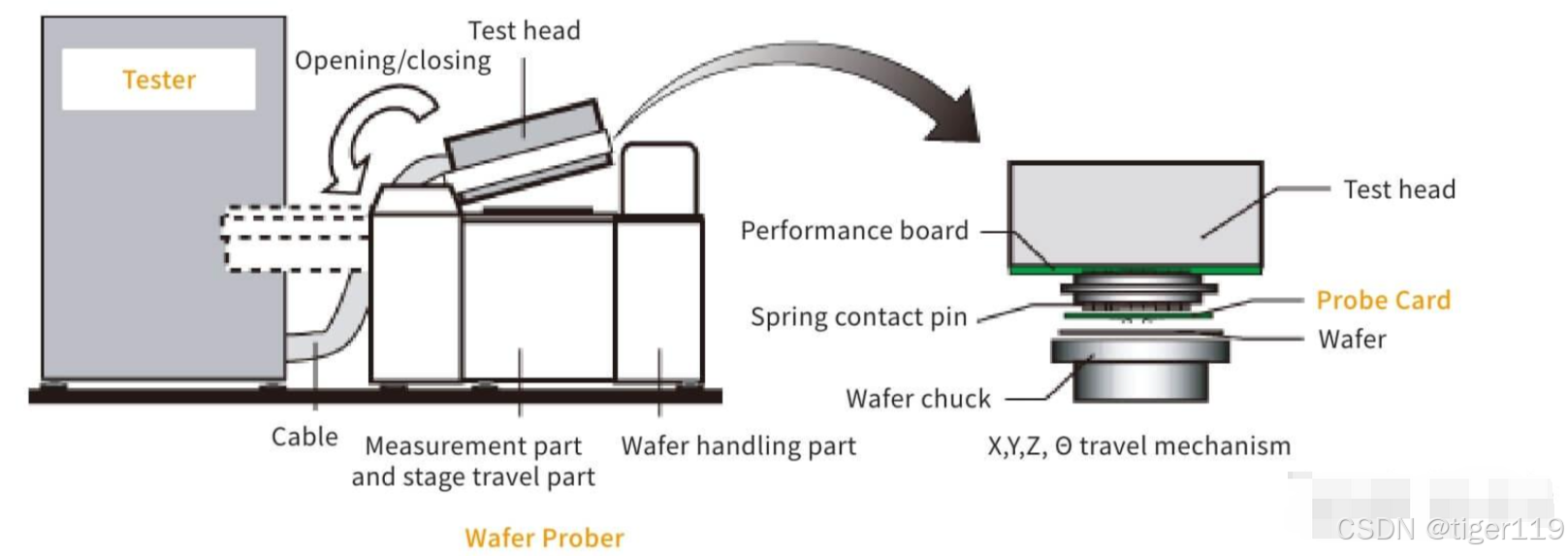

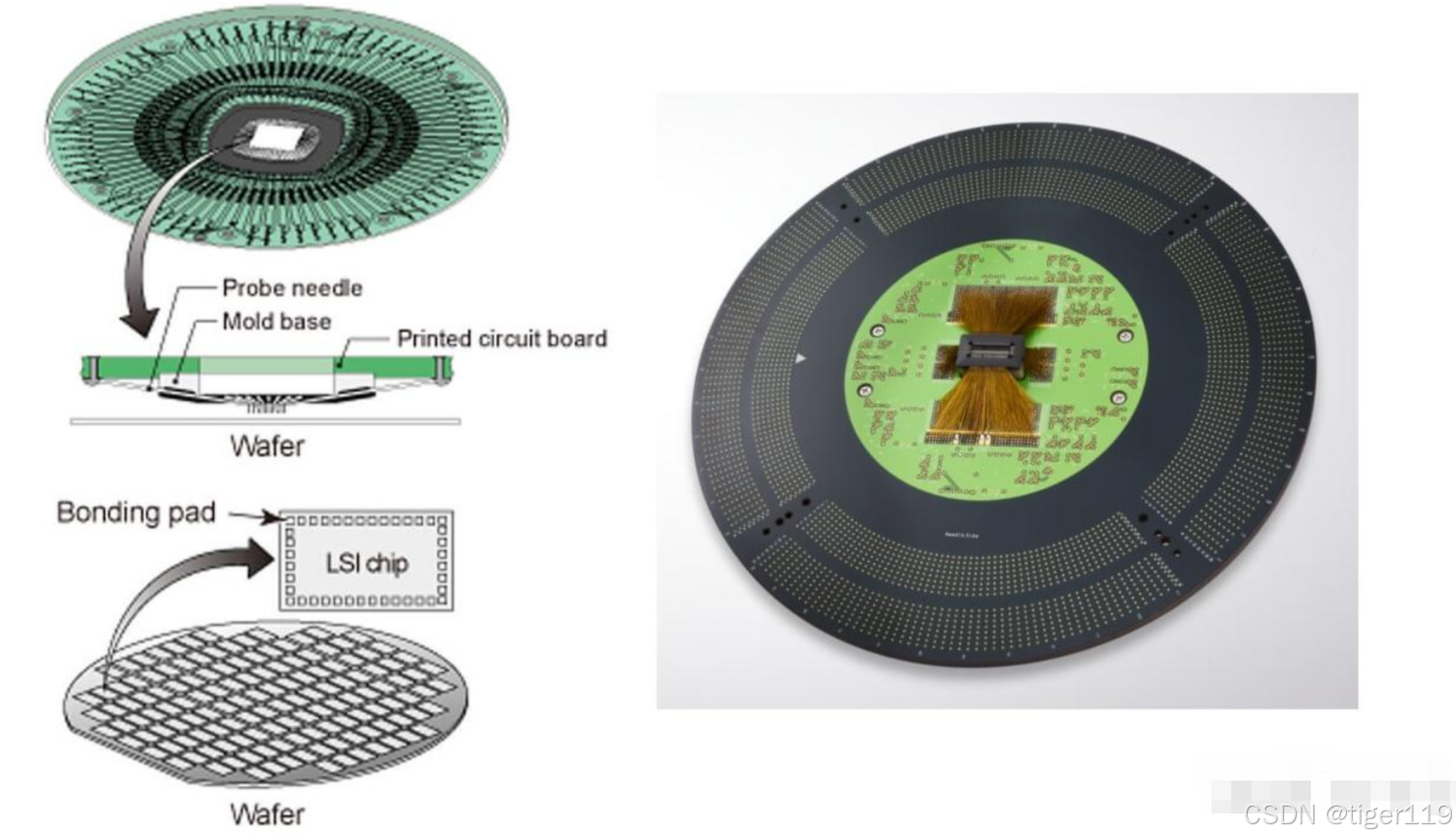

CP【Chip Probing】顾名思义就是用探针【Probe】来扎Wafer上晶片的pad,把各类信号输入进晶片,把晶片输出响应抓取并进行比较和计算。需要应用的设备主要是自动测试设备【ATE】+探针台【Prober】+仪器仪表,需要制作的硬件是探针卡【Probe Card】。

Wafer TEST ATE System

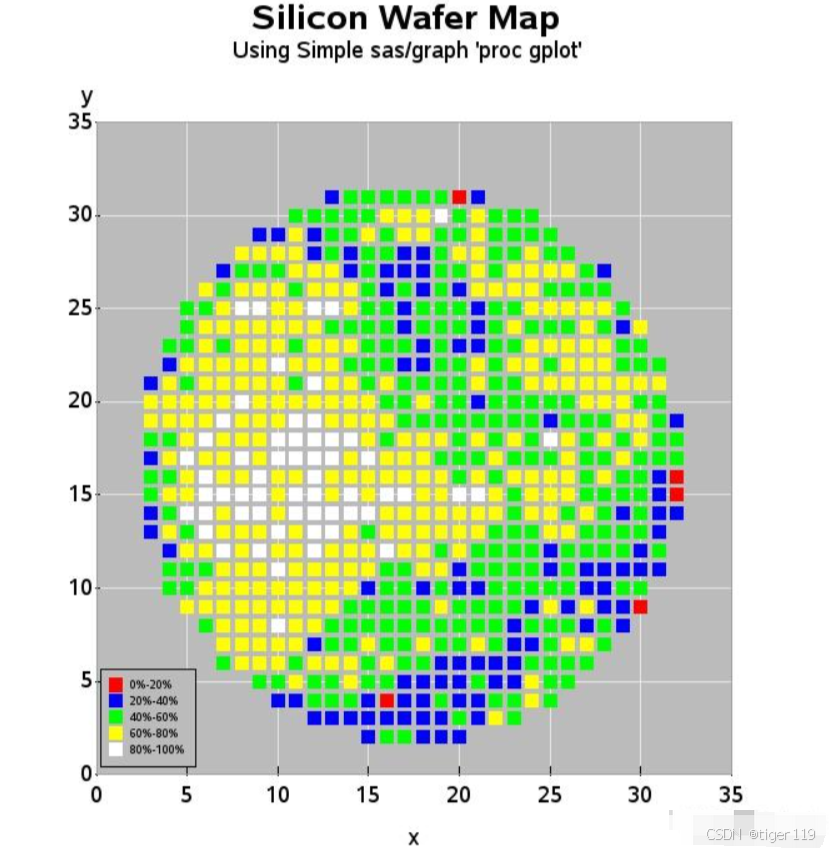

CP测试完成后,输出包含测试数据(datalog)和MAP。测试数据通常以一颗die为单位统计。主要包含die的位置信息,即XY坐标,测试项及测试结果PASS/FAIL(FAIL品又称REJECT)分BIN信息等。

MAP能够更直观的看出整片wafer的良率情况MAP上呈现的分BIN都是Hard Bin,此外还有SoftBin。同时,MAP也需要提供到封装环节,作为封装选die的依据。

CP测试的具体意义

- 通常在芯片封装阶段时,有些管脚会被封装在芯片内部, 导致有些功能无法在封装后进行测试,因此Wafer中进行CP测试最为合适。

- Wafer制作完成之后,由于工艺偏差、设备等原因引起的制造缺陷,分布在Wafer上的裸DIE中会有一定量的残次品。CP测试的目的就是在封装前将这些残次品找出来(Wafer Sort)同时还可以避免被封装后无法测试芯片性能,优化生产流程,简化步骤,同时提高出厂的良品率,缩减后续封装测试的成本。

- 另外,有些公司会根据CP测试的结果,将芯片划分等级,将这些产品投入不同的市场,购买时需要注意这一点。

CP测试,由于需要专用设备,并且相对专业,一般芯片设计公司会外包给三方公司完成。

1.3:FT

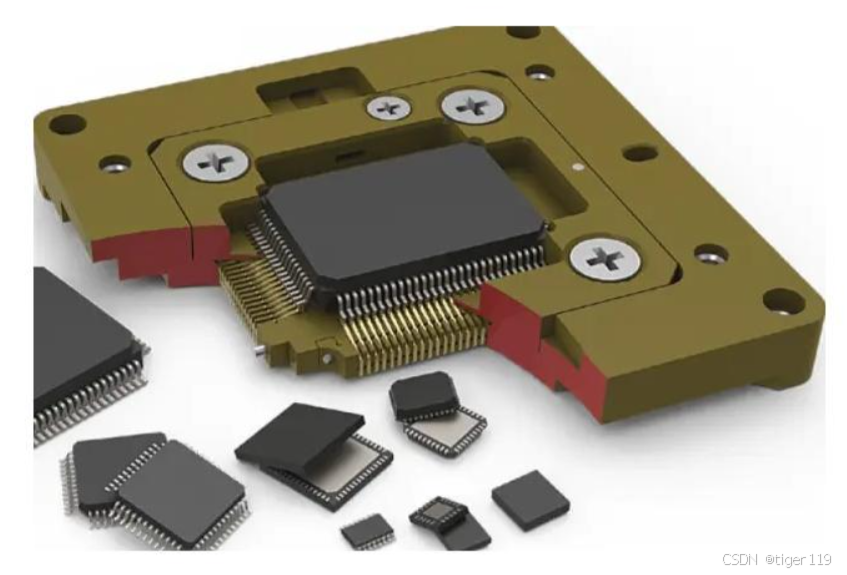

FT(final test)测试就是最终测试,在芯片完成封装之后进行的测试。FT测试属于芯片级测试,是通过测试板(Loadboard)和测试插座(Socket),使自动化测试设备(ATE)到封装后的芯片之间建立电气连接。

FT测试的目的是筛选出满足设计规格的产品卖给客户。

FT测试需要的硬件设备包括测试板、测试插座、ATE(Automation Test Equi[pment)测试机台、Handler。其中Handler也称为自动化分类机,是用来实现FT测试自动化的设备。

handler与tester相结合以及连上了interface之后才能测试。动作就是handler的手臂将芯片放进socket,然后contact pusher下压。使芯片的引脚正确的和socket的接触送出start信号,透过interface 给tester,测试完成之后tester送回binning及EOT(end of test)讯号。handler再做出分类的动作。

FT测试项目也是根据芯片的功能和特性决定的。常见的FT测试项一般有:

- Open/short test,也就是检查芯片引脚是否有开路或者短路,

- DC test也就是检查器件直流的电流和电压的参数。

- Eflash test也就是检查内嵌的flash功能和性能,包含读写参数动作功耗和速度等各种参数。

- Function test就是测试芯片的逻辑功能,

- AC test就是验证交流的规格,包括交流输出信号的质量和信号的实际参数。

- RF test这个就是针对有射频模块的芯片,主要验证射频模块的功能和性能参数。

- 还有就是DFT test,DFT(Design forTest) test主要包括scan扫描设计和内件的自测,也就是BIST(Build In Self Test)。

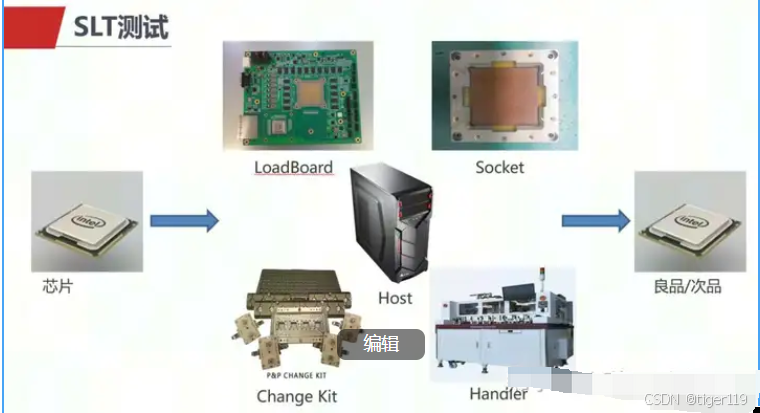

1.4:SLT

系统级SLT(System-Level Test)测试,常应用于功能测试、性能测试和可靠性测试中,常常作为成品FT测试的补充而存在,顾名思义就是在一个系统环境下进行测试,就是把芯片放到它正常工作的环境中运行功能来检测其好坏,缺点是只能覆盖一部分的功能,覆盖率较低所以一般是FT的补充手段。

大多数情况下,SLT中的系统会配备一些板载处理器来执行测试流程。由于片上系统(SoC)和系统级封装(SIP)芯片是SLT的主要测试对象,因此测试用处理器通常就是待测芯片的一部分。如果不是此种情况,待测芯片的外围测试系统通常会配备 一个合适的处理器。

SLT的测试时间比传统ATE的测试时间长很多,因为SLT是模拟真实终端使用场景的功能测试,而不是ATE中的结构测试。SLT的测试时间一般都超过一分钟,甚至可能长达数十分钟,典型的测试时间为10分钟左右。由于测试时间较长,与传统ATE测试相比,SLT测试设备必须具有更高的工位密度和更低的工位成本。

二:技术手段

我们在测试时,会用到哪些特殊的手段呢?

- 版级测试 偏向硬件,测试芯片在真实电路中的性能。

- 验证仿真 偏向设计和仿真,保证逻辑功能正确。

- DFT 测试 负责提升可测试性,桥接设计和测试流程。

- ATE 测试 专注于量产阶段的测试,确保芯片量产质量和效率。

2.1:版级测试

这里版级测试,更多是针对功能性测试,面向整个设计,而不是单个芯片。在做工程样品时,会了验证架构的正确性,需要做版级测试,需要针对不同的设计,做大量的测试板,进行专项的测试。

使用专用93000测试平台或者测试机,自已写自动化的工具,使用 示波器,信号发生器,逻辑分析仪进行测试。

- 验证芯片在特定硬件环境中的功能是否正常。

- 检测芯片与其他电路的互连关系,确保在板级的协同工作正常。

通用测试板:测试基础功能。

AC测试板:测试交流信号源

DC测试板:测试直流信号源

DDRX测试板:DDR内存接口的测试

PCIe测试板:针对PCIe的接口测试

……其它功能测试板。

2.2:验证仿真

对于FPGA芯片,需要加载固定的位流来进行芯片逻辑性验证。

- 在芯片制造之前,确保逻辑设计正确,避免错误流入生产。

- 提供行为层次和设计层次的验证。

- 对于FPGA芯片,由很多的Primitive组成,还有一定制的标准IP,这些组件的功能和接口使用,都需要验证仿真。因为软件会提供Macro IP的组件,所以,软件会做集成测试,硬件会针对每一个Primitive进行模块级的测试。而生产测试中心就是做上板的芯片测试了,也是非常重要的环节。

2.3:DFT测试

DFT测试实际上是在为各种测试做准备,因为其它测试依赖于DFT的实现。

为了让芯片更容易测试,在设计阶段插入一些测试结构,比如扫描链(Scan Chain)、BIST(内建自测试)等。

DFT 测试是基于设计中的这些测试结构进行的。

- 提高生产中 CP 和 FT 阶段测试的效率和覆盖率。

- 确保芯片能被准确测试,从而提高良品率。

2.4:ATE测试机

各种专业的ATE测试机台,这是芯片测试过程中最常用的。测试机台可以辅助完成功能,性能,电气,可靠性,测试覆盖率验证(DFT)。

掌握测试机台的脚本使用,非常重要。

好了,测试什么和方法都有了,我们来看看,在一个芯片公司中,生产测试中心具体的职责范围。

三:职责范围

按芯片设计公司的职责范围来看,涉及的事务有:

3.1:功能测试(Functional Testing)

验证芯片设计功能是否正确,通常在FPGA芯片设计完成后对初次流片进行功能测试。这是量产前的重要工作,也是验证软硬件设计是否正确的保证。在工程样片回来后,正式量产前的重要工作。当然,我们需要提前做好功能测试的样例和硬件板。

3.2:晶圆级测试(CP测试)

对晶圆上的裸片进行测试,筛选出功能正常的Die,避免浪费后续封装和测试资源。这是在晶圆制造厂出片后,要送到封装测试厂封装前的工作。

3.3:封装级测试(FT测试)

封装完成后进行的功能和性能测试,验证芯片在实际环境中的表现。

3.4:系统级测试(SLT)

模拟客户的实际应用场景,验证芯片在系统中的功能、性能和可靠性。

3.5:可靠性测试

包括Burn-in、HTOL、ESD/LU、温度循环测试等,评估芯片的长期稳定性和抗干扰能力。

3.6:失效分析(FA)

使用测试设备和工具(如FIB、SEM)对测试中发现的异常芯片进行失效分析,定位问题根源。

3.7:Corner测试

有时需要针对不同场景进行极端测试,获得极端性能的选片:

TT(Typical-Typical):表示典型工艺条件和典型温度下的情况。

FF(Fast-Fast):表示在最快的工艺条件和最低温度下的情况。这种情况下,晶体管开关速度最快。

SS(Slow-Slow):表示在最慢的工艺条件和最高温度下的情况。这种情况下,晶体管开关速度最慢。

FS(Fast-Slow):指在低温环境下,芯片的运行速度较快,而在高温环境下,芯片的运行速度较慢。

SF(Slow-Fast):指在低温环境下,芯片的运行速度较慢,而在高温环境下,芯片的运行速度较快。

四:组织架构

生产测试中心是一个很大的一级部门,按上面我们介绍的工作范围和内容,一般有如下几个部门组成(并不一定是这样的哈)。

4.1:工程产品部

需要做的事情:主要是整体设计和方案工作,有点象研发部门的架构部。

- 负责协同工作,包括芯片从设计到封装,生产测试,可靠性测试,质量等部门,协同保障产品质量。

- 管控过程,分析数据,保证量产可控,成本可控。失效分析,解决良率问题。

- 制定生产计划,良品率方案,确认从NPI转量产的计划,包括CP,FT测试策略。

- 制定并完成可靠性测试报告,应对不同行业,专业领域的应用。

- 对量产测试数据进行分析,给研发相应的指标上下限指标,用于改进产品质量。

- 与设计团队协作,理解芯片特性和测试要求,编写和调试ATE测试程序,优化测试时间。

技能要求:

- 熟悉芯片制造和测试流程(CP、FT)。

- 具备ATE测试设备操作能力(如Teradyne、Advantest)。

- 熟悉数据分析工具(如Excel、JMP)。

- 掌握良率分析和失效分析方法。

4.2:系统测试部

这是主力的测试部门,凡是和公司芯片产品强相关的系统功能,需要在这个部门完成测试。

类似完成功能和性能测试。因为与公司产品强相关,需要自主完成。

- 完成芯片的功能和性能全覆盖测试,确保各项指标可以达到量产和客户送样的要求。

- 制定Validation计划,完成相应的测试和测试计划。

- 系统测试需要的软,硬件的开发工作。

技能要求:

- 熟悉电路板设计和调试(如高速信号调试)

- 能够编写测试脚本(Python、C等),使用调试工具(如逻辑分析仪、示波器)。

- 理解常见协议(如PCIe、DDR、USB)和嵌入式系统。

4.3:量产测试部

负责芯片量产测试(CP和FT),保证生产效率和产品质量。优化测试流程,缩短测试时间,降低测试成本,对测试不良品进行分析和筛选。

需要完成的事情:

- 维护和优化ATE测试程序,确保量产测试的稳定性。

- 开发探针卡(Probe Card)和负载板(Load Board)。

- 分析测试数据,发现和解决量产中的问题。

- 与供应链合作,保证测试设备和资源的可用性。

技能要求:

- 测试设备:熟悉主流ATE设备(如Advantest V93000、Teradyne J750)。

- 硬件知识:掌握测试板(如探针卡)的设计与调试。

- 数据分析:使用统计工具(如JMP)分析测试结果,提高良率。

4.4:封装设计部

负责芯片封装设计,保证封装可靠性和性能。提供封装方案,包括引脚布局、热管理和电气性能设计。设计和验证封装基板(Substrate)的性能。支持客户对封装形式的定制需求。

需要完成的事情:

- 根据芯片特性,设计适合的封装类型(如BGA、QFN等)。

- 使用EDA工具进行封装基板的布线和信号完整性仿真。

- 与生产部门合作,验证封装可靠性(如热分析、机械应力测试)。

- 提供封装相关的技术支持,协助系统级验证。

技能要求:

- 设计能力:熟悉封装设计工具(如Mentor Xpedition、Cadence SiP),掌握信号完整性(SI)、电源完整性(PI)分析。

- 分析能力:热仿真和机械应力分析能力。

- 材料知识:理解封装材料的特性(如基板材料、引脚材料)。

4.5:其它部门

还有一些包括 质量管理,项目管理的工作。

主要负责组织各种评审工作,制定可靠性标准,HAST,HTOL 设计等。

- 制定和实施可靠性测试计划(如HTOL、ESD、SER)。

- 对生产测试中发现的不良芯片进行分析。

- 撰写质量报告,向客户反馈产品质量情况。

- 协调内部资源,持续提升产品质量。

五:工程样片Validation测试

以FPGA芯片的Validation测试为例,我们可以实际来看看,生产测试中心具体在样片回来后,需要做哪一些Validation测试?

我们只挑几个有代表性的,比较重要的模块进行举例说明。

5.1:模拟模块

5.1.1. 电源相关测试

- Bg_vref (1): 测试电压基准值的变化范围。

- Iconst 50uA (2): 测试电流源偏差。

- Ipoly 50uA (3): 测试电流源偏差。

- Bg_v (4): 电压基准值的变化范围。

- vccbram por/pdr trigger test (8): 测试电源触发值偏差。

- vccint por/pdr test (9): 测试主电源触发值和温度相关性。

- vccaux por/pdr test (10): 测试辅助电源触发值的稳定性。

- vccio_cfg por/pdr test (11): 测试IO电源触发值的偏差。

- ldo_out (VCCM) (17): 测试LDO输出电压的偏差。

- ldo_bypass (18): 测试LDO旁路状态下输出电压的稳定性。

- LDO power up (19): 测试LDO的上电功能。

- power down test (16): 测试电源断电功能。

5.1.2. 时钟相关测试

- OSC (14): 测试内部时钟的频率准确性。

- osc_div2/4 test (15): 测试分频器的频率正确性。

- clk tree test (21): 测试时钟树的功能。

5.1.3. I/O模拟特性测试

- MFG BUFFER (20): 测试缓冲区的输出电压范围和一致性。

5.1.4. 电气容差和极限测试

- POR Delay (12): 测试上电复位延迟的时间误差。

5.2:PRAM & Config

这是FPGA非常重要的模块了,负责位流的加载/编程。测试较简单,主要就是在加电后能否正常读写数据。一般会用到EFuse,也需要做写入的测试。

5.3:PLL

PLL是生成时钟的重要设施,需要重点测试。

主要测试:输入时钟的测试,PFD锁定时间,CP/LFP,VCO

5.4:MDAC功能测试

略

5.5:DLL功能测试

略

5.6:Marco IP 功能测试

这个就很复杂了,主要是对基础的Primitive的验证,具体要看芯片的架构。

包括重要的逻辑计算单元CLB,开关SWB,内存BRAM,DSP,IOB等器件的测试。

包括高速DDR,XGT,PCIE的测试。

六:其它重点

还有一些没有提到的,但也不知道如何归类,我就简单列出来。

6.1:芯片的点亮

芯片生产封测完成,第一件事情是要点亮,这件事情自然是生产测试中心来主导完成。我们以FPGA芯片为例,说明一下点亮的基本步骤:

- 检查IO Pin的配置

- 电源上电测试

- Init_b 初始化

- PRAM 测试

- 下载位流

- 最小程序运行(一般会是一个跑马灯的程序)

点亮主要是验证最基本的功能可行,并不对芯片的完整功能进行测试。

6.2:再次强调测试的重点

芯片生产测试包括功能、参数、高低温、老化、ESD、封装和可靠性测试等多个方面。重点关注以下几项:

- 功能完整性:保证设计功能正确。

- 电气性能:电压、电流、频率、功耗等符合设计要求。

- 高低温稳定性:芯片在极端温度下正常运行。

- 抗静电保护:防止静电损坏。

- 可靠性:筛除早期失效产品,确保长期稳定工作。

6.3:量产测试的重点

使用自动化测试设备,对大量的芯片进行高速的测试,快速筛选样片,测定质量。

功能测试需要专门的DV板或开发板来提供真实电路环境。测试案例要涵盖芯片的基本功能、边界条件 和 异常路径,同时验证输入输出时序、复位、接口通信、状态机和抗扰能力。对于大规模量产,还需要借助ATE设备进行自动化测试,确保高效和稳定。

6.4:可能需要的重要仪器

示波器,信号源,电源,数据采集仪,高速示波器。

对于高速示波器,费用很高,可能需要租借来使用。

刚接触生产测试中心的工作,很多细节都不太了解,后续再逐渐补充,学习。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?