个人感觉时钟选择时CLKCTL蛮有用的。但是哪个信号是全局时钟就是综合器自己认为的吗,好像无法人为干涉。

哪些信号会消耗全局时钟网络呢?外部输入或者内部产生时钟,时钟使能,异步清零信号以及其他高扇出信号。

1—— Altera

Altera的综合器或者PR工具都会根据实际信号clock和reset,preset的fanout大小确定是不是用全局时钟资源。若用了全局时钟资源,你可以在Q2的technology map view里看到Altclkctrl的cell名称--时钟控制模块(Clock Control Block)。

当我们的系统占用比较多的全局时钟资源时,将外部的时钟和FPGA内部产生的时钟资源综合考虑,充分考虑PLL的位置以及外部输入时钟的管脚位置,保证每个时钟都能分配到全局时钟资源,得到最好的时序性能。

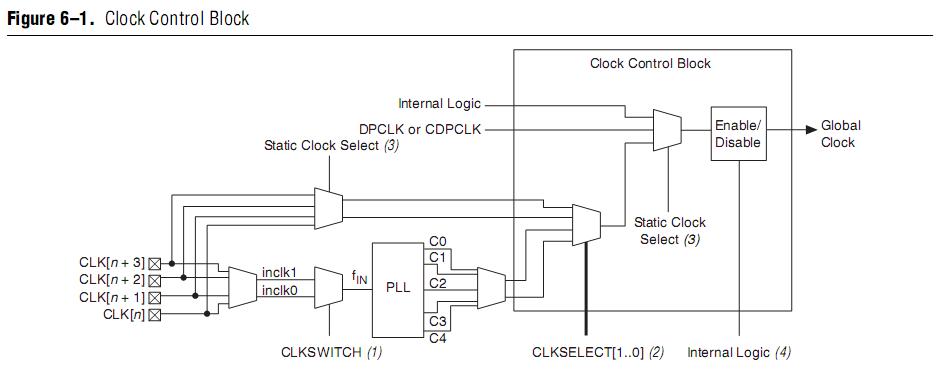

每个全局时钟都有一个时钟控制模块(Clock Control Block),如下图:

该部分的绝大部分配置都是由QuartusII完成,我们能够设置是(2)CLKSELECT[1..0],在MegaWizard…选择I/O--ALTCLKCTRL模块,就可以得到相应的模块,由上图可以知道,该模块的数据必须来自专用时钟管脚或者PLL输出,无法与LC驱动的全局时钟资源连接。当我们需要进行时钟切换时,最好用该功能模块,因为用LC产生的时钟选择模块很容易产生毛刺,另时序电路无法正常工作。

我们知道外部输入或者内部产生时钟,时钟使能,异步清零信号以及其他高扇出信号都会占用全局时钟资源,当系统涉及的上述信号数量过多时,FPGA无法满足,我们就需要有取舍的设置哪些时钟可以占用Global Clock,哪些可以不用。具体设置在Assigment Editor中完成,说明如下:

Auto Global Clock:用于设置时钟是否占用Global Clock;

Auto Global Register Control Signals:用于设置寄存器控制信号(异步复位,寄存器使能等)是否占用Global Clock;

也可在Setting--Fitter Setting--More Setting…将上述设置关闭,则QuartusII阻止信号分配在全局时钟资源上(不推荐)。

4296

4296

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?