前言:

硬件环境:Xilinx ZynqMP XCZU4EV-SFVC784-1-I

软件环境:Ubuntu20.04LTS + Vivado2021.1 + Vitis2021.1

文章目标:1、UART在正常模式下中断接收的回显例子。

2、Xilinx自带UART库代码有点累赘,在例1基础上优化。

3、在例2的基础上,添加UART在正常模式下IDLE中断的(接收超时中断)例子。

参考程序:/tools/Xilinx/Vitis/2021.1/data/embeddedsw/XilinxProcessorIPLib/drivers/uartps_v3_11

ZynqMP串口关键功能简介:

1、PS有两个UART外设,分别是UART0和UART1。

2、UART的TX 和 RX都有一个64Byte的FIFO,读写数据都需先经过FIFO。

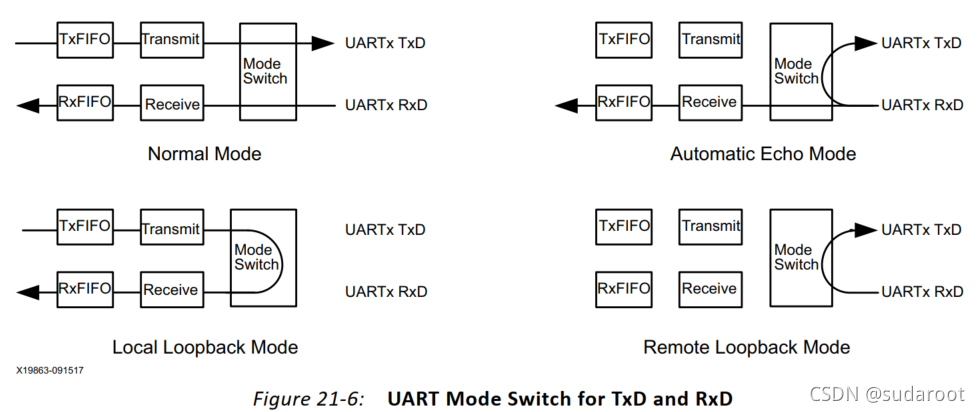

3、UART支持4种模式。分别是正常模式, 回显模式,本地回环模式, 外部回环模式。

更多详细信息请看《UG1085 Zynq UltraScale+ Device Technical Reference Manual.pdf》

准备工作:

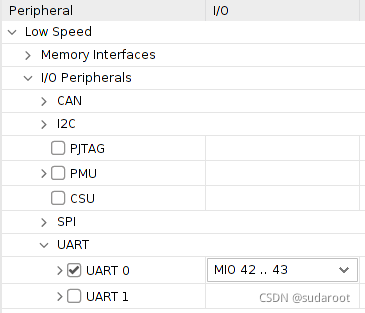

1、打开Vivado2021.1,创建一个工程,勾选UART0外设,生成导出XSA文件。

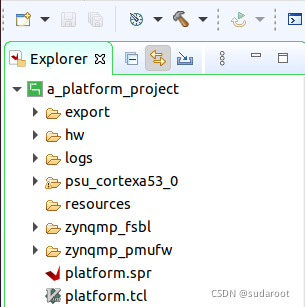

2、打开Vitis2021.1,创建一个Platform Project。

例1:UART中断接收回显

1、创建一个空白的Application Project,添加main函数文件。

2、在main函数文件中添加如下代码。为了简化代码,故非关键函数不进行任何返回值判断。

#include "stdio.h"

#include "xparameters.h"

#include "xuartps.h"

#include "xscugic.h"

#define UART_DEVICE_ID XPAR_XUARTPS_0_DEVICE_ID

#define INTC_DEVICE_ID XPAR_SCUGIC_SINGLE_DEVICE_ID

#define UART_INT_IRQ_ID XPAR_XUARTPS_0_INTR

void UserHandler(void *CallBackRef, u32 Event, unsigned int EventData);

void Handlers(void *CallBackRef);

int UartPsSend(XUartPs *InstancePtr, u8 *BufferPtr, u32 NumBytes);

int UartPsRev(XUartPs *InstancePtr, u8 *BufferPtr, u32 NumBytes);

XUartPs UartPs; /* Instance of the UART Device */

XScuGic ScuGic; /* Instance of the Interrupt Controller */

int main(void)

{

XUartPs_Config *UartPs_Config;

XScuGic_Config *ScuGic_Config;

/* 1、初始化UART,设置波特率,正常模式 */

UartPs_Config = XUartPs_LookupConfig(UART_DEVICE_ID);

XUartPs_CfgInitialize(&UartPs, UartPs_Config,

UartPs_Config->BaseAddress);

XUartPs_SetBaudRate(&UartPs, 115200);

XUartPs_SetOperMode(&UartPs, XUARTPS_OPER_MODE_NORMAL);

/* 2、初始化中断控制器,中断函数连接到系统,使能中断 */

ScuGic_Config = XScuGic_LookupConfig(INTC_DEVICE_ID);

XScuGic_CfgInitialize(&ScuGic, ScuGic_Config,

ScuGic_Config->CpuBaseAddress);

Xil_ExceptionRegisterHandler(XIL_EXCEPTION_ID_INT,

(Xil_ExceptionHandler) XScuGic_InterruptHandle

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1977

1977