前言:

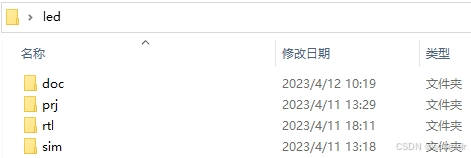

为了方便文件管理,在文件夹内建立几个子文件夹,并把相关的项目资料统一收纳在内。

- doc文件夹:开发过程中使用的辅助文档文件(如绘制的波形图文件、开发过程中涉及到的硬件资料、系统架构图等);

- prj文件夹:Vivado软件新建工程及产生的文件;

- rtl文件夹:开发过程中的 RTL源代码文件;

- sim文件夹:仿真工程与仿真文件等。

注意:工程路径除了英文、数字以及下划线等,不要出现中文或者其它特殊字符,否则 FPGA 开发工具无法识别工程路径。

1. 需求分析

对项目需求进行详细分析,提取项目需求需要实现什么功能。

- 问题:请回答项目要实现的功能。

2. 系统设计

根据项目需求进行系统架构设计。

架构设计主要是将系统分为哪些模块,数据流怎么走,控制流怎么走,以及计算系统运行的带宽和评估系统的工作频率;

3. 绘制系统框图

目的:

- 确定系统内各个子模块的结构层次;

- 梳理系统对外的IO信号;

- 梳理系统与子模块之间的交互信号。

4. 绘制波形图

根据该模块的功能并且结合芯片的数据手册或者接口协议,确定模块接口信号的时序关系,然后绘制各个模块的时序波形图。

5. 编写 RTL 代码

需严格按照绘制出的波形图编写各个模块代码。

6. 编写TestBench代码

TestBench是用于验证功能模块的设计是否符合预期,其内容主要分为以下三个步骤:

1、向被测模块的输入接口添加激励;

2、对被测功能模块的顶层接口进行信号例化;在一个模块中引用另一个模块,对其端口进行相关连接,叫做模块例化。

3、判断被测模块的输出是否满足设计预期。

7. 进行仿真

向仿真软件里添加写好的源代码和仿真代码;

- 仿真过程中如果 RTL 代码有语法错误,仿真工具下面的提示框会显示语法报错详 细信息,可以对照该信息修改 RTL 代码,直至 RTL代码语法错误修改完毕,才能出现仿真波形;

- 观察仿真的波形图是否与我们绘制的时序波形是否一致。如果不一致,则需要通过修改代码使仿真波形与我们绘制的时序波形一致。

7. Vivado新建项目工程

使用 Vivado新建工程并添加我们前面编写的 RTL 代码;

7. 分析与综合

对工程进行综合编译,通过观察综合编译生成的报告可以帮助避免最常见的设计错 误,以便对设计进行分析和改进。

7. 约束输入

在 Vivado对工程引脚进行约束,引脚约束完成后就可以进行布局布线与生成下载文件;

8. 设计实现

就是工程布局和布线的过程。它的作用是将综合生成的逻辑网表配置到具体的 FPGA芯片上。

布局布线完成后,就可以生成下载文件了,下载文件生成成功就可以进行下一步的上板验证。

9. 上板验证及调试

连接好开发板与下载器,将生成的下载文件通过下载器下载到开发板,然后观察开发板的实物运行是否是预期想要实现的功能。

- 如果上板实验现象正常,则说明前期设计与代码编写都正常;

- 如果上板实验现象不正常,可以通过迭代前面设计的每一步来查找问题,如果发现前面的步骤都没有问题,那么这时候可以通过在线调试来查找问题,直到解决问题,上板验证现象正常。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?