延伸阅读:

目录

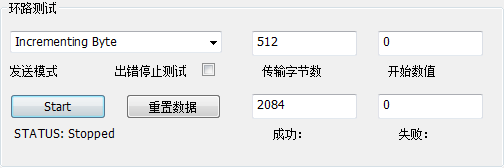

本模块用于FPGA环路代码的性能测试,环路测试时上位机负责数据的先发后收和对比,FPGA仅负责数据的搬运。模块提供了4种发送模式:Constant Byte、Random Byte、Incrementing Byte和Incrementing DWORD,依次对应固定数值、随机数值、单字节递增和4字节递增的512字节数据,上位机默认选择单字节递增传输模式。传输字节数必须为512、1024、1536和2048中的一个,传输非512整数倍的字节数时,环路测试会一直报错。环路传输过程中,成功和失败的次数会实时显示在上位机上。上位机上带有一个出错停止测试的复选框,用于环路测试出错时停止环路测试。重置按钮用于将环路成功和失败次数置0,当上位机处于环路测试时,会被重置按钮强制停止。

1. 设计思路

环路测试的原理很简单,上位机先发送512字节数据,再接收512字节数据,最后将接

订阅专栏 解锁全文

订阅专栏 解锁全文

7620

7620

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?