Verilog

文章平均质量分 64

verilog

卢卡喵

这个作者很懒,什么都没留下…

展开

专栏收录文章

- 默认排序

- 最新发布

- 最早发布

- 最多阅读

- 最少阅读

-

verilog +: / -:语法

这个是在uart总线协议中遇到的,下面对它简单了解一下在Verilog2001以后,Verilog支持在范围中是用变量,并且引入心得语法如下:语法定义:变量的定义可以分为大端和小端,由于实际使用中变量常定义成大端,所以这里对小端不进行分析了 reg [31:0] big_vect; 大端 reg [0:31] little_vect;小端对大端变量进行分析:(+:) 升序将开始位放在右侧,(-:)降序将开始位放在左侧big_vect [31:0]big_vect [0 + : 8]原创 2022-05-11 23:04:28 · 2361 阅读 · 0 评论 -

格雷码和二进制之间的转换

格雷码格雷码:又称循环码,相邻两个格雷码之间只有一位二进制位改变。优点:用格雷码做计数器的值时,因为相邻两个格雷码之间只有1位发生改变,降低了在做状态转换时出现亚稳态的概率。所以在异步FIFO中,会采用格雷码来计数。注意:格雷码必须是计数到2^n 才是每次改变一个bit,这也就是为什么异步FIFO的深度都是2 ^n,就算浪费面积,也需要把深度这样设置。二进制转格雷码原数右移一位在与原数异或格雷码转二进制二进制最高位取格雷码最高位,然后循环做二进制高位与低一位的格雷码异或...原创 2022-05-07 22:14:49 · 3356 阅读 · 0 评论 -

异步FIFO代码与测试

文章目录1.异步FIFO设计难点2.空满标志3.格雷码的使用4.数据同步5.异步FIFO代码6.异步FIFO的测试点7.FIFO的深度如何计算异步FIFO,读写应用不同的时钟,它有两个主要作用,一个是实现数据在不同时钟域进行传递,另一个作用是实现不同数据宽度的数据接口。同步FIFO和异步FIFO的最主要的不同就体现在空满标志产生的方式上,由此引出两者一些不同的参数。1.异步FIFO设计难点异步FIFO的设计难点在于空满标志符的产生,由于异步FIFO的读写是用不同的时钟来控制的,所以不能用计数器的方法原创 2022-05-07 22:13:48 · 3575 阅读 · 0 评论 -

同步FIFO代码与测试

文章目录1.FIFO的主要参数2.同步FIFO的设计2.1模块划分FIFO即Firdst In First Out,是一种先进先出数据存储、缓冲器,我们知道一般的存储器是用外部的读写地址来进行读写,而FIFO这种存储器结构并不需要外部的读写地址而是通过自动地加一操作来控制读写,这也就决定了FIFO只能顺序的读写数据。同步FIFO,读和写应用在同一个时钟。它的作用一般是做交互数据的一个缓存,也就是说它的主要作用就是一个buffer。1.FIFO的主要参数参数符号含义宽度FIFO原创 2022-05-06 21:11:47 · 1511 阅读 · 0 评论 -

偶数分频、奇数分频

文章目录1.占空比2.偶数分频1.占空比占空比:即为高脉冲宽度与周期之比,即TH/T。 其中,时钟周期为T,TH为高脉冲宽度,TL为低脉冲宽度,T=TH+TL。2.偶数分频偶数分频实现简单,用计数器在上升沿或者下降沿计数,当计数器从0计数的值等于分频系数的一半-1或等于分频系数-1时,信号翻转。偶数分频(50%占空比):N/2 - 1和N-1翻转偶数分频原理如下:分频系数为4,是4分频。如输入时钟为24MHz,进行4分频后,分频后的时钟频率为6MHz。首先了解下简单的二分频:module原创 2022-05-04 16:23:33 · 3652 阅读 · 0 评论 -

数电中的各类触发器

文章目录1.RS触发器2.JK触发器3.T触发器4.D触发器1.RS触发器RS触发器为典型的电平式触发器,基本结构是由两个与非门的输入、输出端交叉连接而成。 一定要牢记RS触发器的约束条件:R+S=12.JK触发器JK触发器属于脉冲触发方式,触发翻转只在时钟脉冲的负跳变沿发生,严格上来说,T触发器其实是JK触发器的一种特殊类型。3.T触发器T触发器是在数字电路中,凡在CP时钟脉冲控制下,根据输入信号T取值的不同,具有保持和翻转功能的触发器,即当T=0时能保持状态不变,当T=1时一定翻转的原创 2022-05-01 17:52:13 · 10945 阅读 · 0 评论 -

verilog-同步复位与异步复位

同步复位sync异步复位async特点复位信号只有时钟上升沿到来时才有效无论时钟沿是否到来,只要复位信号有效,就进行复位verilog描述always@(posedge clk)always@(posedge clk or negedge rst_n)总结推荐使用异步复位,同步释放的方式,而且复位信号低电平有效同步清零module dff(d,clk,rst_n,q);input d,clk,rst_n;output reg q;alway...原创 2021-12-22 23:01:03 · 2141 阅读 · 0 评论 -

HDLBits答案合集

HDLBits网站答案:HDLBits答案1-Getting StartedHDLBits答案2-Verilog Langue:BasicsHDLBits答案3-VectorsHDLBits答案4-Modules:HierarchyHDLBits答案5-ProceduresHDLBits答案6-More Verilog FeaturesHDLBits答案7-Combinational LogicHDLBits答案8-MultiplexersHDLBits答案9-Arithmetic Ci原创 2021-12-02 22:15:00 · 5394 阅读 · 0 评论 -

verilog-阻塞赋值与非阻塞赋值

一、阻塞赋值(b=a):顺序执行赋值语句执行完,块才结束b的值在赋值语句执行完后立刻改变always@(posedge clk) begin b=a; c=b; endclk上升沿到来时:b马上取a的值,c马上取b的值(即等于a)效果:b=a; c=a二、非阻塞赋值(b<=a):并行执行上面语句所赋的变量值不能立即就为下面的语句所用块结束后才能完成这次赋值操作,所赋的变量值是上一次赋值得到的always@(posedge clk) begin原创 2021-11-11 16:12:25 · 1358 阅读 · 0 评论 -

HDLBits答案13-Sequential:Shift Registers

文章目录1.1.原创 2021-10-30 21:38:42 · 1148 阅读 · 2 评论 -

HDLBits答案14-Sequential:More Circuits

文章目录1. Rule902.Rule 1103. Conway's Game of life 16*161. Rule90各单元的下一状态是此时当前单元相邻两位的异或。在这个电路中,创建一个512单元系统(q(511:0)),并在每个时钟周期中前进一个时间步长。加载(load)表明系统的状态应该加载data[511:0]至q中,假设边界(q[0]和q[512])都为零。module top_module( input clk, input load, input [511原创 2021-10-30 21:38:12 · 796 阅读 · 0 评论 -

HDLBits答案12-Counters

文章目录1. Four-bit binary counter2. Decade counter3. Decade counter again4. Slow decade counter5. Counter 1-126. Counter 10007. 4-digit decimal counter8. 12-hour clock1. Four-bit binary counter构建一个从0到15的4位二进制计数器,周期为16。同步复位,复位应该将计数器重置为0。module top_module (原创 2021-10-28 23:10:55 · 1679 阅读 · 0 评论 -

HDLBits答案11-Latches and Flip-Flops

文章目录1. Dflip-flop2. Dflip-flops3. DFF with reset4. DFF with reset value5. DFF with asynchronous6. DFF with byte enable7. D Latch8. DFF9. DFF10. DFF+gate11. Mux and DFF12. Mux and DFF13.DFFs and gates14.Create circuit from truth table15. Detect an edges16.原创 2021-10-28 23:10:16 · 1698 阅读 · 0 评论 -

Verilog:避免Latch

一、什么是锁存器?锁存器与触发器的区别锁存器与触发器最大区别在于,锁存器是电平触发,而触发器是边沿触发。锁存器在不锁存数据时,输出随输入变化,但一旦数据锁存时,输入对输出不产生任何影响。latch的危害:1.输入状态可能多次变化,容易产生毛刺,增加了下一级电路的不确定性;2.在大部分 FPGA 的资源中,可能需要比触发器更多的资源去实现 Latch 结构;3.锁存器的出现使得静态时序分析变得更加复杂在组合逻辑中,不完整的if-else结构,会产生latch。避免此类latch的方法主要有两种原创 2021-10-28 23:09:34 · 1539 阅读 · 0 评论 -

verilog :generate语句

Verilog generate 语句是用于编写可配置、可综合RTL的强大构造。它可用于创建模块和代码的多个实例化。generate-for语句:1.必须有genvar关键字定义for语句的变量。2.for语句的内容必须加begin和end。3.for语句必须有一个名字begin:(name)在buffer_8中例化buffer-1 8次module buffer_8( input wire[7:0] din, input wire[7:0] dout); genvar i; gene原创 2021-10-28 20:00:00 · 1338 阅读 · 0 评论 -

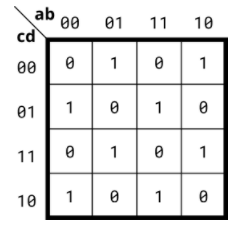

HDLBits答案10-Karnaugh Map to Circuit

文章目录1. 3-variable2. 4-variable3. 4-variable4. 4-variable5. Minimum SOP and POS6.Karnaugh map7.Karnaugh map8. K-map implemented with a multiplexer1. 3-variablemodule top_module原创 2021-10-28 15:20:03 · 954 阅读 · 0 评论 -

HDLBits答案9-Arithmetic Circuits

文章目录1. Half adder2. Full adder3. 3-bit binary adder4. Adder5. Signed addition overflow6. 100-bit binary adder7. 4-digit BCD adder1. Half adder创建半加法器。半加法器将两位加起来(没有进位),产生和和进位。module top_module( input a,b, output count,sum); assign {count,sum} = a + b;原创 2021-10-28 20:15:00 · 1026 阅读 · 0 评论 -

HDLBits答案8-Multiplexers

文章目录1. 2-to-1 multiplexer2. 2-to-1 bus multiplexer3. 9-to-1 multiplexer4. 256-to-1 multiplexer5. 256-to-1 4-bit multiplexer1. 2-to-1 multiplexer创建一个 1 位宽的 2 对 1 多路复用器。当sel=0时,选择a。当 sel=1 时,选择 b。module top_module( input a, b, sel, output out );原创 2021-10-27 21:34:21 · 1032 阅读 · 0 评论 -

HDLBits答案7-Combinational Logic

文章目录1.wire2.GND3.NOR4.Another gate5.Two gates6.More logic gates7. 7420 chip8. Truth tables9. Two-bit equality10. Simple circuit A11. Simple circuit B12. Combine circuit A and B13. Ring or vibrate14.Thermostat15. 3-bit population count16. Gates and vectors1原创 2021-10-27 21:33:19 · 1335 阅读 · 0 评论 -

HDLBits答案6-More Verilog Features

文章目录1.Conditional ternary operator2. Reduction operators3.Reduction:Even wider gates4.Combinational for-loop:Vector reversal25.Combinational for-loop:255-bit population count6.Generate for-loop:100-bit binary adder 27.Generate for-loop:100-digit BCD adder原创 2021-10-27 21:32:28 · 1170 阅读 · 0 评论 -

HDLBits答案5-Procedures

文章目录1.Always block(combinational)2.Always block(clocked)3.If statement4.If statement latches5.Case statement6.Priority encoder7.Priority encoder with casez8.Avoiding latches1.Always block(combinational)有两种类型的always块:组合:always@(*)时序:always@(posedge clk)原创 2021-10-25 23:08:58 · 1162 阅读 · 0 评论 -

HDLBits答案4-Modules:Hierarchy

1. Module只要使用的所有模块都同属一个项目,就可以通过在模块内部实例化,来创建模块的层次结构。两种方式分别是按位置和按名称连接,按位置调(简洁但不稳,顺序不能乱),按名称调(顺序可变)按位置:mod_a instance1 (wa, wb, wc )按名称:mod_a instance2 (.out(wc), .in1(a), .in2(b))module top_module (input a, input b, output out) mod_a inst1 (a,b,out);原创 2021-10-20 23:00:00 · 1435 阅读 · 0 评论 -

Verilog-Implicit Nets、Pack和Unpack

在HDLBits学习中,了解到隐式网的概念,下面对它进行详细的讨论:在Verilog当中,如果在一个assign语句或者一个未被声明的模块当中出现/引用未声明的向量,Implicit nets 就会被隐性地生成在模块当中。Implicit nets一般都是一位wire变量,如果作为向量使用,很可能会报错。用指令default_nettype none可以禁止Implicit nets 的生成。wire [2:0] a,c; //a和c是3位长的向量assign a = 3'b101; // a =原创 2021-10-19 10:54:49 · 2267 阅读 · 0 评论 -

HDLBits答案3-Vectors

文章目录Vectors1.Vector02. Vector13. Vector24. Vector gates5. Gate46. Vector37. Vectorr8.Vector49. Vector5Vectors1.Vector0module top_module ( input wire [2:0] vec, output wire [2:0] outv, output wire o2, output wire o1, output wire o0,); assign outv原创 2021-10-18 23:18:14 · 1362 阅读 · 0 评论 -

HDLBits答案2-Verilog Langue:Basics

Basics位运算符的优先级优先级从高向低~&^ ^~|1. Wiremodule top_module (input in, output out); assign out = in;endmoduel2. Wire4由于verilog语句是并行运行,所以当有多个assign语句时,它们在代码中出现的顺序并不重要。module top_module ( input a,b,c output w,x,y,z); assign w = a; assign x原创 2021-10-17 16:56:47 · 943 阅读 · 0 评论 -

HDLBits答案1-Getting Started

建立一个没有输入和一个输出的电路1.没有输入的电路module top_module (output zero); assign zero = 1'b0;endmodule2. 一个输入的电路module top_module (output one); assign one = 1'b1;endmodule原创 2021-10-17 16:13:46 · 747 阅读 · 0 评论 -

Verilog语法

Verilog语法文章目录Verilog语法一、Verilog设计方法二、模块的结构1.模块端口定义2.模块内容3.数据类型4.运算符及表达式三、运算符与赋值语句1.逻辑运算符2.关系运算符3.等式运算符4.移位运算符5.赋值语句6.块语句总结一、Verilog设计方法Verilog的设计多采用自上而下的设计方法(top-down)。即先定义顶层模块功能,进而分析要构成顶层模块的必要子模块;然后进一步对各个模块进行分解、设计,直到到达无法进一步分解的底层功能模块。设计流程:二、模块的结构原创 2021-10-17 14:44:08 · 1708 阅读 · 0 评论

分享

分享