前言

DDR3控制器MIG学习

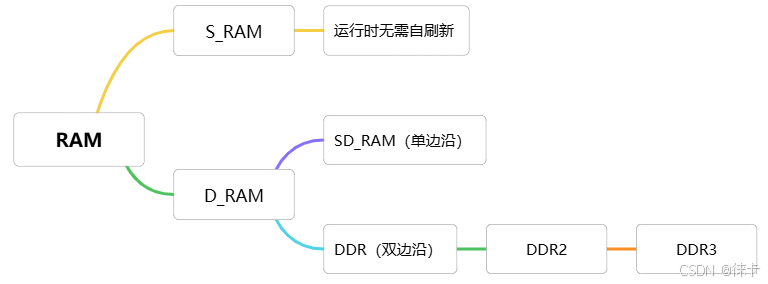

1、RAM分类

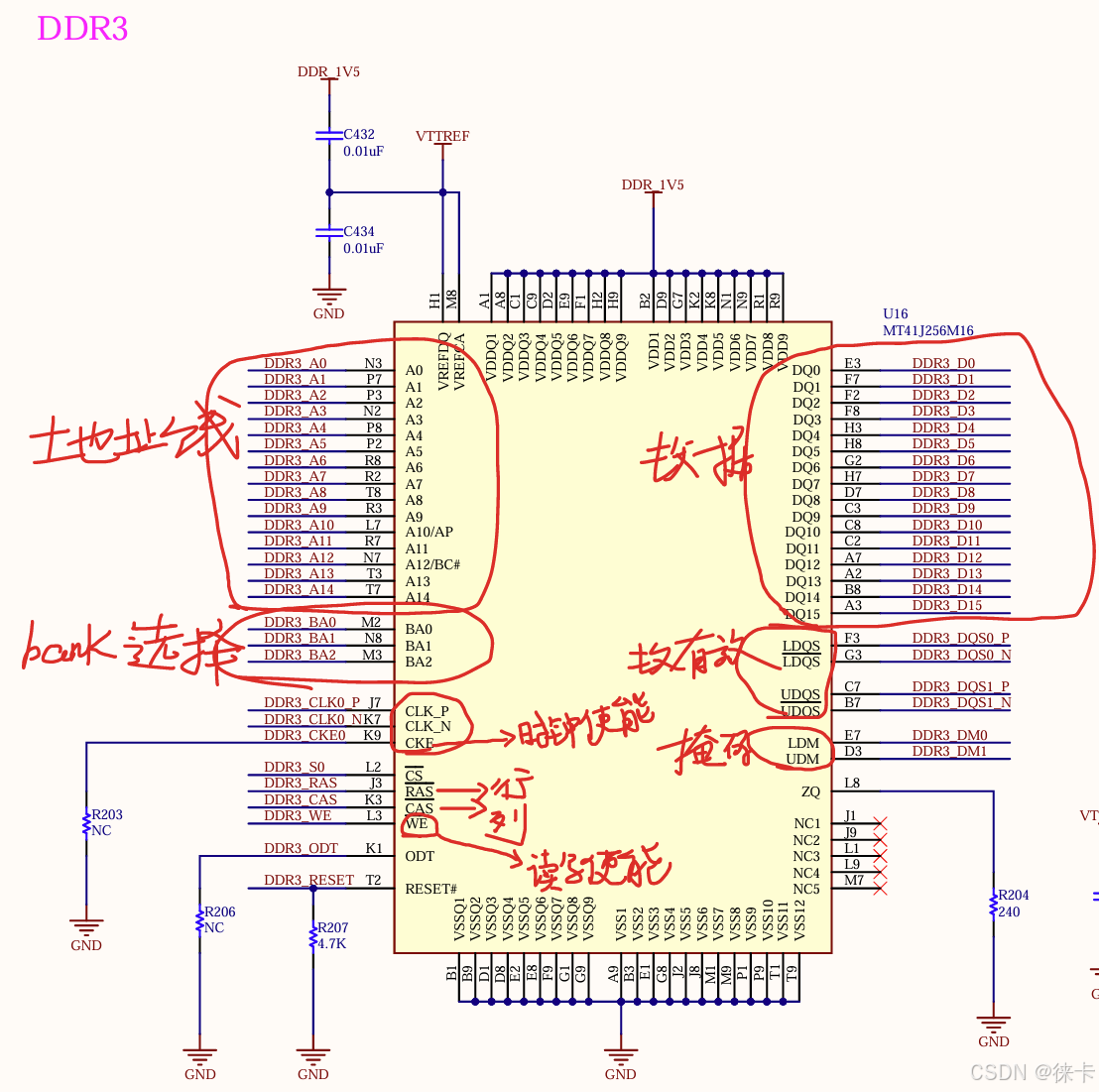

2、DDR3信号

本次使用的是镁光MT41J256M16HA-093型号,MT41J系列,容量为256×16(数据宽度) = 4096Mb,速度等级为093。

故核心时钟(mig核给ddrt提供的时钟)为1066M,数据速率为2132M,用这个的好处是可以降频使用,只要不超上限即可。

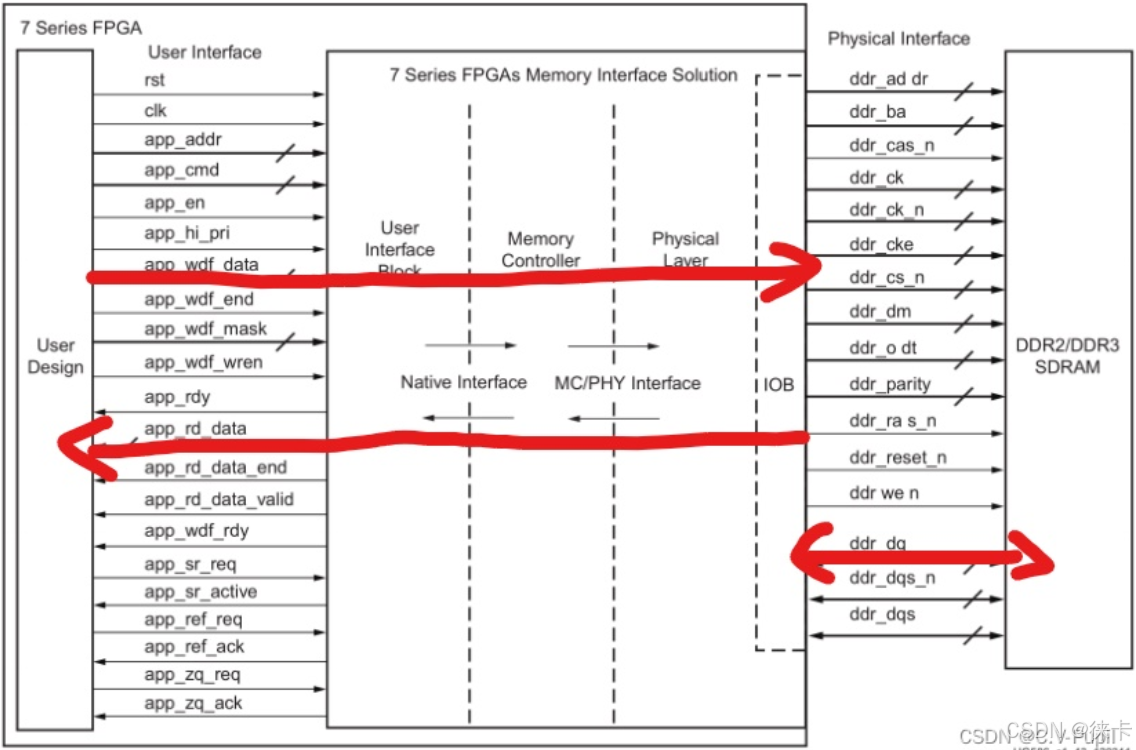

3、DDR3控制器:MIG

由于DDR3的控制时序相当复杂,为了方便用户开发DDR3的读写应用程序,Xilinx官方就提供了一个MIG IP核,它可以为用户生成一个DDR3控制器。它提供了用户接口(左侧),内部会将用户接口接收到的时序转换成DDR3所需的真正时序,并通过物理端(右侧)的接口连接到DDR3。该控制器结构如下:

相关配置参数参考该博主链接:https://zhuanlan.zhihu.com/p/457992596

4、DDR3读写时序

翻阅UG586数据手册,写时序如下

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1615

1615

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?