在设计中,高速电平互连的场合并不少见,与 TTL、CMOS电平互连一样,高速电平互连,首先需要考虑的是电平的大小及摆幅是否兼容,若不兼容,则需通过电阻网络实现电平的转换。

逻辑电平之间的互连有两种方法。

一种是直流耦合(DC Couple),即发送端和接收端直接连接,适于共模噪声小的场合,一般仅应用于板内短距离的互连。

一种是交流耦合(AC Couple),即发送端和接收端之间通过电容(在共模噪声特别大的情况下,应使用变压器)隔离,只传送交流信号,交流耦合有以下几个优点:

其一,解决了发送端和接收端之间可能存在的地平面电位差异的问题;

其二,隔离信号线路上的共模噪声;

其三,解决了发送端和接收端之间可能存在的直流偏置电平不同的问题。因此交流耦合适用于跨单板、远距离走线、共模噪声大、直流偏置电平不同等场合。

1. LVDS 与 LVDS

1)直流耦合

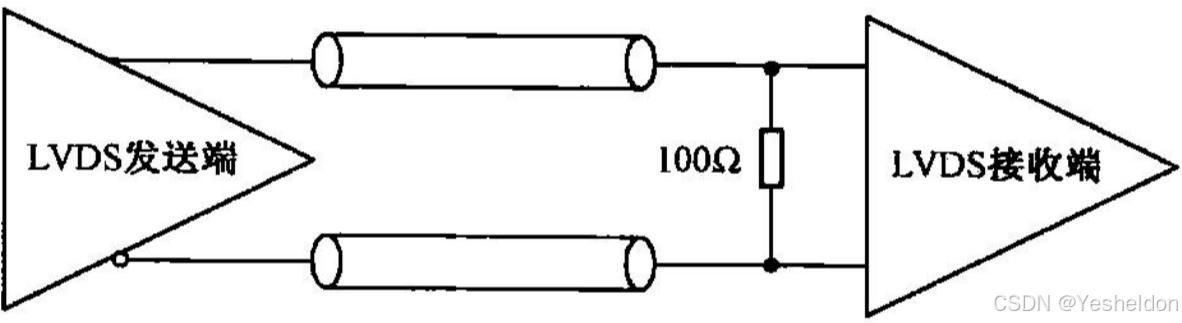

如下图所示为LVDS-LVDS直流耦合示意图。

LVDS-LVDS 的直流耦合较简单,仅需在接收端用100Ω电阻实现终结即可,在PCB设计时应将该电阻紧密地放置在接收端的输入引脚附近。同时,设计者应核对接收端器件是否已内置100Ω终结电阻,若已内置,则不应再增加外部终结电阻。

2)交流耦合

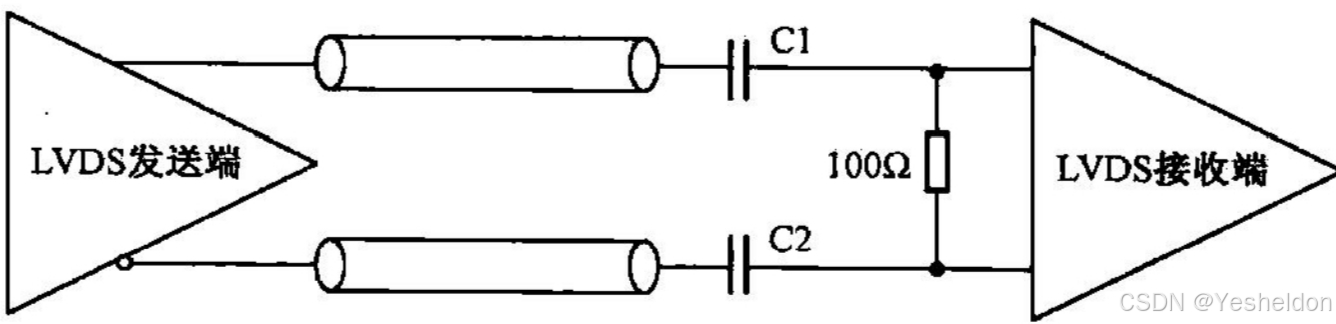

如下图所示为LVDS-LVDS交流耦合示意图。

对于 LVDS-LVDS交流耦合,在PCB设计时应注意将C1和C2靠近接收端方向放置,但无需像100Ω终结电阻那样紧密地靠近接收端器件的输入引脚。为支持传输线路上长0和长1的数据比特位(例如,100000001、0111111110这样的码型,存在较长的连续0或连续1的序列),C1和C2容值不能太小,一般取0.1μF。

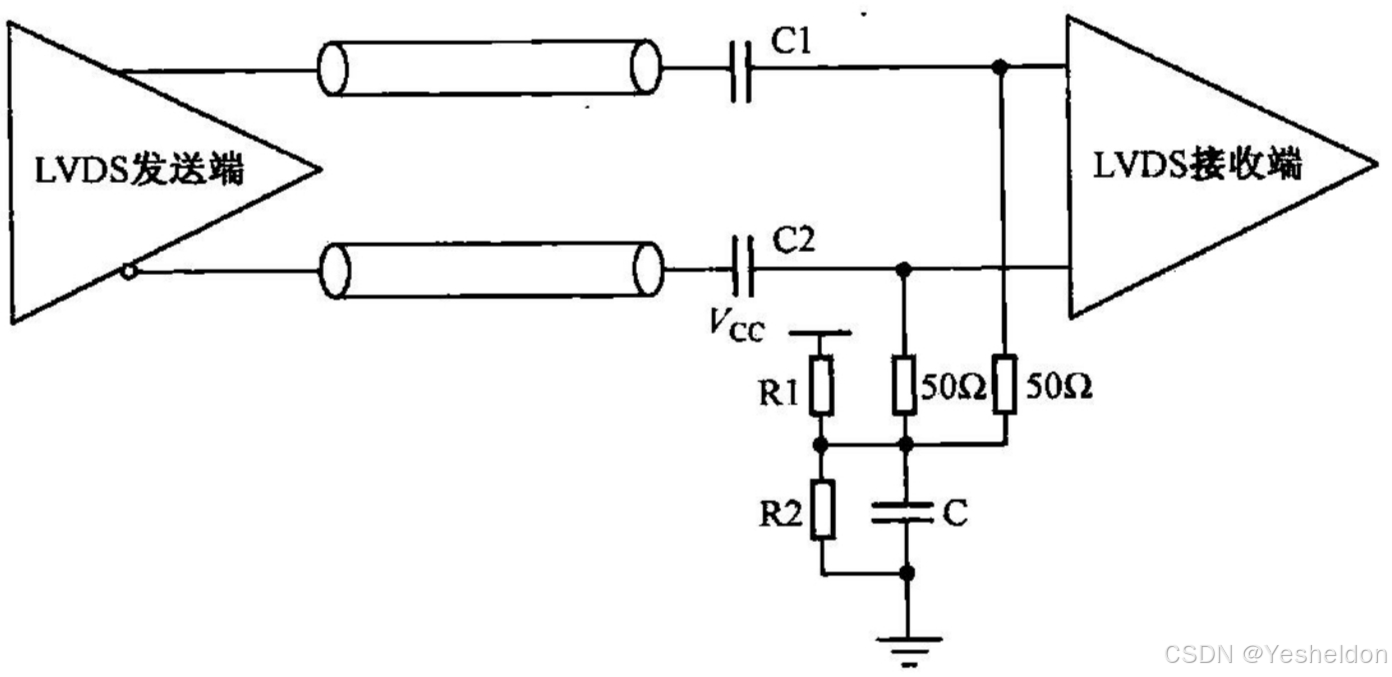

在交流耦合时,直流通路被隔离,设计者应考察接收端器件是否提供直流偏置,若不提供直流偏置,应采用如下图所示的电路通过R1、R2组成的分压电路,Vcc 为接收端提供直流偏置。由之前章节内容可知,

LVDS接收端对直流偏置电平的要求很松,只要处在0.227~2.173V的区间即可,因此一般取中间值1.2V 作为直流偏置电平。电容C的作用是为共模噪声提供到GND的低阻抗通路。对R1和R2的取值,除考虑直流偏置电平的要求外,还应考虑在电阻上产生的功耗。

2. LVPECL 与 LVPECL

1)直流耦合

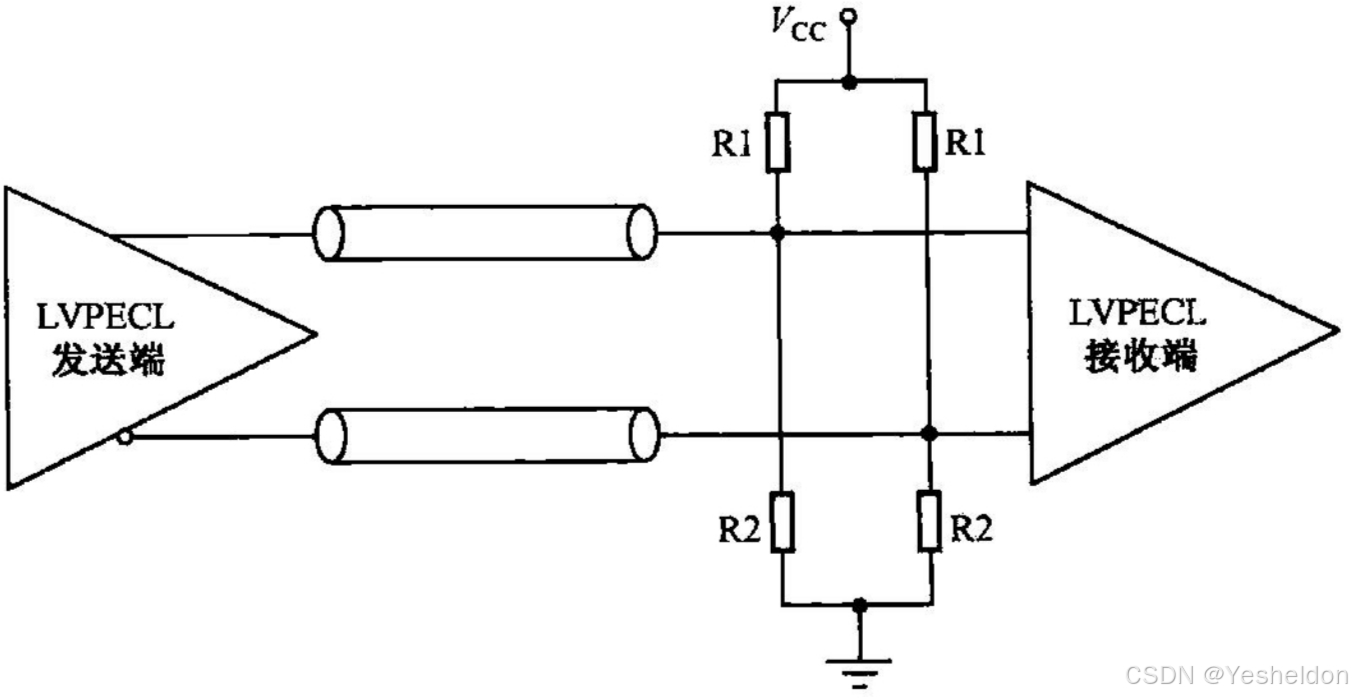

LVPECL的输出端需端接50Ω电阻连接到Vcc-2V,为节省电源种类,可采用电阻分压网络实现该偏置电平,如下图所示。

要求R1和R2组成的分压网络完成以下两个功能:

①获得Vcc-2V的偏置电平。

②提供等效50Ω的端接电阻。

因此,R1和R2应满足以下两个公式:

Vcc*R2/(R1+R2)=Vcc-2 (3.7)

R1//R2= 50 (3.8)

当 Voc=3.3V时,R1=130Ω,R2=82Ω。

在设计时应注意两个问题:其一,在PCB设计时,将R1和R2紧密地放置在接收端器件的输入引脚附近;其二,在电源设计时,应考虑 Vcc在R1和R2上消耗的功率,当Vec=3.3V时,对一个LVPECL接收端口,在分压电阻上的最大功耗可达51mW。

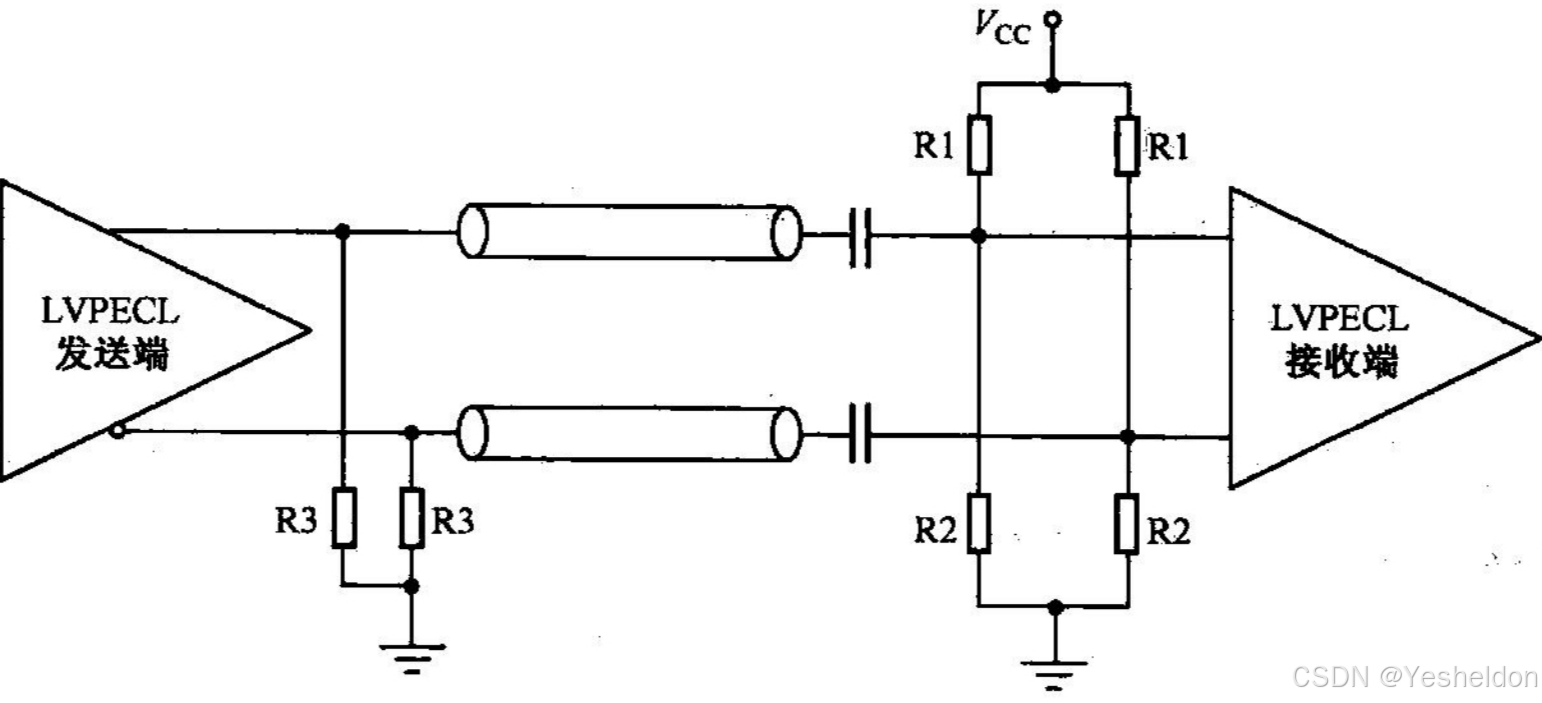

2)交流耦合

如下图所示,R1和R2的选择方法与LVPECL-LVPECL直流耦合相同。

在前面章节提到,LVPECL输出端的共模电平为 Vcc-1.3V,且输出端输出直流电流14mA。交流耦合时,直流通路被阻断,因此需利用R3以保证稳定的共模电平及提供14mA电流的直流回路。R3的阻值计算公式为:

R3=(Vcc-1.3)/14mA (3.9)

当Vcc=3.3V时,R3取值为143Ω。为保证信号质量,R3阻值可做略微调整,但最大值不应超过200Ω。

3. CML 与 CML

CML与CML之间的互连非常简单,直接连接即可。板内信号互连可采用直流耦合,走线距离较远或跨板互连时,应采用交流耦合。

4. LVDS 到 LVPECL

由于LVDS的输出电平以GND为参考,而LVPECL的输入电平以Vcc为参考,因此对于 LVDS到LVPECL的连接,建议采用能隔直流的交流耦合方式,以避免由于收发双方共模偏置电平不同而造成的影响。

为了加强读者对共模偏置电平的理解,此处仍先介绍直流耦合方式。

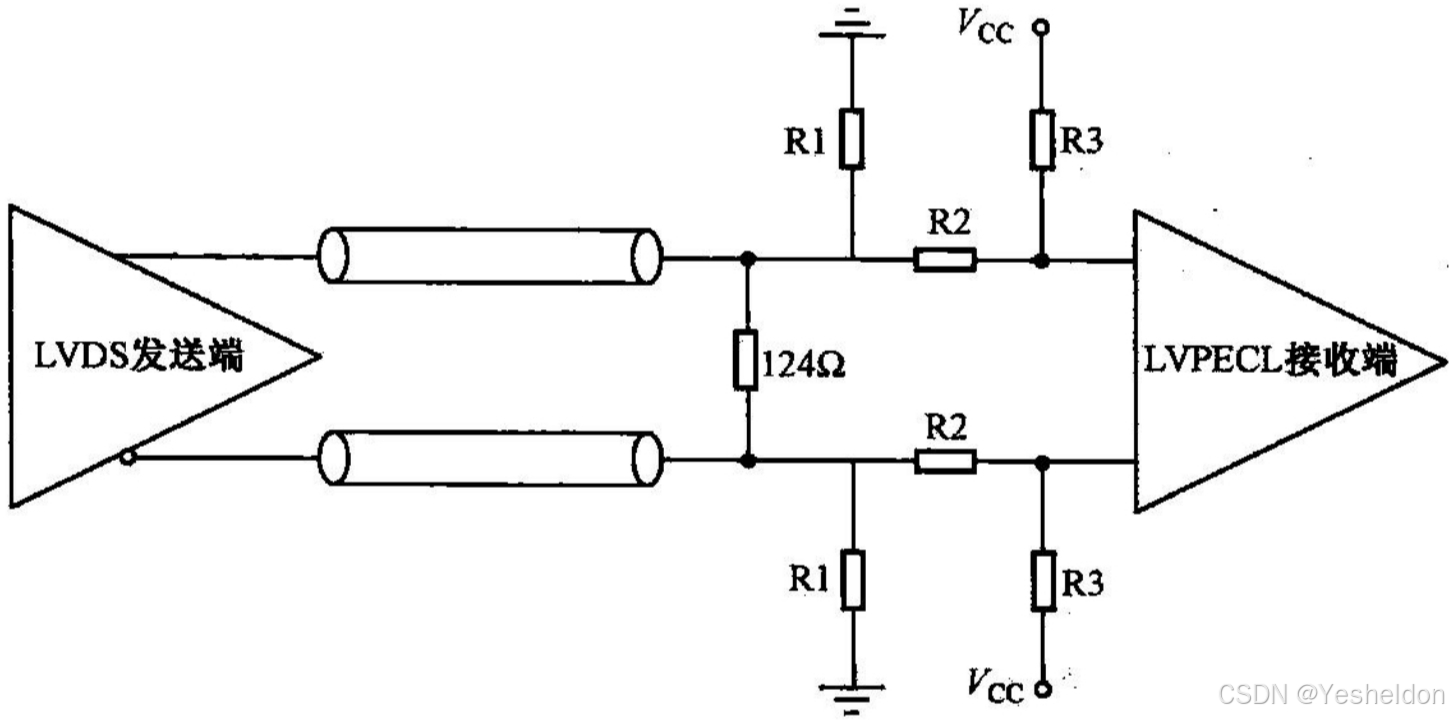

1)直流耦合

如下图所示为LVDS-LVPECL直流耦合的示意图。

LVDS与LVPECL的直流耦合,需满足以下要求:

(1)偏置电平的转换。LVDS输出端共模偏置电平的中间值为1.2V,而 LVPECL输入端的共模偏置电平为Vcc-1.3V。因此,电阻网络需满足以下等式:

Vcc*R1/(R1+R2+R3)=1.2V (3.10)

Vcc*(R2+R3)/(R1+R2+R3)=Vcc-1.3V (3.11)

(2)线路阻抗要求。差分对信号路径上,单端对地阻抗应满足50Ω的要求,同时,该阻抗也是为了满足LVDS的100Ω终结电阻的要求。因此电阻网络需满足以下等式:

R3//(R1+R2)//62=50 (3.12)

当Vcc=3.3V时,得到R1=374Ω,R2=249Ω,R3=40Ω。

在差分对信号之间增加的124Ω并联电阻,其作用是减小电阻网络上的功耗。若不增加该电阻,电阻网络取值为:R1=76Ω,R2=51Ω,R3=82Ω。电阻取值越小则功耗越大,增加并联电阻后,可增大电阻R1~R3的取值,从而降低了功耗。

(3)电平摆幅的匹配。LVDS的输出摆幅|Vod|为350mV,LVPECL对输入摆幅Vm的要求随不同厂家器件而不同。应满足以下不等式:

|Vod| *[Rg /(R2+R3)]> Vid (3.13)

将数值代入,结果为Vid<216mV,即只有当接收端 LVPECL器件对输入摆幅Vid的要求小于216mV时,才能采用以上直流耦合电路。

由于直流耦合的电阻网络较复杂,因此在LVDS 到LVPECL的电平转换中,一般采用交流耦合。

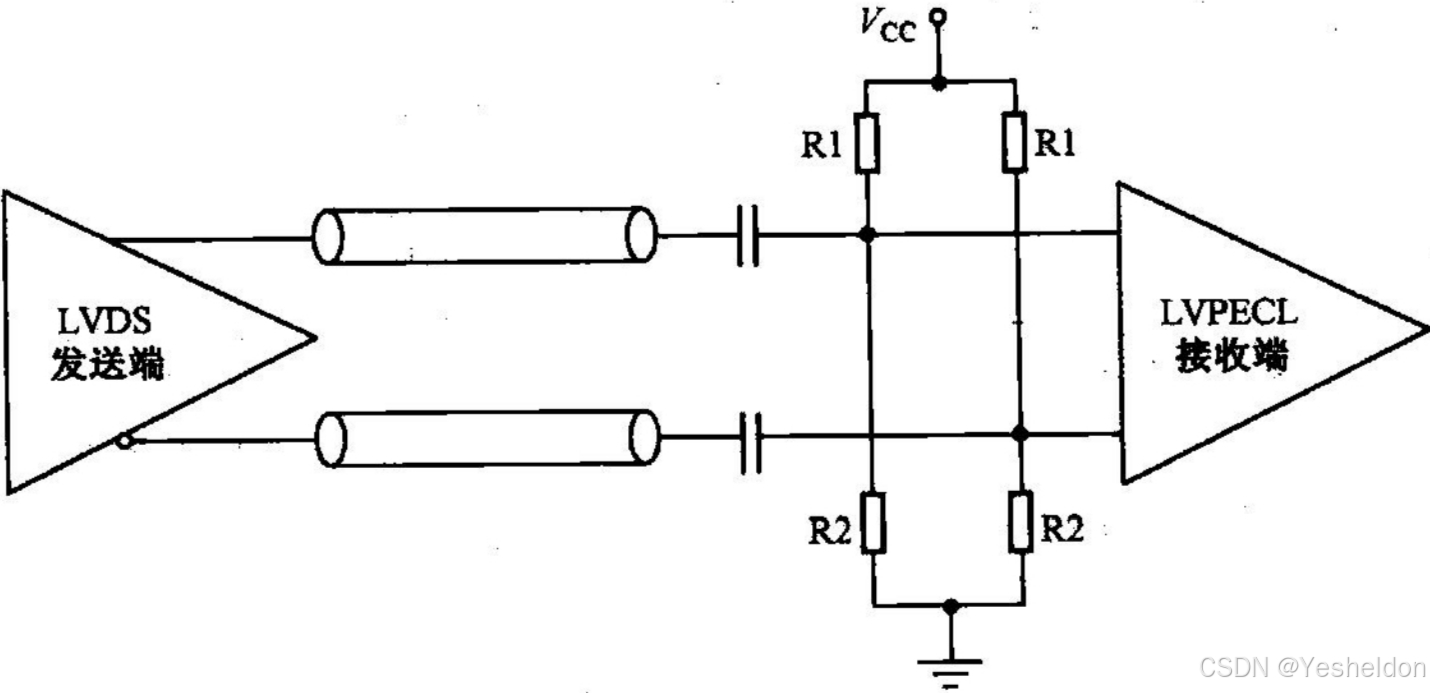

2)交流耦合

如下图所示,R1和R2组成的电阻网络,应满足以下要求:

(1)为LVPECL输入端提供Vcc-1.3V的共模偏置电平。

(2)为LVDS差分对输出端提供100Ω的终端匹配(即单端对地电阻为50Ω)。

因此,R1和R2应满足以下两个等式:

Vcc*R2/(R1+R2)=Vcc-1.3 (3.14)

R//R2=50 (3.15)

当Vcc=3.3V时,得到电阻网络的取值为:R1=82Ω,R2=130Ω。

为减小在电阻网络上的功耗,可在差分对信号线上,靠近接收端增加一个100Ω并联电阻,由该电阻满足第二个要求,而R1和R2仅需满足要求(1)即可,从而增大了:R1和R2的阻值,减小了在电阻网络上的功耗。

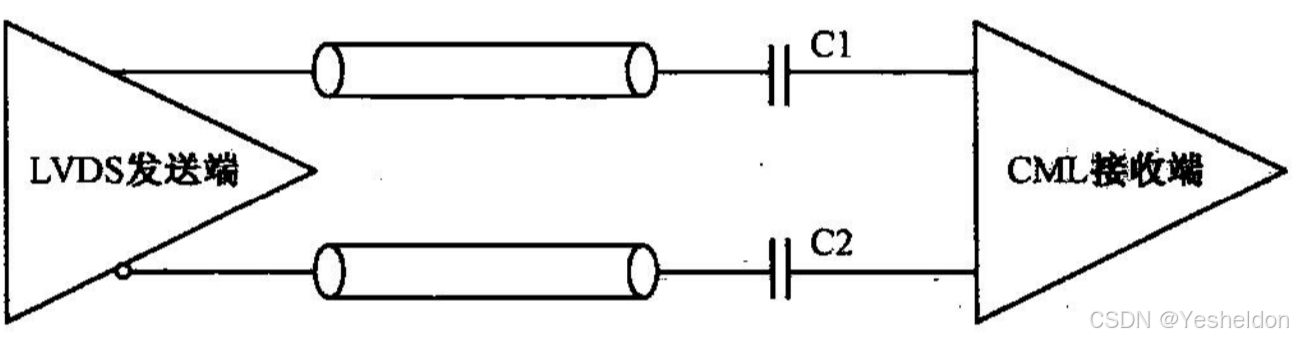

5.LVDS到CML

与LVDS到LVPECL连接的情况类似,LVDS和CML的共模偏置电平不同,一般推荐采用交流耦合方式,如下图所示。

根据前面章节,CML的输入端已内置上拉到Vcc的50Ω电阻,可满足LVDS端接电阻100Ω的要求,因此在信号线上无需外加端接电阻。

在应用中,设计者应核对 LVDS的输出摆幅 Vod与CML的输入摆幅 Vid,是否满足以下要求:

|Vod|>Vid (3.16)

6. LVPECL到 LVDS

1)直流耦合

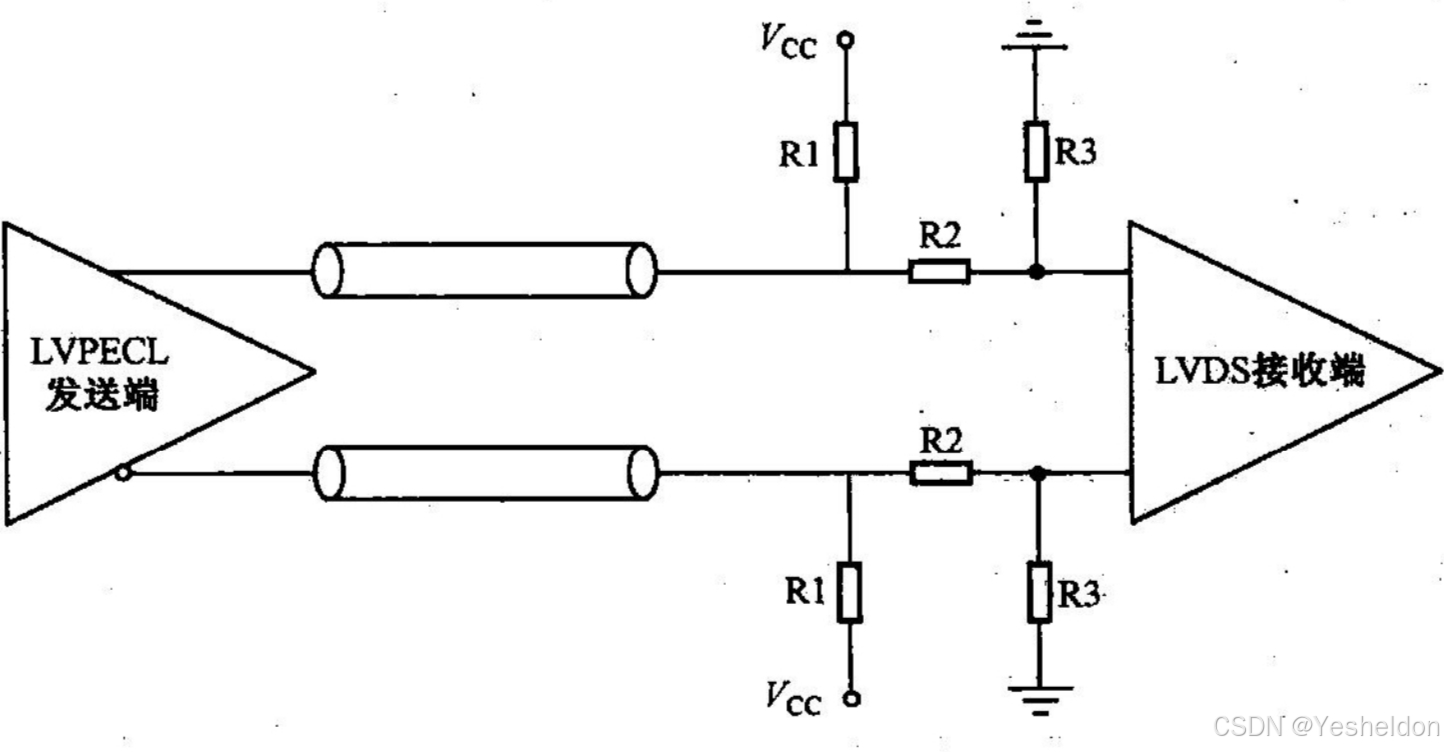

如下图所示为LVPECL-LVDS直流耦合的示意图。

与 LVDS-LVPECL 的直流耦合类似,LVPECL 到 LVDS 的连接同样需要满足以下要求:

(1)为LVPECL输出端提供Vcc-2V的偏置电平。即要求满足式:

Vcc*(R2+R3)/(R1+R2+R3)= Vcc-2V (3.17)

该等效电阻同时满足LVDS对输入端端接100Ω电阻的要求。即要求满足式:

(2)差分信号阻抗匹配。为实现线路上的阻抗匹配,电阻网络的等效电阻应为50Ω,

R1//(R2+R3)=50 (3.18)

电阻网络取值为:R1=120Ω,R2=58Ω,Rg=20Ω。

(3)电平摆幅的匹配。LVPECL的输出摆幅|Vod|的值随不同的厂家器件而不同,LVDS对输入摆幅Vid的要求是100mV。即要求满足以下不等式:

|Vod|*R3/(R2+R3)]>100mV (3.19)

一般,LVPECL的IVopl最小值为800mV,将各数值代入,满足式(3.19),电平摆幅满足要求。

2)交流耦合

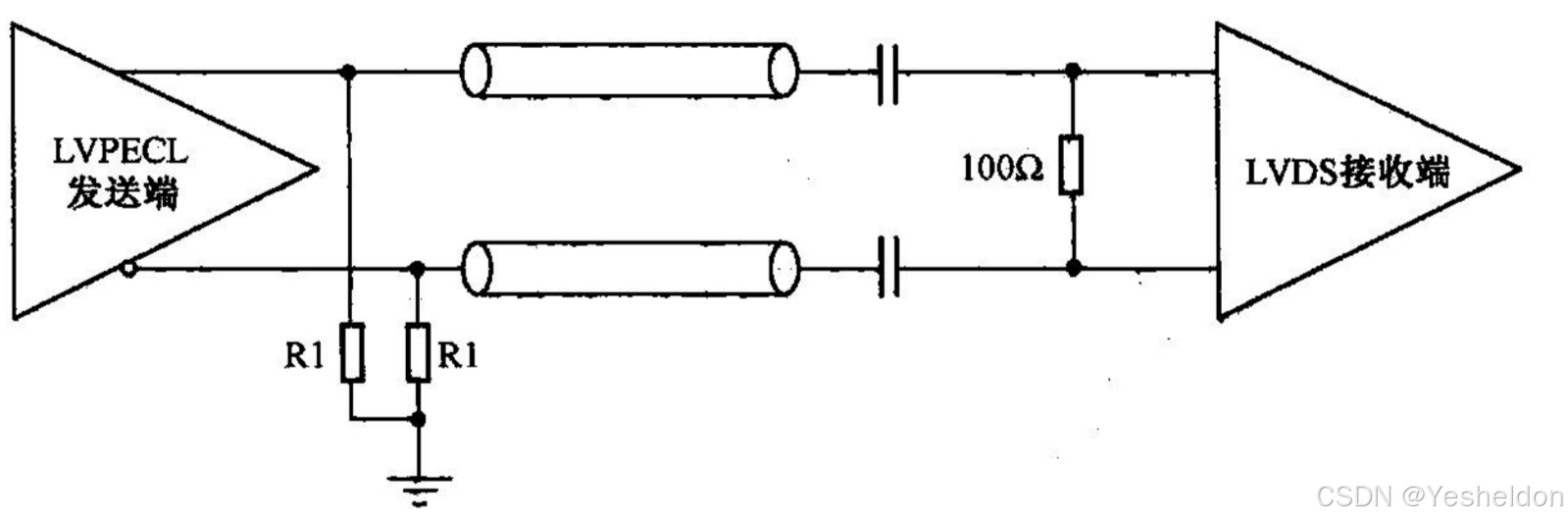

如下图所示为LVPECL-LVDS交流耦合的示意图。

LVPECL-LVDS的交流耦合应满足以下要求:

(1)为LVPECL输出端的14mA直流电流提供回路。该回路由R1提供,R1的阻值计算方法与LVPECL-LVPECL交流耦合相同。

(2)在LVDS输入端,添加100Ω端接电阻。

(3)电平摆幅的匹配。一般LVPECL的输出摆幅 |Vod|较大,而LVDS的输入摆幅Vid较小,为保护LVDS输入端口,可在线路上串电阻以实现衰减。

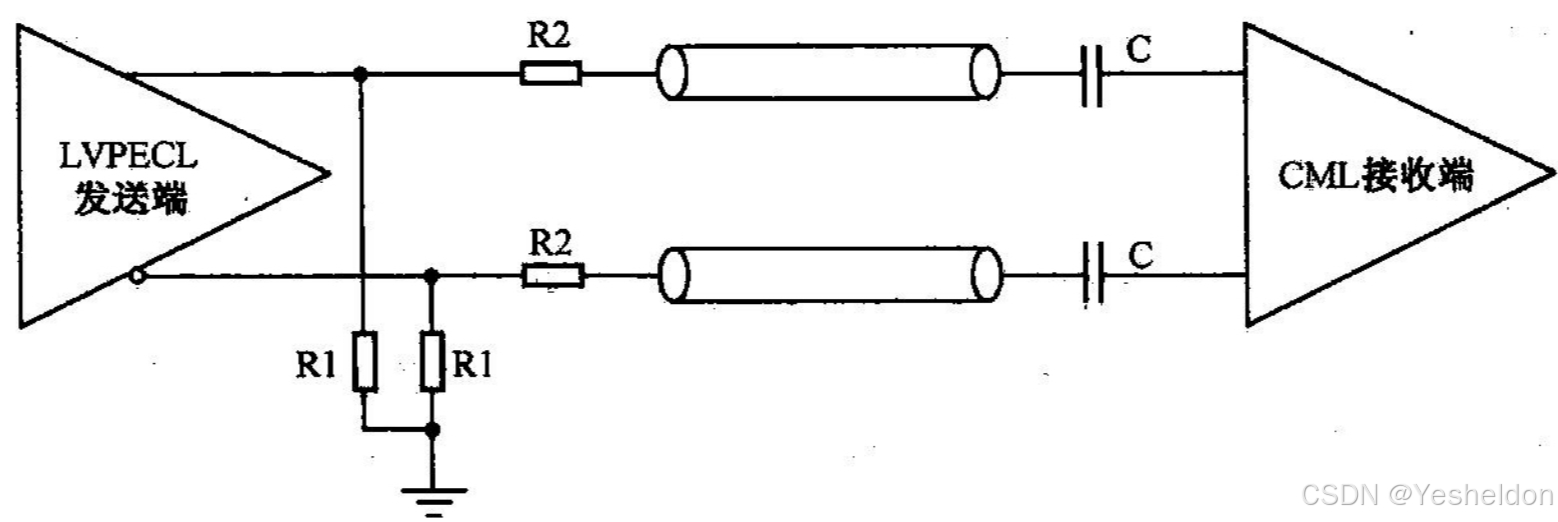

7. LVPECL 到 CML

由于LVPECL和CML的共模偏置电平不同,直流耦合电路复杂,不适于高速应用,因此LVPECL到CML的连接一般采用交流耦合。

如下图所示,LVPECL-CNL的交流耦合应满足以下要求:

(1)为 LVPECL输出端的14mA 直流电流提供回路。该回路由R1提供,R1的阻值计算方法与LVPECL-LVPECL交流耦合相同。

(2)CML输入端的阻抗匹配。根据前面章节内容可知,CML输入端的匹配电阻已内置,无需外部端接。

(3)电平摆幅的匹配。LVPECL输出摆幅|Vod|较大,为保护CML输入端口,应串电阻R2以衰减差分对信号。例如,LVPECL的输出摆幅 |Vod|为800mV,而CML输入摆幅的最低要求为 400mV,一般而言,应将 LVPECL 的输出摆幅衰减三分之一,则应满足式(3.20)[式(3.20)中,50Ω指单端对GND的阻抗值]:

当R1取150Ω时,可得R2=25Ω。

R1/(R1+R2+50)= 2/3 (3.20)

需注意,在差分信号线上增加衰减电阻R2后,将导致线路上的阻抗不匹配,此时应对R2的取值做出权衡。

8.CML到LVDS

高速电路设计中一般不会出现CML到LVDS连接的场合,此处略过。

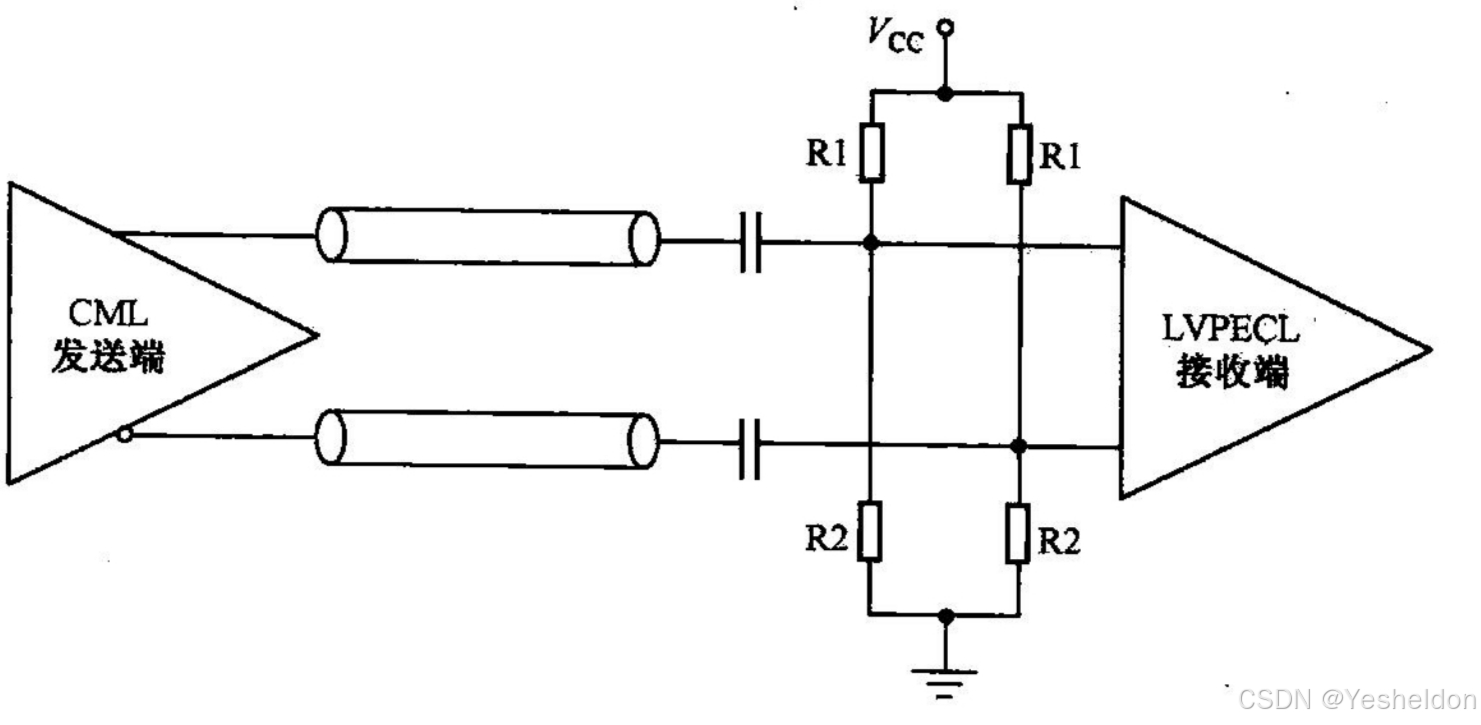

9.CML 到LVPECL

由于CML和LVPECL的共模偏置电平不同,对于CML到 LVPECL的连接,一般采用交流耦合。

如下图所示,CML到LVPECL的交流耦合应满足以下要求:

(1)在LVPECL接收端,由R1和R2组成电阻网络,电阻网络的作用及阻值计算方法与 LVPECL-LVPECL直流耦合相同。

(2)电平摆幅的匹配。当CML器件的输出摆幅|Vod|较大,为保护LVPECL输入端,可在差分对信号线上串联电阻,以衰减差分对信号。串电阻后可能导致线路上阻抗不匹配,设计者应相应地做出权衡。

10.总结

在高速电平互连时,应着重注意以下几个方面:

(1)端接匹配电路的设计。例如,LVDS 接收端要求提供 100Ω端接电阻;LVPECL 接收端应端接电阻以实现50Ω单端对地阻抗。当不满足阻抗匹配要求时,线路上将出现反射,并可能产生共模噪声。

(2)端接电阻的放置位置。在PCB设计时,输出端的端接电阻应靠近输出端器件的引脚放置,输入端的端接电阻应靠近输入端器件的引脚放置。

(3)要求满足收发双方电平摆幅的匹配。当输出摆幅小于输入摆幅的电平要求时,不能实现互连;当输出摆幅远大于输入摆幅的电平要求时,为保护接收端器件,应在线路上串联电阻以实现衰减。

(4)直流耦合时需满足收发双方共模偏置电平的要求。例如,LVDS输出端共模偏置电平的中间值为1.2V,而LVPECL输入端的共模偏置电平为Vcc-1.3V,需采用电阻网络实现电平转换。

(5)交流耦合电容的容值和位置。交流耦合电容一般取0.1μF,并靠近接收端方向放置。

(6)交流耦合时接收端共模偏置电平是否得到满足。例如,LVDS 接收端共模偏置电平应处在0.227~2.173V的区间,而LVPECL接收端共模偏置电平的中间值要求为Vcc-1.3V。

(7)交流耦合时在发送端是否提供了电流源的回路。LVPECL发送端内置14mA电流源,当交流耦合时,电流源回路被阻断,因此,需在发送端补充一条电流回路。

(8)电阻网络上的功耗。有时电阻网络需同时满足共模偏置电平和线路阻抗的要求,以至于电阻取值较小,电阻网络的功耗较大,此时可以采用在 LVDS-LVPECL直流耦合中提到的方法,通过在差分对信号线之间增加一个阻值较小的并联电阻,以增大电阻网络的电阻阻值,从而达到减小功耗的目的。

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?