0.摘要

汽车电子LIN总线不同于CAN总线。

LIN总线基本上是CAN总线的廉价补充,相比于CAN总线,它提供较低的可靠性和性能。同时LIN总线也是一个应用非常广泛的网络协议,并且越来越受欢迎。

再一次,我们准备了一个关于LIN总线的简要介绍。以下涉及多个方面的主题与研究内容。本文将结合专业知识,以一种非常简单的方式解释LIN总线和LIN协议,以使其尽可能通俗易懂。

1.什么是LIN总线?

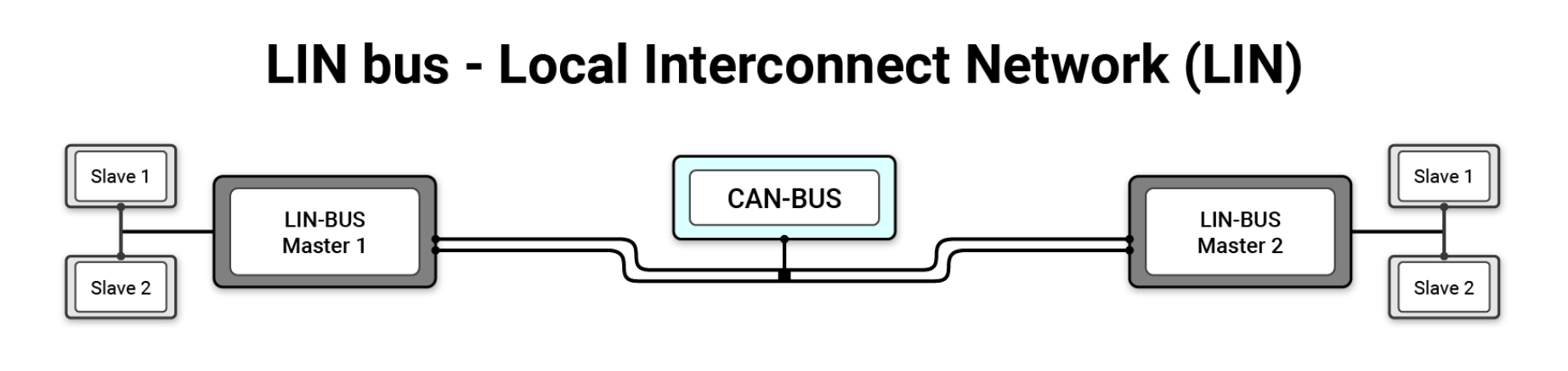

LIN总线代表本地互联网络(Local Interconnect Network (LIN) ),用于车辆组件之间的通信。它也被称为CAN总线的补充。LIN协议具有很高的成本效益,比CAN总线便宜得多。然而,它提供了较低的性能,不像CAN 总线那样可靠。

当CAN总线太昂贵而无法为车辆中的每个组件实现应用时,LIN总线应运而生。或者说LIN Bus被创造出来是为了来应对这个挑战,并且已经完美地完成了既定目标。

2.什么是LIN协议?

LIN协议是电子设备的有线通信协议。它由一个主节点和一个或多个从节点组成。每个LIN帧由两对组成——报头和响应。报头总是由LIN主节点发送,响应由一个专用的LIN从节点或LIN主节点发送。此外,Lin协议使用两种总线状态,睡眠模式和活动模式。

LIN总线是一种低成本的协议,具有部分替代can总线系统的作用,用于车辆部件之间的通信。也称为CAN总线的补充。

3.LIN Bus的主要特点

-

Low-cost option.

-

Single wire with 1-20 kbit/s at maximum 40m bus length (+ground).

-

Operating voltage 12V.

-

Frequently used in vehicles for wipers, air conditioners, steering wheels, windows, and so on.

-

LIN clusters contain 1 master and up to 16 nodes.

-

The latest vehicles have more than 10 nodes.

-

Several data lengths (2,4 and 8 bytes).

-

Guaranteed latency time with time-triggered scheduling.

-

Sleep mode and wake-up support.

-

The physical layer is based on ISO 9141 - K-line.

-

LIN protocol support error detection and configuration.

4.LIN 总线如何工作

LIN总线也可以用于车辆的电池电源线,使用LIN over DC (DC-LIN)收发器,这被标准化为ISO/AWI 17987-8。如今,LIN Bus在所有现代车辆中几乎都是标准化的。LIN总线正在使用的主要有如下几种情形:

-

Sensors for position and temperature.

-

Speed and pressure.

-

Cruise control.

-

Wipers.

-

Radio.

-

Climate control.

-

Small motors.

-

Side mirrors.

-

Seat control.

-

Locks.

-

Rain sensors.

-

Headlights.

-

And more.

此外,LIN Bus还被用于家用电器,如洗衣机、炉灶、冰箱等。有相关的预测表明,LIN总线及其应用的需求还会继续增加。电子控制单元ECU是许多其他应用中的常见应用之一。

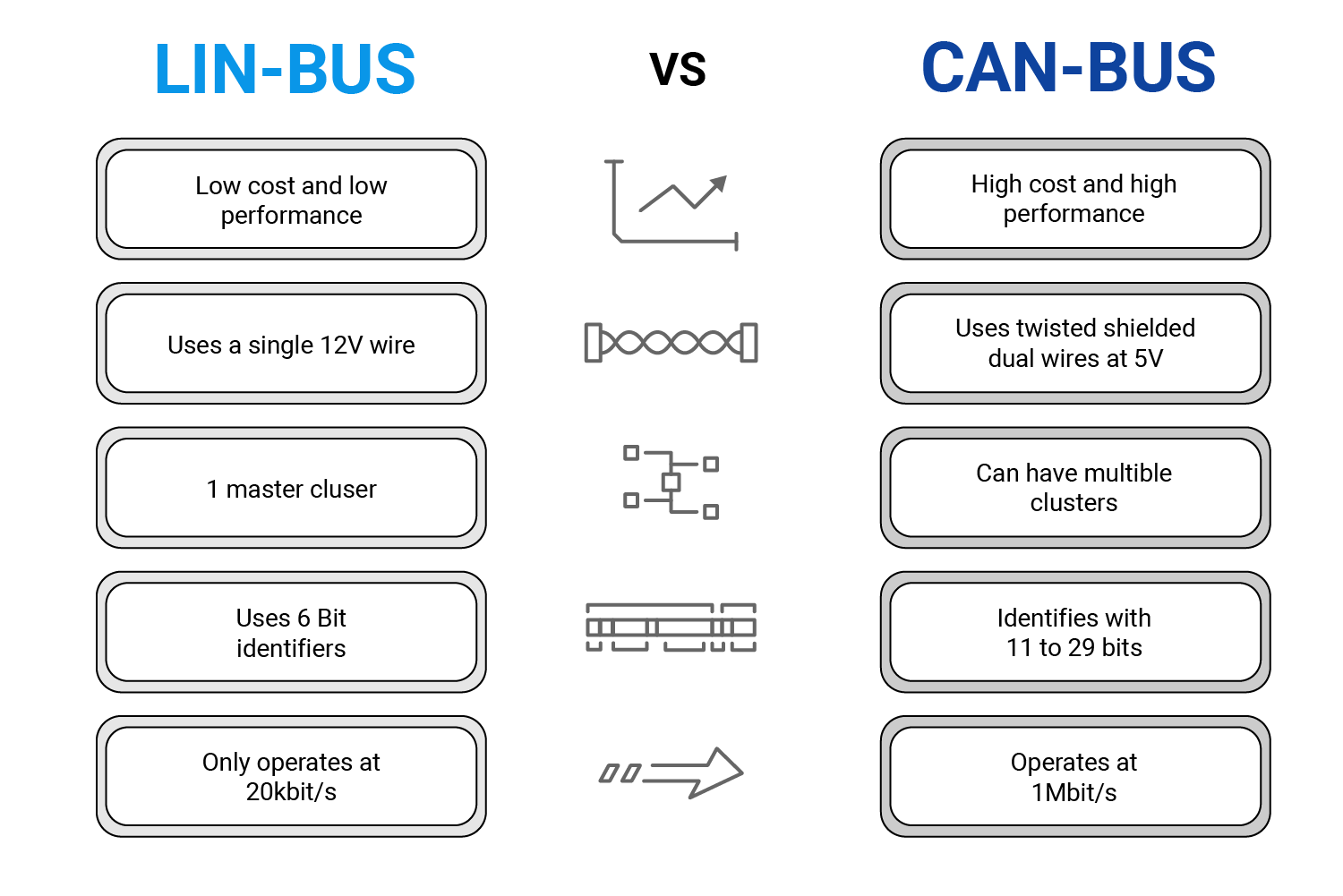

5.LIN Bus 与 CAN Bus对比

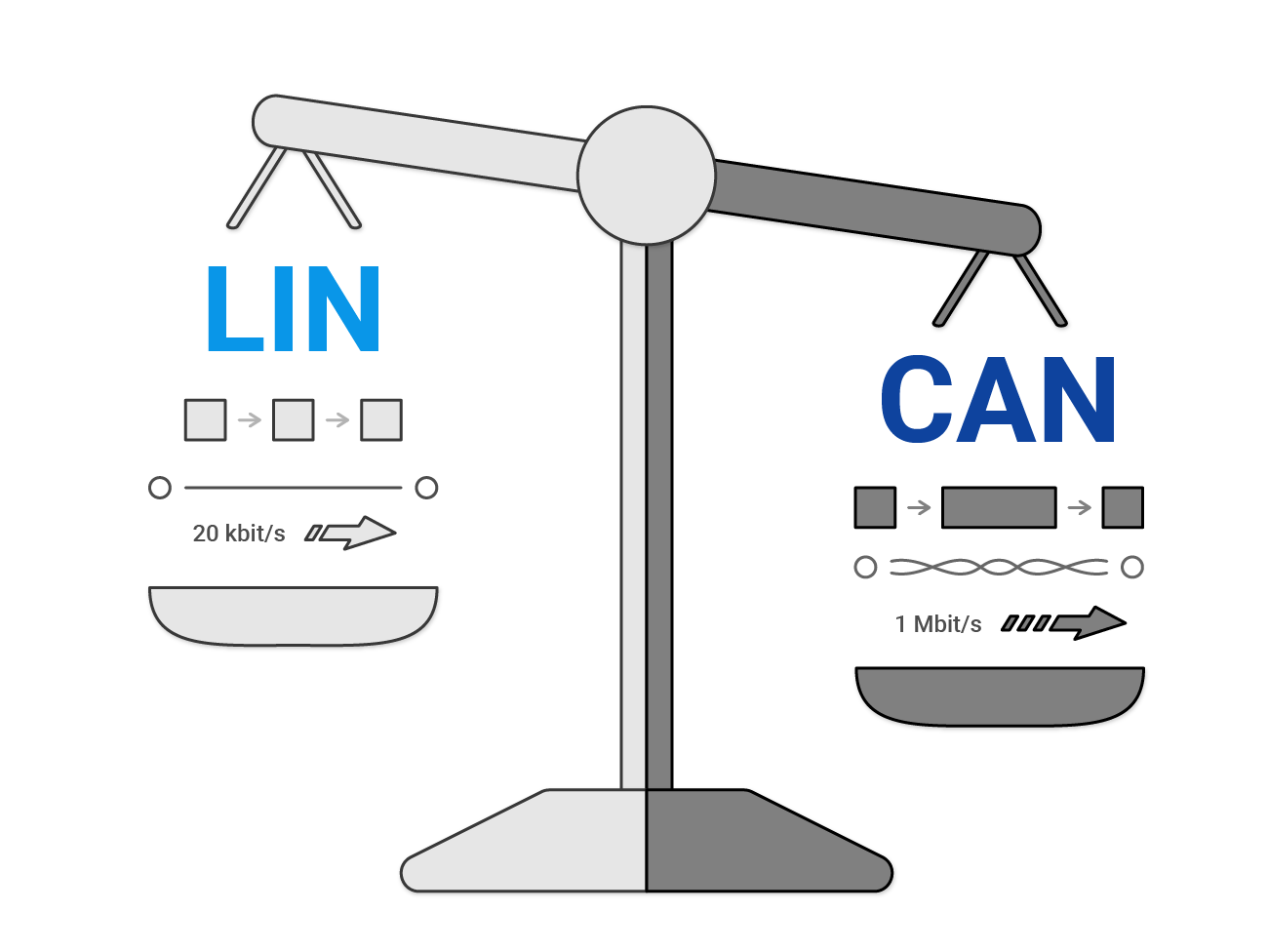

下面是LIN总线接口和CAN总线接口的主要差异,提到了它们的主要区别以及它们的主要优点。

Lin Bus 接口

-

Lower cost.

-

Latency time - more predictable network.

-

Overall implementation - simpler to implement than CAN.

-

Typically, LIN master works as a gateway to the CAN Bus.

-

LIN clusters have a single master.

-

LIN is settled - not event-driven.

-

Uses single wire 12V.

-

LIN offers a max of 20 kbit/s.

CAN Bus 接口

-

Uses twisted shielded dual wires 5V.

-

Uses 11 or 29-bit identifiers.

-

Very complex and robust interface.

-

CAN could have multiple masters.

-

CAN offer up to 1 Mbit/s.

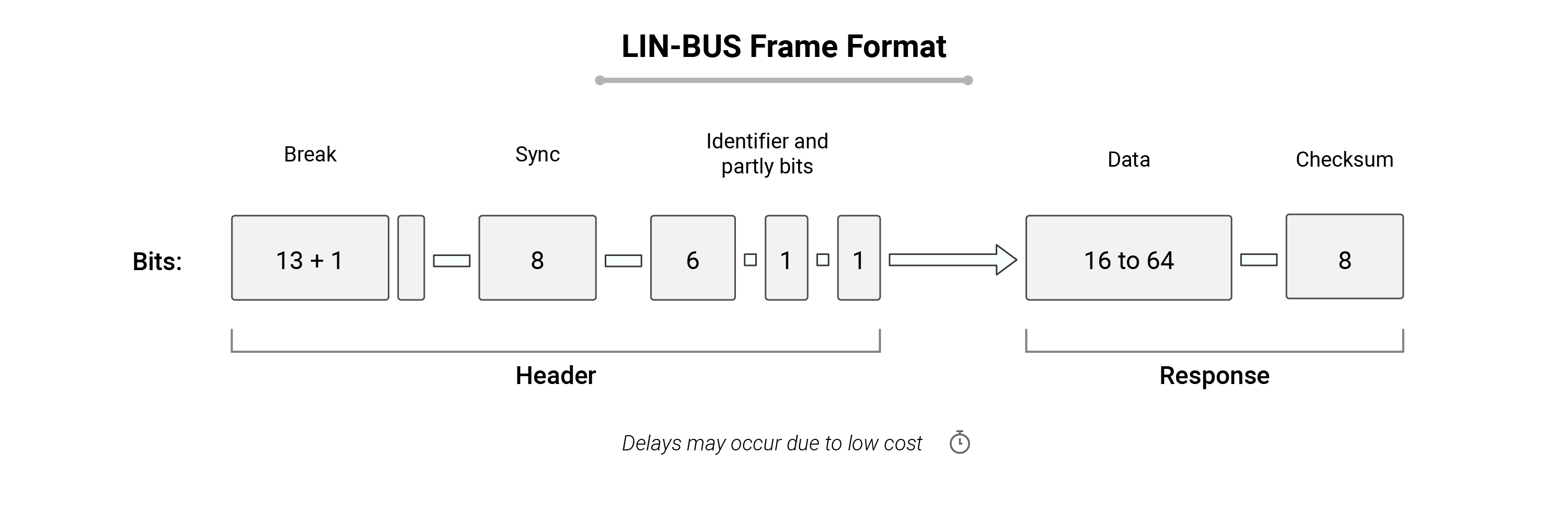

6.LIN总线数据帧格式

简单地说,LIN总线消息帧由一个报头和一个响应组成。一般来说,LIN主节点通常向LIN总线发送一个报头,然后触发一个从节点。从节点发送最多8个数据字节作为响应。LIN帧格式用下图说明。

现在我们将详细解释LIN帧格式的具体部分。

中断

-

The Sync Break Field (SBF), also known as just Break is a minimum of 13 + 1 bit long.

-

Commonly used as 18 + 2 bits.

-

Operates as a start of the frame.

同步

-

Is 8 bits long.

-

Has a predetermined value of 0x55.

-

Its structure allows the LIN nodes to determine the time between rising and/or falling edges.

标识位

-

Is 6 bits long and followed by 2 parity bits.

-

The ID operates as an identifier for each LIN message.

-

Slaves determine the validity of the ID field and operate accordingly - ignore the subsequent data transmission, listen to the data transmitted from another node, and publish data in response to the header

此外,通常在同一时间使用一个从节点来获取信息。这意味着没有碰撞风险,也不需要采取仲裁。6位允许64个id,其中id 60-61用于诊断。

7.LIN Bus消息帧格式

LIN消息由标识符字节、校验和字节、同步字节和同步字段组成。

Frame types

-

Unconditional frame - 0-59 ID dec, 00-3B ID hex.

-

Event-triggered frame - 0-59 ID dec, 00-3B ID hex.

-

Sporadic frame - 0-59 ID dec, 00-3B ID hex.

-

Diagnostic frame - 60-61 ID dec, 3C-3D ID hex.

-

User-defined frame - 62 ID dec, 3E ID hex.

-

Reserved frame - 63 ID dec, 3F ID hex.

8.LIN Description File (LDF)

LIN网络由LDF描述,其中包含有关帧和信号的信息。LDF用于在主服务器和从服务器上创建软件。

使用时可能需要将原始LIN总线数据解码为物理值,作为LIN数据工作流的一部分。

要将原始数据解码为可读形式,需要从LIN帧有效负载中提取LIN信号。LIN总线解码与CAN总线解码非常相似,需要相同的信息。

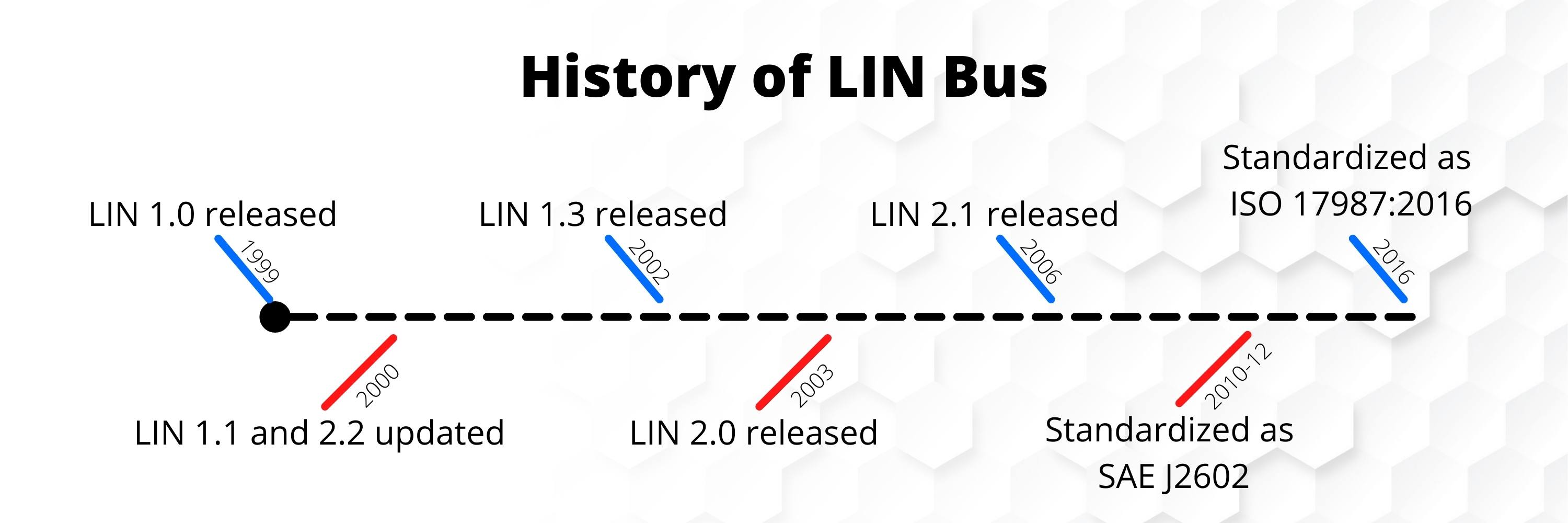

9.LIN Bus 的历史

为了更好的理解LIN总线的由来, 创建LIN Bus的历史时间线如下:

-

1999 - LIN 1.0 released by the LIN Consortium (BMW, Volkswagen Group, Volvo Cars, Audi, and Mercedes-Benz)

-

2000 - The LIN Bus protocol was updated - LIN 1.1 and LIN 2.2

-

2002 - LIN 1.3 was released

-

2003 - LIN 2.0 was released with multiple changes

-

2006 - LIN 2.1 specification released

-

2010 - LIN 2.2A was released

-

2010 - 2012 - Based on LIN 2.0, SAE standardized LIN as SAE J2602

-

2016 - LIN standardized as ISO 17987:2016

10.LIN Bus未来展望

由于其低成本的特点,LIN Bus有望在现代汽车中得到更为普遍的应用。

自2015年以来,我们已经看到LIN总线的受欢迎程度有了巨大的增长,预计还会增加更多。

此外,基于它的低成本。LIN总线有可能在J1939中也会得到使用。

本文介绍了LIN总线,一种低成本的汽车电子通信协议,与CAN总线的对比,包括其特点、工作原理、数据帧格式、历史发展及未来趋势。LIN总线因其性价比高,在现代车辆中的应用日益广泛。

本文介绍了LIN总线,一种低成本的汽车电子通信协议,与CAN总线的对比,包括其特点、工作原理、数据帧格式、历史发展及未来趋势。LIN总线因其性价比高,在现代车辆中的应用日益广泛。

5127

5127

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?