在某些高速数据存储场景下,单个NVMe IP已无法满足带宽需求,常需要多个NVMe IP并行工作以提升写入带宽,由于NVMe底层使用PCIe,而Xilinx/Altera等厂家FPGA芯片自带的PCIe硬核往往有限,比如Kintex-7芯片一般只有一个PCIe2.0硬核,此时,基于GTX等高速收发器实现PCIe软核成为一种必要方式。

目前我们正在进行PCIe软核的开发,简单介绍如下:

(1)基于 FPGA 片上高速收发器GTX(或其他)实现同等PCIe硬核功能(NVMe PCIe 2.0应用场景下)。

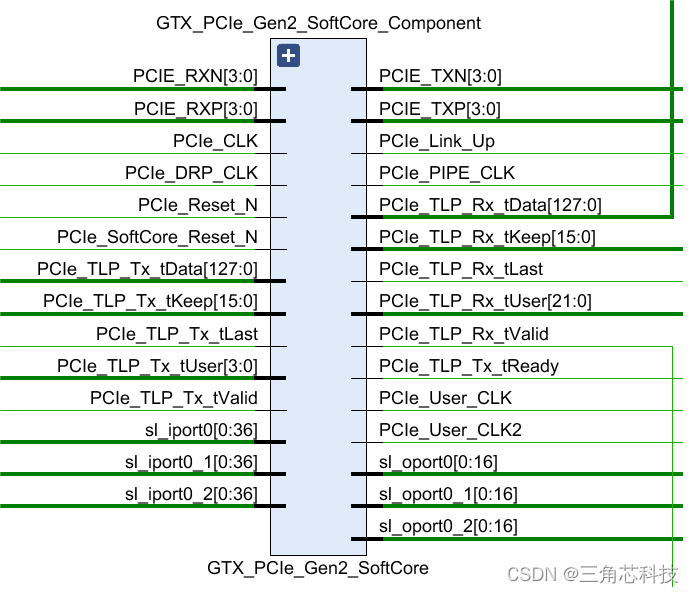

(2)包括物理层 PCIe PIPe(高速收发器搭接)、PCIe MAC(LTSSM、通道行处理、MAC收发等)、PCIe 数据链路层(DLCMSM、TLP发送接收、TLP重传、DLLP应答与流控等)、PCIe 事务层(外部控制和数据的TLP打包与解包)、PCIe上电配置(根端PCIe地址分配)等所有功能FPGA逻辑实现。

(3)第一版PCIe软核,功能已调通,与7系列PCIe硬核功能等同。

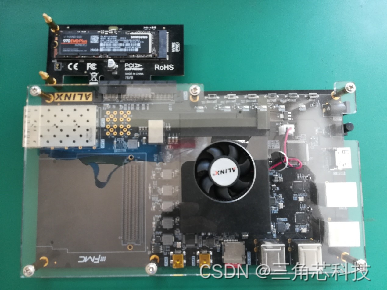

PCIe软核的开发平台如下图(AX7350开发板):

PCIe软核的对外接口如下图:

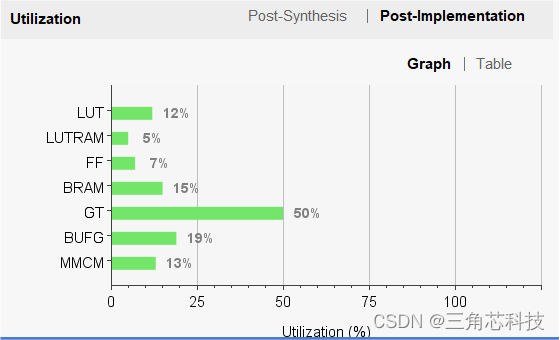

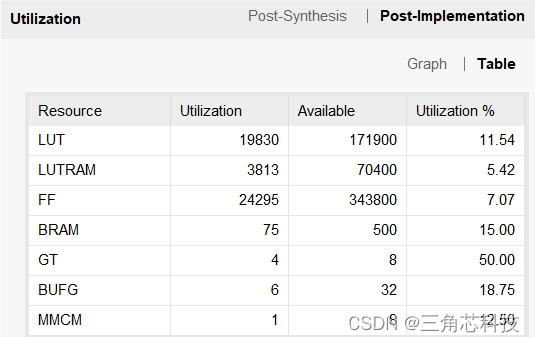

PCIe软核的资源报表如下图:

1220

1220

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?