环境射频能量收集系统:关于集成电路设计的综述

1 引言

环境射频(RF)能量是城市和郊区环境中低功耗设备(如无线传感器节点(WSNs))的一种替代能源,可支持物联网(IoT)[1, 2]。手机、平板电脑和笔记本电脑等无线通信设备的使用增加了自由空间环境中传播的无线功率,提供了可采集的新能量来源。环境射频(RF)能量是无线设备在与通信基站之间传输电磁信息时所传播信号的残留。已在各个城市和环境中开展了测量与研究,以评估利用环境射频(RF)能量作为替代能源的可行性[2–7]。通过相关调查,测得的射频能量水平密度显示出为低功耗设备采集环境射频(RF)能量的良好潜力。

这些环境中的射频能量残余为大规模部署传感器节点以用于监测应用的无线传感器网络(WSN)提供了一种可行的能源,例如在医疗保健[8–11],、智慧城市环境监测[12, 13], 、工业制造[14, 15]等领域。

生物应用,例如检测大黄蜂的授粉模式[16]。收集环境射频能量的能力为传感器节点充电提供了一种替代和新型的能源,其中电池寿命由于锂离子电池在物理尺寸、可靠性和维护方面的限制,成为大规模部署中的巨大瓶颈。

使用分立电子器件和片上系统(SoC)解决方案设计环境射频能量收集器仍然是一个挑战,原因在于射频能量的低功率密度特性与晶体管的阈值电压(Vth)(即开启晶体管所需的最小电压)之间存在不匹配;这限制了整流器的功率转换效率(PCE)。已有综述探讨了环境射频能量采集的设计范围及其挑战[17–19],但这些综述大多高度集中于分立电子器件,相较于芯片集成则关注较少。本文旨在通过系统分析,引导环境射频能量采集的研究与开发方向转向集成电路集成。

我们希望填补片上系统射频能量采集实现方面的空白,提供一篇关于环境射频能量采集的全面文献综述,重点关注集成电路集成在无线传感器网络(WSN)等应用中的应用。

我们从由整流器、阻抗匹配网络(IMN)和电源管理单元(PMU)组成的采集器出发,对各个模块进行综述,以设计适用于低功耗设备的改进型环境射频能量采集系统。第2节回顾了射频能量采集概念的总体范畴。第3、4和5节分别对整流器、IMN和PMU进行了分析与综述。第6节提供了有助于射频能量采集技术发展和性能增强的其他方面的补充信息。第7节得出结论。

2 射频能量收集器的集成电路设计

射频能量收集是指采集在自由空间介质中传播的电磁波,并将其转换为可用的电能,以驱动电子设备或传感器接口。根据射频功率的方法和密度不同,射频能量收集可明显分为近场和远场两种类型。近场射频能量收集(RFEH)通常被称为无线功率传输(WPT),通过彼此靠近放置的两个电感器或天线线圈之间的磁耦合或磁共振来采集或传输能量[20–33]。与远场相比,近场的射频频率通常较低,但功率密度较高。近场射频能量收集主要应用于生物医学领域应用[20, 22, 23, 25, 26, 29, 31] 和电池充电[30],以适应所采集射频功率密度的提高。

另一方面,远场射频能量收集是通过接收天线采集环境射频能量,所采集的射频能量可能来自专用源,也可能是传播介质中通信信号的残余能量[34]。与某些需要恒定功率的电子设备不同,无线传感器网络所需的能量非常低,无需持续供电,因此环境射频能量可作为此类设备合适的能量来源。本综述将重点关注远场射频能量收集。为简便起见,本文中的射频能量收集(RFEH)均指环境射频能量收集,因为我们仅考虑集成电路设计中报道的远场射频能量收集系统。

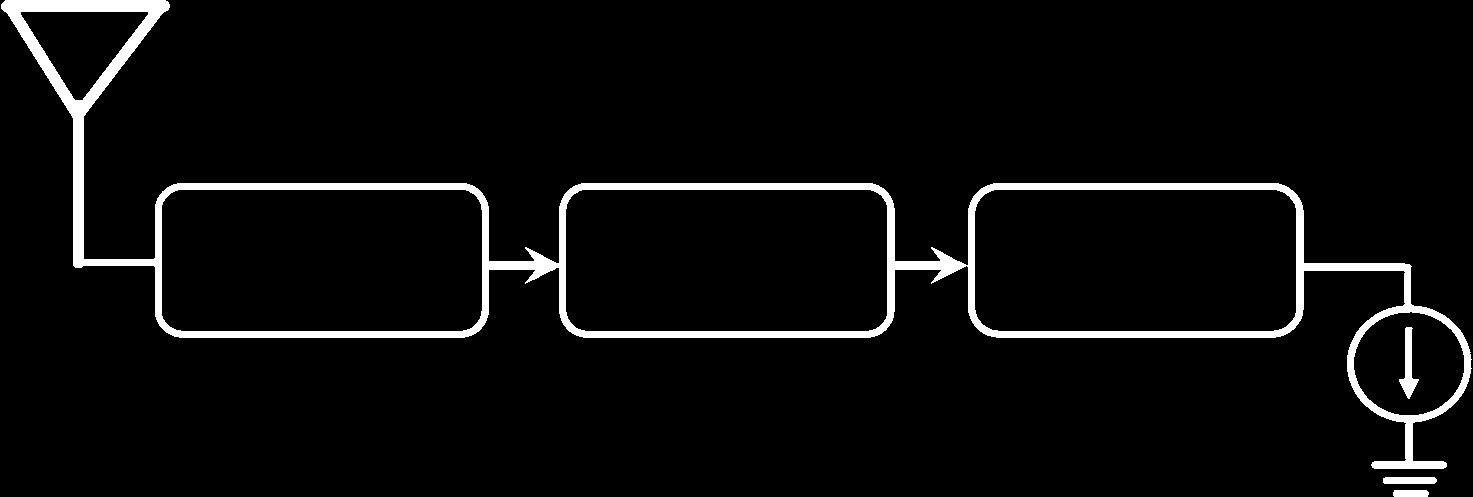

图1展示了射频能量收集系统中各模块的典型集成方式。由于本综述仅关注电路元件,对接收天线的研究将不再展开。系统的运行始于天线,天线从传播介质中捕获射频能量。天线处接收到的功率P ð RÞ可根据公式(1)[35, 36]中的弗里斯自由空间传输计算得出:

$$

P_R = \frac{P_T G_R \lambda^2}{(4\pi R)^2}

\tag{1}

$$

其中$P_T$是由天线捕获的发射射频功率信号,$G_R$是接收天线的增益,$\lambda$是无线电频率波长,即波速除以其频率,$R$是系统与发射射频源之间的距离。天线产生的交流电压可通过(2)确定:[37, 38]:

$$

V_{ANT} = \sqrt{8 \cdot R_{ANT} \cdot P_R}

\tag{2}

$$

其中$V_{ANT}$为天线处的峰值输入电压摆幅,$R_{ANT}$为天线的辐射电阻,且$P_R$为接收功率,与(1)中的类似。

当天线接收到射频功率$P_{in}$时,信号传播到IMN中,IMN实现天线与负载(即射频能量收集系统输入端的阻抗)之间的阻抗匹配,以提供最大功率传输。仍以交流形式存在的射频功率从IMN输出后,将通过整流器进行整流。电源管理单元(PMU)对直流功率进行调节或存储,我们设计该单元以确保转换后的功率适合输送至负载。

图2展示了射频能量收集系统的功率流,以及用于评估整体系统性能的表达式:

$$

\eta_{system} = \frac{P_{output,dc}}{P_{input,RF}} = \eta_{IMN} \cdot \eta_{Rect} \cdot \eta_{PMU}

\tag{3}

$$

其中,$\eta_{system}$是系统的整体效率,$\eta_{IMN}$是IMN电路的效率,$\eta_{Rect}$是整流器的效率,$\eta_{PMU}$是电源管理单元(PMU)的效率,该效率基于该单元消耗的功率量。

系统的性能主要通过其将输入射频功率转换为电能的效率以及灵敏度来评估,灵敏度是指系统启动能量收集过程所需的最低输入射频功率电平。

3 用于射频能量收集的整流器

整流器是射频能量收集系统中的主要模块,负责将采集的输入射频能量转换为可用的电能输出。目前在环境射频能量收集中广泛使用的整流器拓扑结构主要有两种:迪克森型[39–59]和交叉耦合差分驱动(CCDD)[34, 60–72] 拓扑结构。这两种拓扑结构在整流过程的实现方式上有所不同,但采用相似的性能指标进行评估,即功率转换效率(PCE)和灵敏度。

PCE用于衡量采集的功率从交流转直流的转换效率,其计算公式如下:

$$

PCE_{Rect} = \frac{P_{out,dc}}{P_{in,RF}}

\tag{4}

$$

或者,灵敏度$P_{dBm}$的表达式为:

$$

P_{dBm} = 10 \log_{10}(P_{mW})

\tag{5}

$$

灵敏度以分贝毫瓦(dBm)为单位进行评估,因为接收到的射频功率处于毫瓦或微瓦范围内。由于射频能量收集是一个新兴课题,对整流器拓扑结构的综述与射频识别(RFID)和射频传感器等应用有所重叠。

尽管所报道的电路并不完全相同应用,这些应用中的整流电路非常适合用于射频能量收集系统,因为其执行相同的功能并具有相同的性能指标。这为射频能量收集系统中整流器设计的性能比较开辟了一条途径,例如在无线传感器网络等应用中,由于输入射频功率的采集水平和采集频率相似,因此可以进行比较。

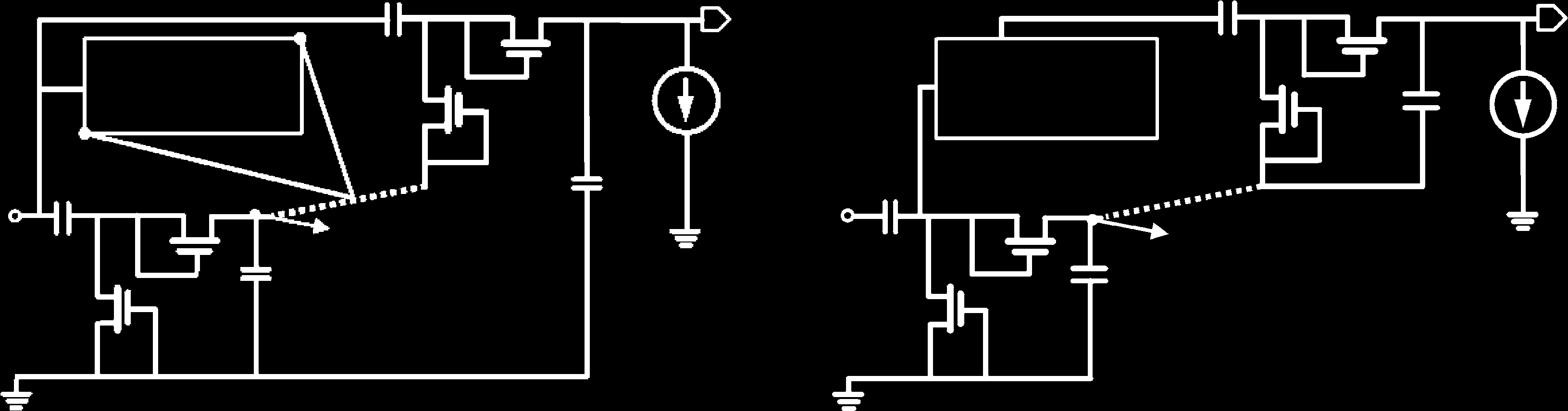

迪克森型拓扑结构由[39]以单片形式在集成电路上提出,该结构源自分立式考克饶夫‐沃尔顿电压倍增器(VM)电路。它被实现为用于晶体管‐晶体管逻辑兼容的非易失性四锁存器应用中存储器读写的高压发生器。已有少数基于相同工作原理用于射频功率整流的该拓扑结构变体被报道[40–55]。

参考图3中的电路,整流器通常采用多级结构进行堆叠或级联,其中整流器的单个级可以通过二极管连接的晶体管M1和M2以及电容器C1和C2来识别,如图3所示。在输入射频电压的负半周期期间,二极管连接的晶体管M1处于正向导通模式,而由于反向电势的存在,M2被关断。此时,电容器C1充电至$V_{RF} - V_{th1}$,其中$V_{th1}$是晶体管M1的阈值电压。在输入射频电压的正半周期期间,晶体管M2现在处于正向导通状态,而M1处于反向截止状态并被关断。此时,电容器C2被充电至由以下方程描述的输出电压:

$$

V_{out,1} = 2V_{RF} - V_{th1} - V_{th2}

\tag{6}

$$

其中$V_{out,1}$是输出电压,$V_{RF}$是峰值输入电压,$V_{th1}$和$V_{th2}$是晶体管的阈值电压M1 and M2 respectively.

该拓扑结构可以配置为多级,如图3(a) 和 (b) 中的中间级所示,以根据n级数产生最终输出电压$V_{out,n}$。

图3(a)中的集成是堆叠的,其中电路中的每一级接收到相似的输入功率水平;而图3(b)所示的配置表明,各级是级联的,其中串联电容(C1,Cn+1)还起到直流阻断的作用,为后续各级提供直流偏移。由于迪克森电荷泵适用于集成应用,可克服电容器的底板电容以及科克罗夫特‐沃尔顿配置中中间节点的寄生参数,因此被广泛应用[73]。

如(6)中所观察到的,晶体管的$V_{th}$ 对电压降有贡献,消除这种有害损耗可以减少电路中由于正向压降引起的损耗,从而提高功率转换效率。针对该拓扑结构,已提出了多种方法来改善其性能。其中一种主要技术是通过抵消或补偿晶体管的电压th来实现的[40–51, 53, 54, 56, 74]。图4表示该技术的示意图,即在典型整流器中引入一个补偿电压(VC),以在晶体管的栅极提供额外的补偿或抵消电压,从而降低电压th。

[41]中的研究报道了一种类似无源镜像的抵消器,用于抵消Vth下降的影响,以提高效率。然而,在完全抵消Vth的模式下,会出现权衡问题:抵消会增加反向漏电流,导致功率回流到源极[42, 43, 49, 51, 54, 55]。考虑到功率流的平均时间,这种情况是不希望发生的,因为它会导致流向负载的电荷减少,从而降低效率。

为了最小化电压th下降与反向漏电流之间的权衡,[40, 42–51, 53, 54]报告了多种为整流器中的晶体管提供最佳Vc的方案。[40]提出在晶体管的栅极与漏极之间加入偏置电压发生器,以施加特定的VC电平。另一种技术包括采用浮栅[42, 44],其中整流器中晶体管的栅极通过互补金属氧化物半导体(CMOS)电容器进行直流偏置,保持VC不变,以抵消其阈值电压,同时减小反向漏电流的影响。

此外,[43, 47, 49, 51]报告了补偿方案,其中Dickson拓扑中的二极管连接的晶体管通过栅极进行补偿晶体管的源极(漏极)端与多级整流器中后续晶体管的漏极(源极)端相连。或者,[43] 报道了一种采用“阶数”补偿的方案。在多级整流器中,每个晶体管之间产生的直流电压可被引出作为$VC$。当某个晶体管引出下一个级联级的直流输出时,称为一阶补偿。类似地,若引出后续第$n$级的直流输出,则根据所引出的后续级数$n$的数量,称为$n$阶补偿,其中$VC$ 被引出。

一种更复杂的调节晶体管VC的方案是通过改变整流器中补偿顺序的能力,该方案在[47]中提出。哈米德和穆兹[49]进一步改进了这种补偿方案,采用了一种混合补偿方法,通过前向补偿减少Vth的不利影响,并通过增加Vth实现反向补偿,以在需要时防止反向漏电流。

文献[51]提出了一种自适应混合补偿方法,在栅极处串联二极管连接的晶体管,以最少的电路提供补偿电压。其他补偿方法包括使用附加电路独立生成$V_C$[53, 54],但这会增加电路的复杂性。

提高该整流器性能的另一种方法包括:对晶体管进行体偏置以降低Vth[52],采用栅极升压技术以提升栅极处的输入射频电压[48], ,调整整流器拓扑结构中的交叉耦合方案以减少反向漏电流[45],或在电路中利用电容集成[46, 50, 55]。电容集成可用于通过存储能量并向栅极释放电压来设定栅极电位,如文献[46],所提出的;或将电容器作为泵浦储能元件以抵消Vth[50]的影响;或在输出端放置电容器,以在正半周期减小负载电容,从而降低漏电流[55]。

另一种用于提升性能的非电路技术是采用肖特基二极管或集成电路中的其他工艺实现[37, 75, 76] ,该方法在低电压降和低反向漏电流方面表现出良好的性能,但以增加制造成本为代价。

使其成为在集成电路集成中不具吸引力的实用解决方案[46, 图485, 所49]示。的CCDD拓扑结构也表现出类似的改善趋势。该拓扑结构源自二极管桥式整流器,最初由[60] 在集成电路实现中提出,作为四单元整流器,并由[61]定义为CCDD。该拓扑结构由两组串联连接的单个 NMOS晶体管和单个PMOS晶体管组成。这两组晶体管以交叉耦合结构对称连接,其中一组串联电路的栅极连接到另一组NMOS晶体管和PMOS晶体管之间的输入节点,如图5所示。

在输入信号$V_{RF}$的正半周期期间,晶体管MP2和 MN1因栅极分别被正电压和负电压驱动而强制关断。与此同时,晶体管MP1和MN2导通,形成一个完整的电路回路连接到负载,其作用类似于二极管桥式整流器。同样,在输入信号$V_{RF}$的负半周期期间,晶体管 MP2和MN1导通,而晶体管MP1和MN2被强制关断。该拓扑结构中的其他元件包括耦合电容CC,它在输入端提供交流耦合,并作为直流阻断以防止直流电荷回流至源极;电容器CL为滤波电容,用于平滑输出端的纹波电压;RL为输出负载。

该拓扑结构能够实现高达80%的峰值PCE,但在较高输入功率水平[61]下会受到反向漏电流的影响。与迪克森型拓扑结构类似,当整流器以多级配置连接时,输出电压$V_{out}$可能高于输入射频电压。当发生这种情况时,在输入射频电压的上升和下降时段,电荷会从 $V_{OUT}$的高电位流向$V_{RF}$的低电位,从而产生反向漏电流。

最近的研究报道了减少反向电流影响的技术,例如在[64, 69]中采用反馈网络来检测$V_{out}$,以控制 PMOS晶体管的栅极偏置。一些更简单的方法结合了电阻元件,例如在栅极和输出[70–72]之间使用无源电阻或高Vth晶体管。当$V_{out}$大于$V_{RF}$时,会产生较大的电位差,从而减轻反向电流的不利影响。在文献[34],中,作者利用漏电流的优势,采用一种偏置方案来增强射频能量收集整流器,并将其作为过压保护方案。另一项工作在[65]中采用了在 CMOS中实现的互补拓扑结构,以及利用CMOS工艺中可用的蓝宝石上硅(SOS)技术构建的二极管桥式整流器,以减少SOS中二极管桥的回流电流,并通过 CMOS中的CCDD提高正向电流。还提出了其他增强方法,例如在栅极提供直流偏置,采用类似产生Vth的自适应阈值方案来减小迪克森拓扑中Vc的影响[62]。

另一项工作在[66]中开发了一种压电与射频能量收集器的混合能量收集器,其中射频能量收集器利用压电部分采集的能量产生直流偏移。表1总结了近期报道的先进射频整流器的比较。

在射频能量收集系统中,整流器拓扑结构的选择取决于两种主要拓扑结构之间的多种权衡。可以发现,第一个权衡在于晶体管数量,其中交叉耦合双二极管拓扑所需的晶体管数量是迪克森拓扑的两倍,这可能会影响集成电路制造中的尺寸限制。此外,自偏置的CCDD拓扑能够在较少的级数 2[71, 72], 3[34, 61, 65]或 5[38]下实现输出工作电压,而自补偿迪克森拓扑通常需要更多的级数,范围从 7[48], 12[47], 17[42], 20[44], 24[49],甚至高达 50[57, 59]才能达到相应的输出,这可能是迪克森拓扑效率较低的原因之一。由于交叉耦合双二极管拓扑需要更少的级数即可达到相同的输出电压,因此其晶体管总数可能更少,从而占用更小的面积。然而, CCDD拓扑需要差分天线或PCB平衡‐不平衡转换器来实现单端到差分转换[51]。

另一个需要注意的考虑是,这两种拓扑结构中整流器的阻抗会随输入射频功率电平[37, 38, 45, 60, 77]而变化。此外,整流器的阻抗还随着级数和晶体管宽度[43, 49, 61]而变化。这些整流器的特性将在下一节关于射频能量收集系统的IMN电路中进行探讨,因为它与阻抗匹配网络电路的设计考虑密切相关。

在两种拓扑结构中都存在的另一个折衷是,当输出负载变化时,PCE曲线会发生偏移。增加输出负载需要更多功率,从而降低峰值PCE和灵敏度。与其仅仅关注实现峰值PCE性能(已在许多基于CCDD拓扑的报道工作中实现),一个值得关注的研究方向是拓宽高PCE范围。

4 射频能量收集系统的阻抗匹配网络(IMN)

射频能量收集系统中的下一个模块是集成在天线与整流器之间的IMN电路。IMN电路通过负载阻抗与源阻抗的共轭匹配,确保天线接收到的功率能够最大效率地传输到负载。良好的匹配可以降低采集的输入射频信号的反射,IMN的性能由反射系数$S_{11}\text{(dB)}$衡量,其表达式为[35]:

$$

S_{11} \text{(dB)} = \Gamma = \left| \frac{Z_{\text{rect}} - Z^

{\text{ant}}}{Z

{\text{rect}} + Z^

_{\text{ant}}} \right|

\tag{7}

$$

其中,$\Gamma$是反射系数,$Z_{\text{rect}}$是整流器的阻抗,$Z^* {\text{ant}}$是天线的阻抗。由于整流器是非线性电路,$Z {\text{rect}}$可近似为一个由电阻和电容器组成的线性负载在迪克森拓扑结构中并联[73, 81]。对于交叉耦合双二极管拓扑,使用戴维南等效电路,通过包含辐射电阻的函数来近似表示$Z_{\text{rect}}$[38, 82],其中包含一个由电压源产生感应电压的串联电容和电阻´。

参考(7),当天线与整流器的阻抗匹配时,反射降至零,从而最小化反射信号,并最大化从天线到整流器的信号传输。反射系数方程的另一种形式是功率反射系数,$|\Gamma|^2$用于计算被反射的功率大小,表达式如下:

$$

|\Gamma|^2 = \left| \frac{Z_{\text{rect}} - Z^

{\text{ant}}}{Z

{\text{rect}} + Z^

_{\text{ant}}} \right|^2

\tag{8}

$$

尽管(8)与(7)相当,但(8)中的主导项被平方以表示反射功率的大小。

IMN电路通过在特定频率下电荷的存储与释放,使源极和负载阻抗谐振来实现阻抗匹配。类似地,IMN电路也可应用于射频接收机中的低噪声放大器等其他场景[77]。针对射频能量收集系统已实现并研究的最基本的IMN网络是L型匹配[43, 73, 77, 83, 84]。表2展示了一些L型匹配的变体形式及其在射频能量收集系统中使用的相应数学关系。术语‘Q’为品质因数,表示存储能量与耗散功率之比,是频率的函数,$R_{in}$为源(天线)辐射电阻,而$R_L$为负载阻抗,在射频能量收集系统中即为整流器和电源管理单元的阻抗。$\omega_0$为输入射频功率的频率,而$C$和$L$分别为匹配电容和电感的取值。

根据所选L型匹配的配置,在测试集成电路芯片的条件下,考虑负载阻抗的虚部和焊盘寄生电容,以确定IMN电路元件的尺寸,从而实现最佳匹配条件。为射频能量收集系统设计IMN电路的主要挑战之一是整流器的阻抗会随输入射频功率电平的变化而变化。

由于射频整流器在不同输入功率水平下存在阻抗波动,[77]提出了一种利用概率密度分布来确定元件最佳值的方法,以在设计射频能量收集系统时,在工作输入射频功率范围内实现阻抗匹配网络电路的最高性能。差分L型匹配也已应用于射频能量收集系统,通常用于差分整流器拓扑结构,例如具有两个对称结构的CCDD整流器每个输入端的L型匹配电路。

此外,[73]报道了一种复杂的L型匹配技术,该技术通过一系列二进制控制电容器实现RFEH系统的可重构L型匹配,以改变电容器的值,从而在输入射频功率电平变化时确保最低的反射,因为整流器的阻抗会发生变化,同时还提供了调谐IMN电路以在多种输入射频频率下工作的能力。该工作在一个射频能量收集系统中实现,其中电源管理单元(PMU)(本工作的部分内容将在后面讨论)控制[87]中提出的二进制系统。

该研究还探讨了片上与片外IMN的差异,结论指出,在无源器件的灵敏度和品质因数方面,片外IMN性能更优[73]。尽管片外IMN表现出更好的性能,但片上IMN能够实现系统的完全集成,并且在物理尺寸和外形因数方面要小得多。

射频能量收集系统中报道的另一种匹配方式是变压器匹配[81, 88, 89]。图6展示了射频能量收集系统中使用的变压器匹配的简单电路表示。变压器对于低阻抗天线,匹配效果更佳,因为低阻抗天线自然产生较低的输出电压,需通过IMN电路的电压增益能力来提升[89]。在[81],中,该研究利用升压变压器实现功率匹配,并作为采集的射频功率的电压提升器。

其他为双频射频能量收集提出的片上IMN设计[90, 91]扩展了射频能量收集系统设计在多个频率上的应用范围,使得射频能量收集系统能够采集多个输入射频频率。文献[90]开发了一种射频能量收集系统,该系统将两个串联电感连接到一个输入源,同时从两个频率采集能量并输送至两个不同的整流电路;而文献[91]在集成无源器件(IPD)技术上为两个频率分别设计了带通滤波器(BPF)和带阻滤波器(BSF),并将整流器实现在标准CMOS平台上,以实现更高的阻抗匹配网络电路性能。

一些研究尝试通过在系统开发中采用天线协同设计策略来消除射频能量收集系统中的阻抗匹配网络电路[41, 82]。该协同设计策略旨在同时开发天线和电路,以实现匹配阻抗,而无需通过阻抗匹配网络电路进行中间匹配,若将集成天线设计纳入开发范围,则可进一步探索该方法。这可以提高整体效率,因为消除了匹配网络中的损耗。表3总结了针对射频能量收集系统的阻抗匹配网络研究。

根据对阻抗匹配网络电路的综述,L型匹配与变压器匹配在集成面积限制方面表现出明显的权衡关系。相比变压器匹配,L型匹配的设计方法更为简单。由于电感的品质因数限制了电压提升能力并影响灵敏度,片上L型匹配电路的性能低于片外实现。而另一方面,变压器匹配一直被报道为一种片上电路。因此,这种权衡可归结为在阻抗匹配网络电路的尺寸限制下,对片上实现最高性能的追求。由于片上设计面积有限,变压器匹配在射频能量收集系统中的片上阻抗匹配网络集成更具吸引力。

在电压增益方面的另一个考虑是希望IMN充当增益提升元件。通过变压器匹配,增益可以根据情况配置初级和次级线圈之间的匝数比。另一方面,L型匹配高度依赖于电感的Q因子,其在片上集成方面的局限性显而易见。输出电压和负载电流也会影响灵敏度,因此在设计IMN时必须考虑输出负载的参数,以实现最佳匹配和性能。

5 射频能量收集系统的电源管理单元(PMU)

最后一个模块是PMU,通常集成在射频能量收集系统链中整流器之后。PMU用于实现多种电源管理功能。其中一个主要原因是管理由于环境条件变化以及天线输入端接收到的低功率水平所引起的接收功率波动。无论采用何种方法实现PMU,其最终目的都是在系统的目的是提升整体射频能量收集系统的性能。根据管理系统的电源方法不同,电源管理单元中包含各种电路。

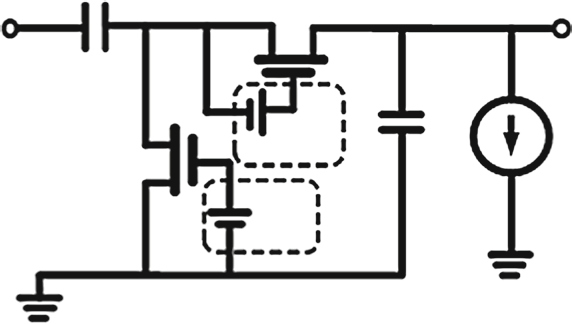

首先,当预期输入射频功率较低时,可以将整流器尺寸设计为尽可能产生最高的电压,从而在输出端实现高电压生成[92]。这会导致问题:更多的级数会增加$V_{th}$下降,从而降低效率。此外,如果输入射频功率电平剧烈波动,仅使用一个整流电路将导致射频能量收集系统的直流输出电压无界。整流后的直流输出电压会随着输入射频电平的波动而变化,这种波动受环境条件或与发射天线距离变化的影响。最基本的电源管理单元集成方式之一是加入电压调节器[75]。电压调节器仅在整流输出电压在其期望的直流输出值附近波动时才适用。在输入剧烈波动的情况下,作为电源管理单元的电压调节器在调节输出端较大的直流电压变化时,其效率会受到影响。在[85],所报道的工作中,提出了一种射频能量收集系统解决方案,该方案采用单级整流器与基于电感的DC‐DC升压转换器配对,并结合自适应控制,根据输入射频功率电平为转换器提供自适应时钟信号作为电源管理单元。单级整流器可避免晶体管出现过多的$V_{th}$下降,不像更多级的整流器级数那样。该系统通过比较器检测整流器输出端的功率水平,用于锁存脉冲发生器,从而为升压转换器提供时钟信号,以向负载提供电荷。时钟频率根据检测到的功率水平进行调整,以实现升压转换器的最佳工作状态。

另一项工作在[38]中实现了一种可重构整流器,主要针对RFEH系统由于输入功率水平波动而导致的启动问题,以提高其灵敏度。所提出的PMU允许使用多种数字模块,包括时钟发生器、负载,带有锁存比较器和二进制模块的存储和整流控制器。电压基准发生器是唯一使用的模拟模块。电源管理单元根据设计将整流级的级数配置为最高,以在相应的低输入功率水平下实现最高电压,同时提高灵敏度。或者,当输入功率水平达到能够整流至所需输出电压的水平时,电源管理单元将配置为最少的级数。

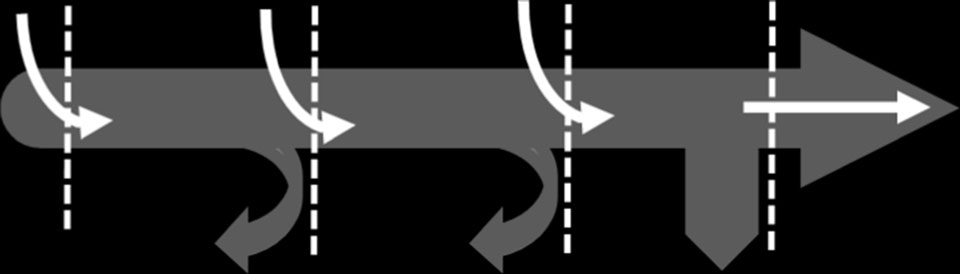

与其重新配置级数,一些已报道的工作通过根据输入功率水平将整流级以串联或并联方式重新配置其排列结构。将整流器以串联或并联方式排列会改变整流器的阻抗,从而改善阻抗匹配条件,提高射频能量收集系统的灵敏度[45]。另一个原因是由于功率转换效率曲线,不同的整流器配置可根据输入功率水平使该曲线发生偏移[93]。图7展示了单级整流器在不同输入射频功率下的功率转换效率。将另一整流级以串联方式集成可使功率转换效率曲线向右移动,使得峰值PCE位于较高功率处。

同样,将整流级并联配置会使峰值PCE曲线在较低输入射频功率下向左移动,这提出了开发一种能够重新配置多级整流器结构的电源管理单元(PMU)的需求,以提升在不同输入射频功率水平下的功率转换效率。

此外,工艺中的晶体管在不同的输入功率水平下可能表现出不同的性能,文献[38]提出了一种双路径电源管理单元解决方案,通过使用互补金属氧化物半导体工艺中的标准阈值、低阈值和高阈值晶体管来控制功率在两种整流器之间的分配。根据检测到的输入功率水平,电源管理单元接通或断开射频能量收集系统中的特定路径,使功率能够通过在特定输入功率水平下效率最高的路径传输。

通常,射频能量收集系统受限于接收到的功率,在负载端功率不足。因此,设计了一种新型的电源管理单元来管理储能系统,以采集并存储能量,并在积累足够电荷后向负载放电[87, 94, 95]。电平检测器用于检测射频能量收集系统中的不同功率水平,以对储能电容进行充电,并在适当时将能量释放给负载。此外,在[87, 94],的研究中,当输入功率足够高时,可禁用充放电过程,使功率直接流向负载。

根据功能,射频能量收集系统的电源管理单元可归纳为两种拓扑结构。图8总结了射频能量收集系统中使用的两种基本电源管理单元方法。图8(a)展示了电源管理单元系统,其通过因输入功率水平波动而控制整流器配置或升压转换器的脉冲来调节各个元件。图8(b)中的电源管理单元则由于输入功率较低而控制储能元件。无论电源管理单元的功能如何,一些电路是共通的,例如电压传感器、参考发生器和控制器,其功率均来自采集的能量。表4比较了当前最先进的射频能量收集系统实现方案。选择系统设计的拓扑结构完全取决于系统的应用。诸如射频识别和传感器等应用需要持续供电,而无线传感器网络则需要短时高功率,因此需要能量存储。

电源管理单元(PMU)的拓扑结构可根据其所要供电的负载电路进行选择。如前文整流器部分所述,增加负载会降低功率转换效率(PCE),但这仅适用于需要恒定功率的应用。如果不需要恒定功率,可以设计一个充电电路,在将能量释放到负载之前将其累积至所需量,从而在射频能量收集系统设计中使负载成为最不需关注的因素。与前两个考虑因素相关的是待采集的输入射频功率电平范围。如果需要实现低功率采集,则PMU必须能够在输入功率较低时累积能量,并在输入电平较高时允许将功率输送至负载。PMU的复杂性将根据具体应用和功能而变化。此外,当PMU的供电来自采集的能量时,应设计为低功耗消耗,以提高整体射频能量收集系统的效率。

6 射频能量收集集成电路设计应用的其他方面

还有一些关于射频能量收集整体的研究计划,涉及集成射频能量收集系统的设计。其中一个新兴领域是在CMOS技术中实现毫米波(mm‐wave)频率的射频收发器[48, 52, 67, 96]。该领域报道的射频能量收集系统性能仍然有限,最高报道的峰值PCE仅为20%,灵敏度为6dBm[67]。其次,还有研究计划致力于同时采集多种类型的射频信号[97, 98]。大多数射频能量收集所研究的系统模块均假设输入射频信号为纯正弦波形。文献[98]表明,在实际应用中,射频能量收集系统的性能不仅受限于输入射频功率电平和频率,还与所采集波形的类型和形状有关。最后,新兴研究正在通过分立式和集成式电路设计探索多频带射频能量收集,以提高射频能量收集系统的供电功率密度[2, 82, 91, 99]。

当前的多频带射频能量收集研究主要集中于整流天线设计,即将整流器与天线在单一设计中结合,使用分立元件实现[100–104]。未来关于多频带射频采集也有望通过集成电路实现来减小多频带射频能量采集系统的物理尺寸。

7 结论

本文综述了芯片级射频能量收集系统(RFEH)及其相关系统模块的研究工作,探讨了现有差距,并聚焦于集成电路实现中的RFEH设计。每个系统模块均从其范围、方向、性能、局限性以及在实际应用中的电路集成潜力等方面进行了分析,同时指出了进一步研究和改进的方向。此外,还专门设立章节总结了射频能量收集系统的设计挑战与研究趋势,概述了设计中的主要挑战以及近年来报道的射频能量收集领域的研究动态,这些都值得重点关注。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?