一种基于有限范围二分查找的基带全数字时钟与数据恢复电路

摘要

本文提出了一种基于全数字锁相环(ADPLL)的时钟数据恢复电路(CDR),用于基带电路系统。为了适应不同的数据速率,设计了可编程的数字控制时钟相位发生器(DCPG),以生成具有不同相位分辨率的恢复时钟。为了在任意相位数下执行二分查找,在相频控制有限状态机(PFCFSM)中加入了有限范围的二分查找流程。

该提出的CDR在0.18μm CMOS工艺中进行了验证,占用了200μm×225μm的核心面积。在1V的供电电压、200MHz的参考时钟和500ppm的数据频率偏移条件下,芯片结果显示数据速率范围为1Mbps至5.5Mbps,总功耗为0.22mW。在5.5Mbps下,恢复时钟和数据的时序抖动分别为0.025UI和0.0475UI。

I. 提出的时钟数据恢复电路架构

对于第五代移动通信系统或第六代移动通信系统,基带电路系统可根据基带信号质量、通信信道条件和应用需求支持动态数据速率调整。由于具有更高的工艺可扩展性和性能灵活性,全数字时钟数据恢复电路易于集成到基带电路系统中。

图1显示了提出的全数字CDR的系统架构。亚历山大相位检测器比较输入数据(DI)和恢复时钟(ckO)的相位,然后输出相位超前或滞后。作为环路滤波器,置信计数器收集相位关系,通过累加减少相位比较结果的噪声,并将相位偏移控制(Leado/Lago)提交给PFCFSM。

PFCFSM存储频率和相位控制码(L[0:5], P[0:5]),以使DCPG相应地生成恢复时钟。

图2展示了DCPG的示意图,该DCPG由一个可编程计数器和等值检测器组成。该可编程计数器使用计数器来累加参考时钟周期。不同的计数值被视为不同的相位位置。当时钟计数值C[0:5]达到决定恢复时钟总周期的上限时,等值检测器会发送重置脉冲,使计数器重新开始计数过程。

为了产生不同的时钟相位,将计数值与代表上升沿和下降沿相位数的互补相位控制P[0:5]进行比较,从而向后续的推挽反相器发送周期性脉冲(Ueq/Deq)。

为了加快数据恢复速度,采用了二分查找方法在初始频率和相位跟踪过程。与全范围(例如7位,0~127)搜索相比,相位数随数据速率变化并受到限制(例如0~80)。传统全范围二进制搜索如图3(a)所示,会导致有限状态机输出禁止的相位控制(P[0:N> L[0:N]]),从而使数字控制时钟相位生成器无法输出时钟。

为解决该问题,图3(b)展示了一种提出的有限范围二分查找。每次根据二叉树确定位值时,已确定的位和预设为一的当前位(P[n:N])将与上限(L[n:N])进行比较。当待确定的当前位满足 P[n:N]<L[n:N] 时,该位将被强制置零。

II. 测试芯片验证

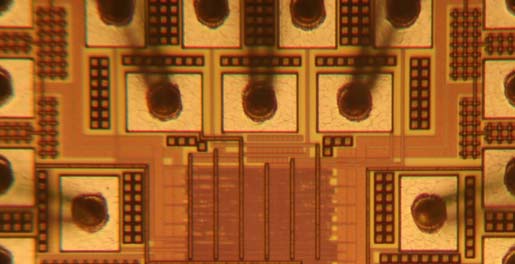

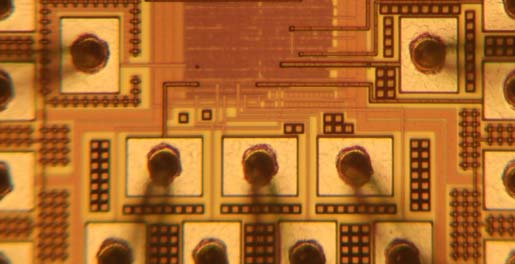

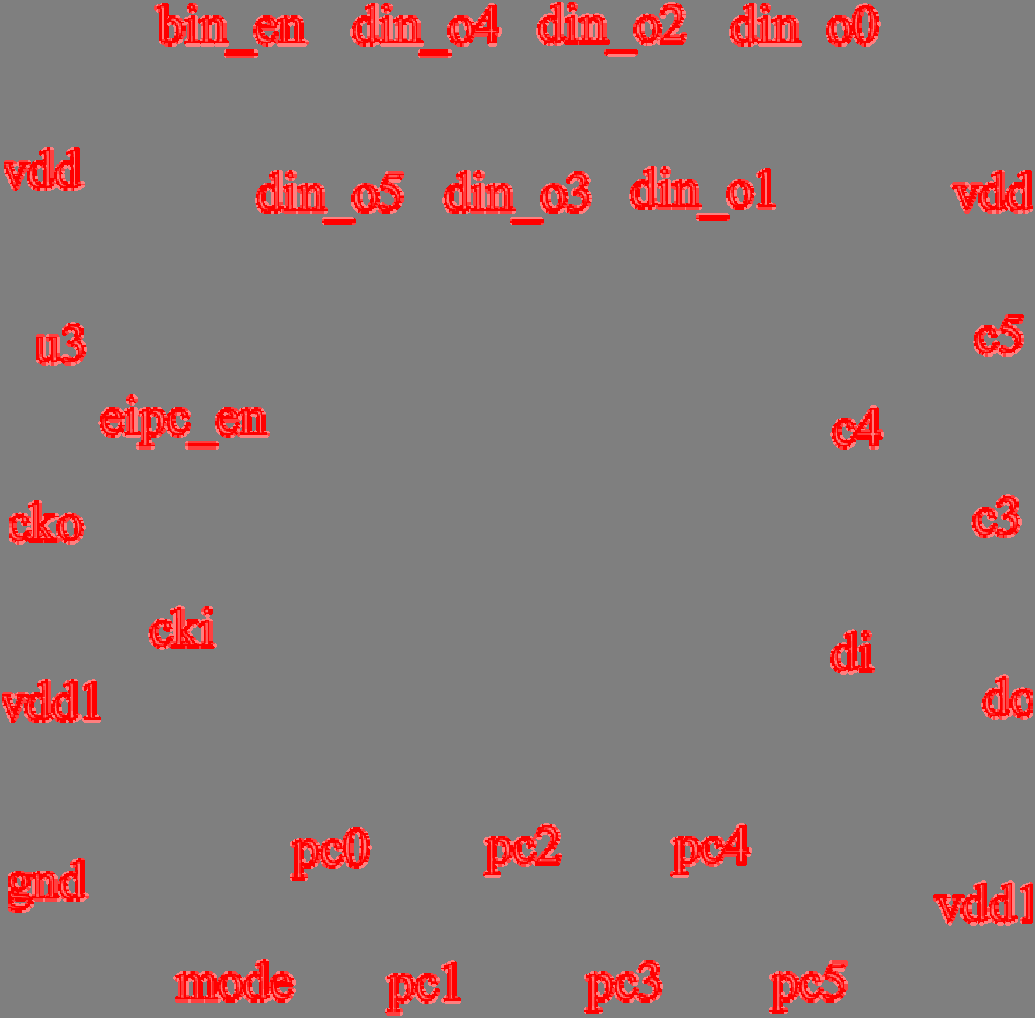

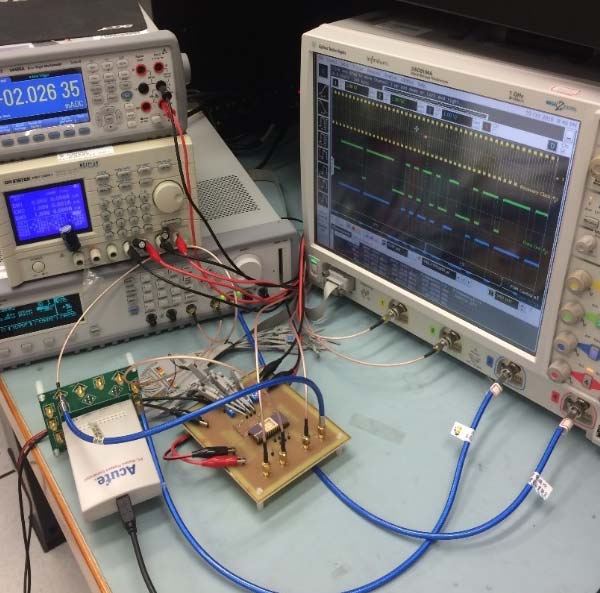

为验证提出的架构,图5展示了在台积电0.18微米工艺下实现的CDR测试芯片及其测试设置。核心尺寸为220μm×220μm。Acute PKPG2116+和安捷伦81130A生成高频系统时钟以及带有频率偏移的低速率输入随机数据,安捷伦DSO9104A测量恢复数据和PFCFSM的控制码。

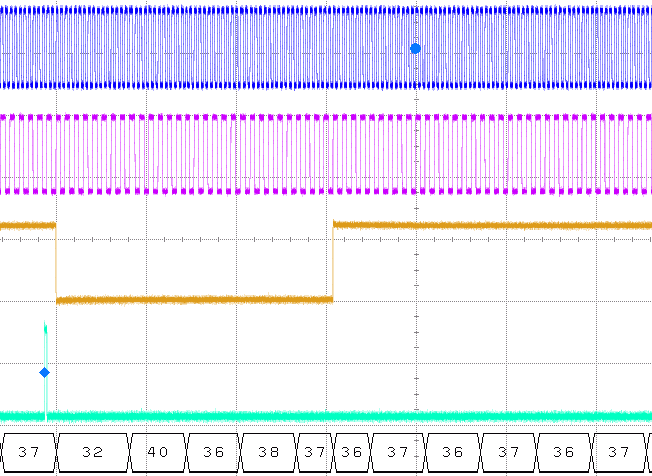

在200兆赫时钟和5兆比特每秒数据且无频率偏移的情况下,图6显示了测得的二分搜索过程。其中目标码为37,控制码范围限制为40。控制码序列不是32、48、40(传统方法),而是32、32、40(提出的方法),从而避免了相位控制超出范围。

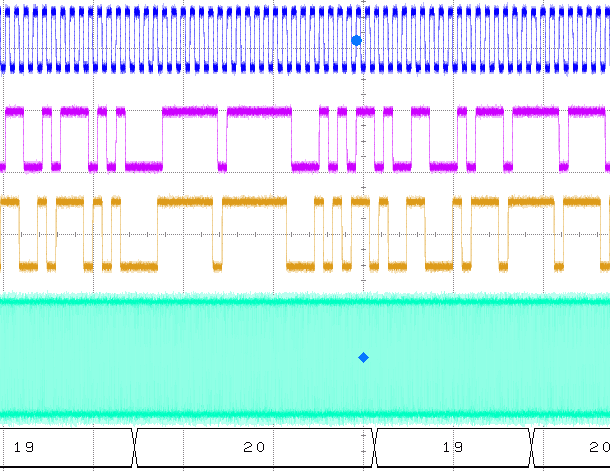

图7展示了在零、+500ppm和‐500ppm频率偏移下恢复数据和恢复时钟的眼图及短期序列。恢复数据的时序抖动分别为0.05UI、0.075UI和0.05UI。

表I 先前基带CDR技术比较

| 参考文献 | [1] | [2] | [3] | [4] | [5] | 本工作 |

|---|---|---|---|---|---|---|

| 工艺(微米) | 0.18 | 0.25 | 0.18 | 0.18 | 0.13 | 0.18 |

| 最大数据速率(Mbps) | 10 | 2 | 10 | 2 | 0.2 | 5 |

| 电源电压(V) | 1 | 1 | 1 | 0.5 | 0.7 | 1 |

| 功率(mW) | 4.6 | 0.2 | 2.4 | 4.535 | 0.39 | 0.22 |

| 面积 (mm²) | 2.3 | 0.85 | 2.5x5 | 0.121 | 2 | 0.37 |

表I列出了本工作和已报道的低速率基带CDR的规格。提出的设计具有低电路面积、低功耗和宽数据速率范围的特点。

3万+

3万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?