基于忆阻器的多层神经网络电路设计

摘要

忆阻器是用于非易失性存储器、逻辑电路和神经形态计算应用中的有前景的元件。本文提出了一种用于基于忆阻器的多层神经网络的新颖电路,该电路能够利用单个忆阻器阵列实现神经突触联的正权重和负权重。此外,在学习过程中使用基于忆阻器的开关来更新基于忆阻器的突触联的权重。同时,采用一种适用于所提出的基于忆阻器的多层神经网络的自适应反向传播算法来训练神经网络,并执行异或函数和字符识别。本文的另一亮点是,与其它多层神经网络相比,所提出的基于忆阻器的多层神经网络表现出更高的识别率和更少的周期。

索引词

忆阻器,突触权重,交叉阵列,多层神经网络,异或函数,字符识别。

I. 引言

ARTIFICIAL 神经网络已被用于解决模式识别领域的许多问题,展现出实现高速计算的潜力。实现高速计算的一种可能器件是忆阻器,其发现极大地拓展了混合CMOS架构在非常规逻辑[1](如阈值逻辑[2]和神经形态计算[3])中的应用范围。忆阻器由蔡于 1971[4]年从理论上提出,随后威廉姆斯团队于 2008[5]年在惠普实验室展示了一种电阻可变器件作为忆阻器。作为一种新型纳米级器件,忆阻器具备非易失性、高密度、低功耗和良好的可扩展性[6]等多种优势特性。忆阻器尤其适用于人工神经网络[7],[8]中,将突触权重实现为具有记忆功能的可重构电阻的固有特性,使得忆阻器非常适合用于突触权重优化。

神经元电路最初是在互补金属氧化物半导体[9],[10]中开发的。随后,开发了混合CMOS‐忆阻器突触电路[11]–[13]。然而,晶体管的面积和功耗远大于忆阻器。文献[14]–[16],提出了一种基于忆阻器桥接突触的神经网络与学习方法,该方法实现了由反向传播(BP)算法训练的多层神经网络(MNN),并且突触权重的更新由主机计算机完成。然而,主要的计算瓶颈在于学习过程本身,无法通过大规模基于忆阻器的交叉阵列在硬件中完全实现。

许多先前基于忆阻器的学习规则都集中在脉冲时序依赖可塑性(STDP)[17]上。例如,在[18],中提出了一种采用两个PCMO忆阻器(双忆阻器)作为突触联的神经形态字符识别系统,并在[19]中为CMOS神经元提出了用于视觉模式识别的学习规则。丝状开关二进制双忆阻器突触联被用于语音识别[20]。然而,基于STDP的学习对于一般输入的收敛性无法得到保证[21]。

此后,针对基于忆阻器的神经形态架构提出了新的方法。例如,[22],中提出了脑状态盒(BSB)神经网络,其也使用双忆阻器交叉阵列分别表示正极性和负极性连接矩阵。[23]和[24],中提出了具有在线梯度下降训练的基于忆阻器的多层神经网络,每个突触联使用单个忆阻器和两个CMOS晶体管(2T1M)。[25]中提出了一种双忆阻器硬件神经形态网络的训练方法。为了减小电路尺寸,期望使用更少的忆阻器和晶体管。因此,[26],中提出了一种基于忆阻器的交叉阵列架构,其中正极性和负极性连接矩阵均由单一交叉阵列和一个简单的恒定项电路实现,从而减小了物理尺寸和功耗。然而,[26]中的基于忆阻器的神经网络仅限于单层神经网络(SNN)。在大多数基于忆阻器的神经网络中,片上学习方法仍然是一个挑战。

在[27]–[29]中研究了具有基于忆阻器的突触的神经形态处理器,以实现数字模式识别。在[30]和[31],中提出了双忆阻器交叉阵列神经形态处理器的训练算法,该算法可以用于MNN中;然而,每个突触需要两个忆阻器。一种用于超高密度神经交叉数据栏的片上监督学习规则在[32]中被描述,该规则使用忆阻器实现突触和神经元,以执行异或和与逻辑运算。在100万个交叉点的数据栏上实现BP算法仍然是一个问题。

本文的主要贡献是:

1) 基于忆阻器的与门(MRL门)[33]被用作基于忆阻器的开关(MS)[2],以更新突触交叉阵列电路。在仿真中采用了基于实验数据的突触电路的忆阻性模型。还提供了用于确定权重更新过程相关时间的公式。此外,添加了一个放大器以生成误差,从而为片上更新突触权重创造了条件。

2) 将[26]中的基于忆阻器的SNN扩展到MNN,即使在忆阻值变化的情况下也提供了增强的鲁棒性。所提出的基于忆阻器的突触交叉阵列电路与[11],[12],[14]‐[16],[18]‐[20],[22],[23],[25],[30],和[31]中描述的突触电路相比,使用了更少的忆阻器且无需晶体管。

3) 开发了一种适用于所提出基于忆阻器的MNN的自适应BP算法,用于训练神经网络并执行异或函数和字符识别。此外,权重调整过程以及所提出的MNNs表现出更高的识别率并且需要更少的周期。

本文的其余部分组织如下。第二节讨论了忆阻器和 MS。第三节介绍了提出的基于忆阻器的SNN和扩展的 MNN。第四节描述了基于所提出的自适应BP算法的 MNN的操作。第五节讨论了交叉阵列架构的鲁棒性。第六节提供了仿真结果,以证明提出的司法电阻基神经网络的优越性能。第七节对全文进行了总结。

II. 忆阻器与MS

本节介绍了关于忆阻器和基于忆阻器的开关(MS)的基本背景。在第二节.A中,对忆阻器进行了理论表征,并讨论了不同的忆阻器模型。在第二节.B中,提出了将 MS应用于基于忆阻器的神经网络。

A. 忆阻器

一个电荷控制的忆阻值[4]可以被描述为

$$

M(q)= \frac{d\phi}{dq},

$$

其中$M(q)$为忆阻值(单位为 $\Omega$),$\phi$为磁通量,$q$为电荷。电流控制的HP忆阻器为[5],[34]

$$

v(t)= R(t)i(t)

$$

$$

R(t)= R_{ON} \frac{w(t)}{D} + R_{OFF}(1 - \frac{w(t)}{D})

$$

其中,$w(t)$是掺杂区域的宽度(初始宽度$w(0)$= $w_0 \in R$),$R(t)$是忆阻值($R(t)$= $M(q)$),$D$是$TiO_2$, $R_{ON}$表示忆阻器完全掺杂时($w(t)$= $D$)的内部低忆阻值,$R_{OFF}$表示忆阻器完全未掺杂时($w(t)$= 0)的内部高忆阻值,$i(t)$和$v(t)$分别是忆阻器的电流和电压[5]。

为了考虑忆阻器的特性,[35]–[37]中比较了不同的忆阻器模型。此外,[38]–[40]中介绍了不同的基于忆阻器的SPICE模型和电路。因此提出了一种新模型,该模型符合近期忆阻器件的突触行为[41]。所提出的内存性模型中状态变量的导数

$$

\frac{dw(t)}{dt}=

\begin{cases}

\frac{\mu_v}{R_{ON}} \frac{D}{i_{off}} i(t) - i_0 f(w(t)), & v(t)> V_T^+> 0 \

0, & V_T^- \leq v(t) \leq V_T^+\

\frac{\mu_v}{R_{ON}} \frac{D}{i_{on}} i(t) f(w(t)), & v(t)< V_T^-< 0,

\end{cases}

$$

其中$i_0$, $i_{off}$和$i_{on}$是常数,$\mu_v$表示平均离子迁移率,$V_T^+$和$V_T^-$分别是正负阈值电压。电导变化与脉冲次数(时间)[42]之间存在关系。还可以通过窗口函数引入非线性离子漂移现象,例如在边界附近离子漂移速度降低,

$$

f(w(t))= 1 -(2\frac{w(t)}{D} -1)^{2p},

$$

其中$p$是一个正整数。

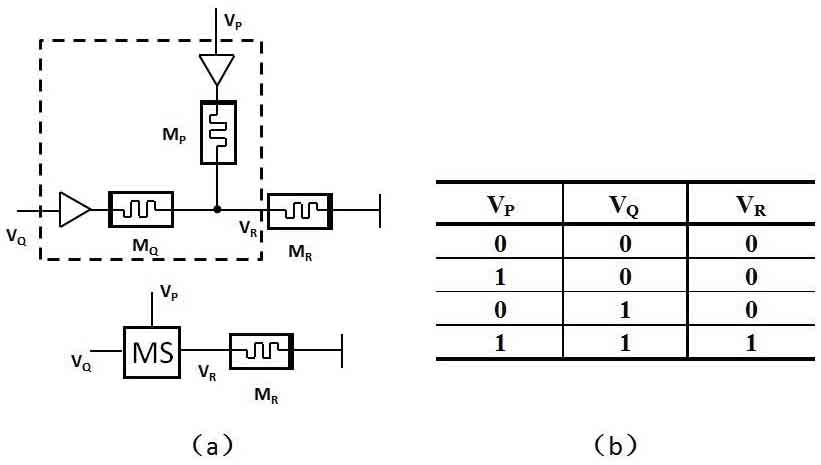

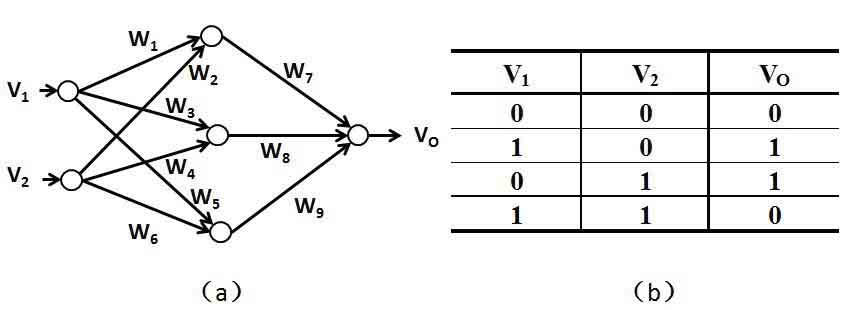

B. 基于忆阻器的逻辑开关

在基于忆阻器的神经网络中,输入电压为$V_H$或0 V。提出的基于忆阻器的与逻辑开关(MS)是[2],的简化形式,由两个忆阻器P和Q通过两个正极连接构成,如图1(a)所示。由于神经网络中的输入电压均为正值,因此 MS中不需要四个忆阻器。$V_P$和$V_Q$是两个输入电压,且

一个基于忆阻器的逻辑开关,以及(b) 与运算的真值表。)

一个基于忆阻器的逻辑开关,以及(b) 与运算的真值表。)

$V_R$是输出。为了确保与运算的正确性,$R_R \ll R_P,R_Q$,如[2]所述。基于忆阻器的与运算的真值表如图1(b)所示。

为简化计算,忽略窗函数。在仿真中考虑了非线性离子漂移现象,并使用了窗函数。假设忆阻器从$R_{ON}$变为$R_{OFF}$或从$R_{OFF}$变为$R_{ON}$所需的时间相同。P和Q忆阻器的初始权重是任意的,MS的开关时间$T_1$为[2]

$$

T_1 \approx \frac{2i_{on}\Delta R R_{OFF}}{k V_H} = \frac{2\beta_1 i_{on} D^2}{\mu_v V_H},

$$

其中$k= \mu_v\Delta R/D^2$, $\Delta R$是$R_{OFF}$与$R_{ON}$($\Delta R= R_{OFF} - R_{ON}$)之间的差值,且 $\beta_1=R_{OFF}/R_{ON}$。$R_{OFF}$和 $R_{ON}$分别为忆阻器P和Q的高、低忆阻值,如图1(a)所示。

假设MS中无阈值。输出误差$V_e$为[2]

$$

V_e \approx \frac{R_Q}{R_P+ R_Q} V_H= \frac{R_{ON}}{R_{OFF}+ R_{ON}} V_H.

$$

要将$R_R$的忆阻值从任意初始忆阻值$R_{Ri}$改变为最终忆阻值$R_{Rf}$,$R_R$与时间$T$之间的关系为[2]

$$

T=

\begin{cases}

\frac{V_R(\ln R_{Ri} - \ln R_{Rf}) -i_0(R_{Ri} - R_{Rf})}{k’i_{off}}, & V_R> 0\

\frac{R_{Ri}^2-R_{Rf}^2}{2k’V_R i_{on}}, & V_R< 0,

\end{cases}

$$

其中$k’=\mu’ v\Delta R R’ {ON}/D^2,$,且$R’_{ON}$是$R_R$的低忆阻值。

当忆阻器$R_R$的忆阻值从$R’ {ON}$变为$R’ {OFF}$时,由公式 (7)可得时间$T_2$为

$$

T_2= \frac{R’^2_{OFF} - R’^2_{ON}}{2k’V_R i_{on}}= \frac{(\beta_2+ 1)D^2}{2\mu’ v V_R i {on}},

$$

其中 $\beta_2= R’ {OFF}/R’ {OFF}$为$R_R$的高忆阻值。$T_1$相对于$T_2$,应尽可能小,以满足 $\beta_1< \beta_2$和 $\mu_v> \mu_{v0}$。

III. 忆阻神经网络电路

在第三节III.A中,基于忆阻器的单层神经网络(SNN)被扩展为多层神经网络(MNN)。此外,在第三节III.B中提出了用于片上MNN的改进的反向传播(BP)学习方法。

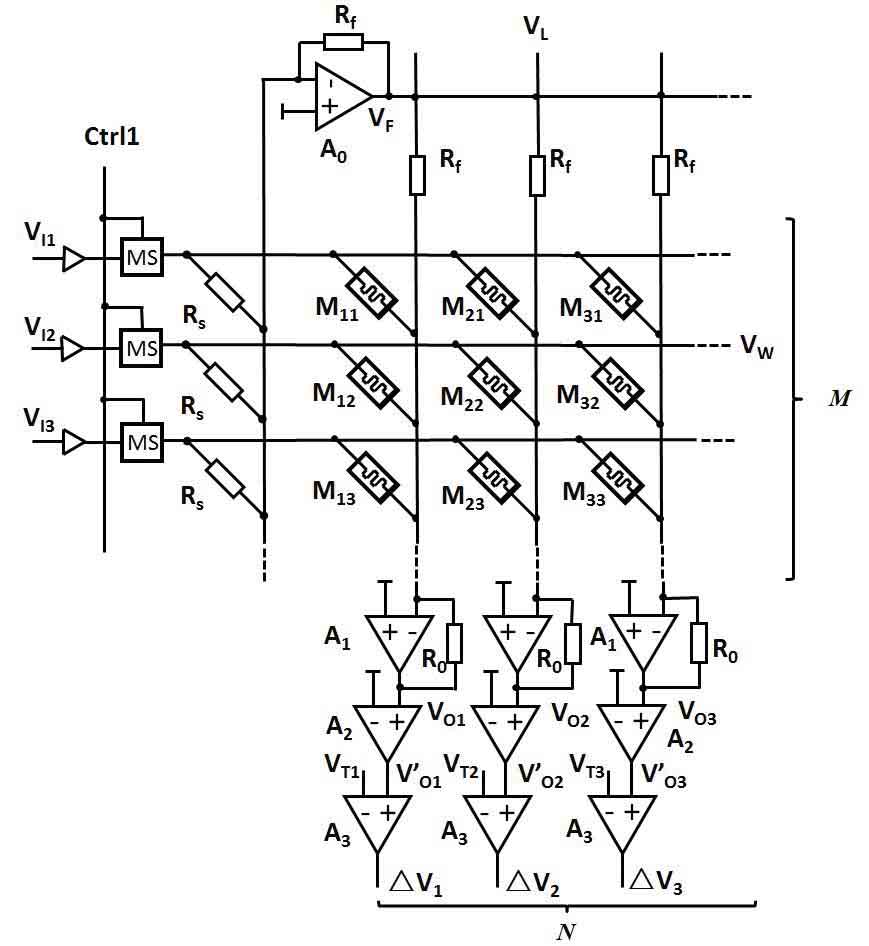

A. 基于忆阻器的SNN

在本节中,忆阻器被用于[26],中的基于忆阻器的突触交叉阵列电路,其中正极性和负极性连接矩阵通过单一交叉阵列和一个简单的恒定项电路实现[26]。第二个放大器A2在输出部分进行了更改(如图2所示),以正确运行神经网络(放大器的正负极端子连接被交换)。此外,添加了放大器A3(如图2所示)以生成误差,并进行更新

芯片上的突触权重。$T_1$小于$T_2$的要求可以通过在忆阻器阵列(MS)和突触中使用不同的忆阻器来实现。突触忆阻器的忆阻值远高于MS中的忆阻器。

假设一个学习系统在$K$次输入的离散迭代上运行,索引为$k = 1,2,…, K$。在每次迭代$k$中,该系统接收一对大小分别为$M$和$N$的向量:$\mathbf{V} I (k) \in \mathbb{R}^M$和输出$\mathbf{V}_O (k) \in \mathbb{R}^N$。例如,假设$W$是一个可调的$N \times M$矩阵,并考虑估计器[23],

$$

\mathbf{V}_O (k)= W(k)\mathbf{V}_I (k),

$$

or

$$

V_O^{(k)}_j= \sum {i=1}^M W^{(k)}_{ji} V_I^{(k)}_i,

$$

其中$i= 1,2,…,M$且$j= 1,2,…,N$。

一种新的突触阵列由一个$M-(G_{ji})$的单一交叉阵列和一个$G_s$的恒定项电路组成,如图2所示。其中,$G_s(G_s= 1/R_s)$是$R_s$的电导,$G_{ji}(G_{ji}= 1/R_{ji})$是第$i$th行与第$j$th列交叉点处的忆阻器电导。$V_{Ii}$是施加到第$i$th行的输入电压。根据基尔霍夫定律,$V_F$是[26]

$$

V_F= -\sum_{i=1}^M \frac{R_f}{R_s} V_{Ii}.

$$

$j$th列的输出电压$V_{Oj}$是

$$

V_{Oj}= -\left[ \sum_{i=1}^M (R_0 \times G_{ji} \times V_{Ii})+ \frac{R_0}{R_f} V_F\right].

$$

将(12)与(11)结合,$V_{Oj}$是

$$

V_{Oj} = \sum_{i=1}^M R_0 \times(G_s - G_{ji}) \times V_{Ii} .

$$

突触权重是

$$

W_{ji}= R_0 \times(G_s - G_{ji}).

$$

比较器使得$V’ {Oj}$作为

$$

V’ {Oj}= f(V_{Oj})=

\begin{cases}

V_H & \text{if } V_{Oj}> 0 \

V_L & \text{if } V_{Oj} \leq 0,

\end{cases}

$$

其中$V_H$和$V_L(V_L= 0)$分别是比较器的高电压和低电压。估计器的输出$\mathbf{V} O= W\mathbf{V}_I$用于预测新出现的未见输入$\mathbf{V}_I$对应的目标输出$\mathbf{V}_T$。为了解决这一问题,突触权重$W$会被更新,以最小化在训练集的一个长度为$K_0$的子集($k= 1,2,…, K_0$)上输出与目标输出之间的误差。误差向量为

$$

\Delta \mathbf{V}(k)= \mathbf{V}_T(k) - \mathbf{V}’_O (k).

$$

一种常见的度量是均方误差(MSE)[23],它是

$$

MSE= \sum {k=1}^{K_0} |\Delta \mathbf{V}(k)|^2.

$$

输出的性能在另一个子集上进行测试,该子集称为测试集($k= K_0+ 1, K_0+ 2,…, K$)。

一种用于最小化目标函数(17)的可行迭代算法是

$$

W(k+1)= W(k) - \frac{1}{2} \eta\nabla_W(k)|\Delta \mathbf{V} (k)|^2,

$$

其中$\eta$是学习率。利用链式法则(9)和(16),$\nabla_W(k)|\Delta \mathbf{V} (k)|^2= -2(\mathbf{V} T(k) - \mathbf{V}’_O (k))(\mathbf{V}_I(k))^T$。因此,定义$\Delta W(k) \equiv W(k+1) -W(k)$,外积为

$$

\Delta W(k)= \eta\Delta \mathbf{V}(k)(\mathbf{V}_I (k))^T,

$$

or

$$

\Delta W^{(k)} {ji}= W^{(k+1)} {ji} - W^{(k)} {ji}= \eta\Delta V^{(k)} j(V^{(k)} {Ii}).

$$

具体而言,MNNs通常使用BP算法进行训练,这是一种在线梯度下降[43]的有效形式。重要的是,注意(20)中的更新规则是局部的,即突触权重$W^{(k)} {ji}$的变化仅依赖于输入$V^{(k)} {Ii}$和误差$\Delta V^{(k)}_j$。

为了实现神经网络的BP训练,需为每一步确定相关时间。由(14)得,

$$

\Delta W^{(k)} {ji}= -R_0\Delta G^{(k)} {ji}.

$$

由(20)得,

$$

\Delta W^{(k)} {ji}= \eta(V^{(k)} {Tj} - V’^{(k)} {Oj} )V^{(k)} {Ii}

=

\begin{cases}

0 & \text{if } V^{(k)} {Tj} = V’^{(k)} {Oj} \text{ or } V^{(k)} {Ii}= 0 \

\eta V_H^2 & \text{if } V^{(k)} {Ii}= V_H, V^{(k)} {Tj} = V_H, V’^{(k)} {Oj} = 0 \

-\eta V_H^2 & \text{if } V^{(k)} {Ii} = V_H, V^{(k)} {Tj} = 0, V’^{(k)} {Oj} = V_H.

\end{cases}

$$

如果$\Delta W^{(k)} {ji} = 0$,

$$

| \Delta G^{(k)} {ji} |=\left| \frac{1}{R^{(k+1)} {ji}} - \frac{1}{R^{(k)} {ji}} \right|= \frac{\eta V_H^2}{R_0}.

$$

假设$W {ji} \in[-1, 1]$而$R_{ji} \in[R’ {ON},R’ {OFF}]$,$R_0,R_s,R_f$由(14)确定。由(7)可得,每一步的时间$T(k)$为

$$

T(k)=

\begin{cases}

\frac{V_W(\ln R^{(k)} {ji} - \ln R^{(k+1)})-i_0(R^{(k)} {ji} -R^{(k+1)})}{k’i_{off}}, & V_W>0\

\frac{(R^{(k)} {ji})^2-(R^{(k+1)})^2}{2k’V_W i {on}}, & V_W<0.

\end{cases}

$$

B. 基于忆阻器的MNN

一个简单的两层神经网络可以扩展为多层神经网络,如图3所示。考虑一个两层交叉阵列。在第1层中,一个$N\times M$矩阵$W^{(1)}(W_{ji})$对应$N$个神经元和$M$个输入。在第2层中,一个$P\times N$矩阵$W^{(2)}(W_{pj})$对应$P$个神经元和$N$个输入。

自适应BP算法是[30]

1) 使用高忆阻值$R’ {OFF}$初始化忆阻器。2) 随机对所有忆阻器施加权重更新电压$V_W$,以记录初始权重($W^{(1)} {ji}$和$W^{(1)} {pj}$)和忆阻值($R^{(1)} {ji}$和$R^{(1)} {pj}$)的所有随机值。3) 将输入模式$\mathbf{V}_I$施加到交叉阵列电路,并计算隐层和输出层神经元值。

4) 对于输出层神经元,确定神经元输出$\mathbf{V}’_O$与目标输出$\mathbf{V}_T$之间的误差$\Delta \mathbf{V}$。

$$

\Delta V^{(k)} {1j} = \sum_{p= 1}^P \Delta V^{(k)} {2p} W^{(k)} {pj}.

$$

5) 反向传播误差

$$

\Delta W^{(k)} {pj}= \eta(V^{(k)} {T2p} - V’^{(k)} {O2p})V^{(k)} {I2j}

=

\begin{cases}

0 & \text{if } V^{(k)} {T2p}= V’^{(k)} {O2p} \text{ or } V^{(k)} {I2j}= 0\

\eta V_H^2 & \text{if } V^{(k)} {I2j}= V_H, V^{(k)} {T2p}= V_H, V’^{(k)} {O2p}= 0\

-\eta V_H^2 & \text{if } V^{(k)} {I2j}= V_H, V^{(k)} {T2p}= 0, V’^{(k)} {O2p}= V_H,

\end{cases}

$$

其中神经元$p$与前一层神经元$j$相连。

6) 向交叉阵列施加写入脉冲,脉冲宽度与$\Delta W {pj}$成正比,以更新忆阻器电导。如果$\Delta W^{(k)} {pj} = 0$,

$$

| \Delta G^{(k)} {pj} |=\left| \frac{1}{R^{(k+1)} {pj}} - \frac{1}{R^{(k)} {pj}} \right|= \frac{\eta V_H^2}{R_0}.

$$

7) 确定$\Delta W^{(k)} {ji}$,以确保每个忆阻器电导都发生变化。

$$

\Delta W^{(k)} {ji}= \eta\Delta V^{(k)} {1j} V^{(k)} {I1i}

=

\begin{cases}

0 & \text{if } V^{(k)} {I1i}= 0\

\eta V_H\sum {p=1}^P \Delta V^{(k)} {2p} W^{(k)} {pj} & \text{if } V^{(k)} {I1i} = V_H.

\end{cases}

$$

8) 向交叉阵列施加写入脉冲,脉冲宽度与$\Delta W^{(k)} {ji}$成正比,以更新忆阻器电导。如果$\Delta W^{(k)} {ji} = 0$,

$$

| \Delta G^{(k)} {ji} | = \left| \frac{1}{R^{(k+1)} {ji}} - \frac{1}{R^{(k)} {ji}} \right| = \left| \frac{\eta V_H\sum_{p=1}^P\Delta V^{(k)} {2p} W^{(k)} {pj}}{R_0} \right|.

$$

9) 如果误差未收敛到足够小的值,则返回步骤2)。

备注1: 使用类似的方法,(24)‐(29)可以写成描述$N$层的通用表达式。

IV. 系统操作

本节介绍了在片上执行所提出的BP训练和突触权重调整过程的方法,这些方法具有无串扰路径的优点。在IV.A节中,提出了一种四步片上BP训练方法。在IV.B节中描述了用于改变神经网络阵列中突触权重的串扰路径方法。

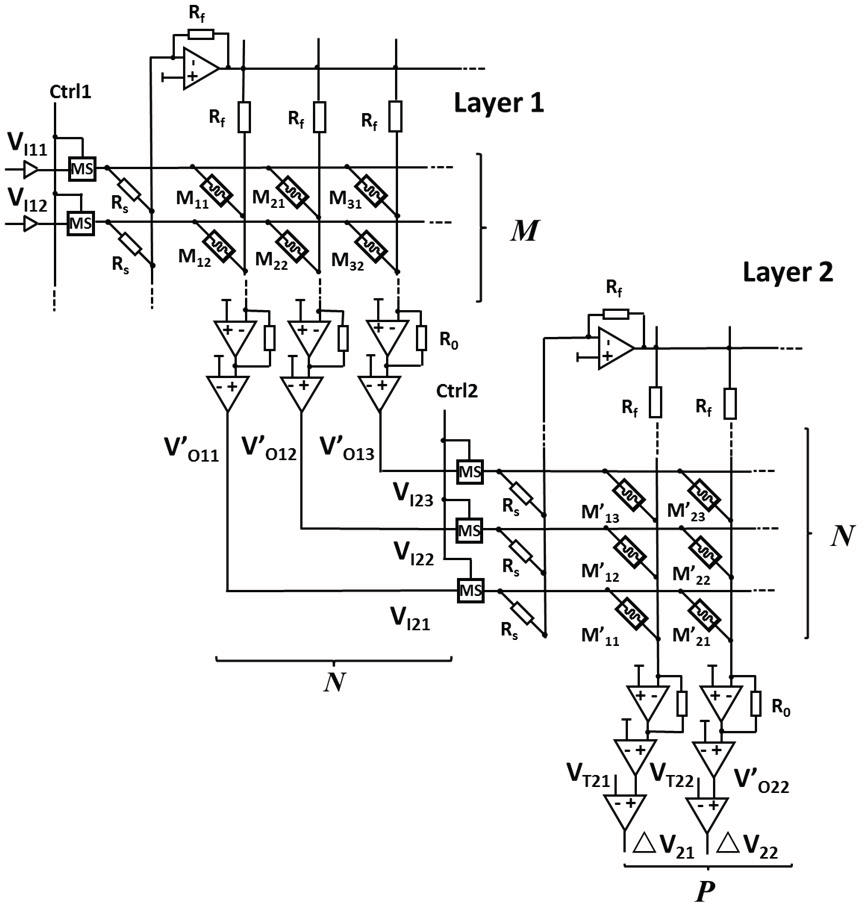

A. BP训练电路

神经网络电路的BP训练电路实现如图3所示。该训练由四个步骤[30]组成:1将输入电压施加到第一层,并记录第2层神经元输出误差。2通过第二层权重反向传播第2层误差,并记录第一层误差。

M22从1调整为−1,以及(b) M22从−1调整为1。)

M22从1调整为−1,以及(b) M22从−1调整为1。)

3根据第2层误差更新第2层突触权重。

4根据第一层误差更新第一层突触权重。

所提出的BP训练的四步操作描述如下:

步骤1: 将输入信号Ctrl1和Ctrl2设置为$V_H$,以导通MS。一组输入电压施加到第1层神经元上,第2层神经元的输出$V_{O21}$、$V_{O22}$、⋯⋯、$V_{O2p}$、⋯⋯、$V_{O2P}$与期望输出$V_{T21}$、$V_{T22}$、⋯⋯、$V_{T2p}$、⋯⋯、$V_{T2P}$进行比较。该过程如图3所示。误差项$\Delta V_{21}$、$\Delta V_{22}$,、⋯⋯、$\Delta V_{2p}$、⋯⋯、$\Delta V_{2P}$基于观测输出与期望输出之间的差异。这些值由比较器生成,提供离散化误差值$V_H$、$-V_H$或0。这些误差被放大(至2 V、$-2$ V或0)并施加到突触阵列上,以改变忆阻值,如图4所示。

$|\Delta W_{ji}|$的值可在测试过程中获得,并通过FPGA或LUT(查找表)计算对应的$|\Delta G_{ji}|$(或$|\Delta R_{ji}|$)。忆阻器的初始状态被记录下来,调整时间的计算可在FPGA中完成。每个突触的调整均由外围电路控制。

步骤2: 为了反向传播第2层的误差,将Ctrl1和Ctrl2设置为$V_H$。将第2层的误差($\Delta V_{21},\Delta V_{22},…,\Delta V_{2p},…,\Delta V_{2P}$)应用于第2层的权重,以生成第1层的误差($\Delta V_{11},\Delta V_{12},…,\Delta V_{1j},…,\Delta V_{1N}$)。

步骤3: 将Ctrl1和Ctrl2设为0(关断MS),以隔离第二层交叉阵列与第一层。训练单元将第2层误差与第2层中间输出一同放大,生成一组训练脉冲。这些脉冲被施加到第2层忆阻器交叉阵列上,以更新第2层突触权重。

步骤4: 为了将第一层交叉阵列与输入电压隔离,将Ctrl1和Ctrl2设置为0。应用类似于步骤3的过程来更新第一层忆阻器交叉阵列中的突触权重。

B. 突触权重更新

在测试过程中,施加的电压是输入电压0或$V_H$。最终输出电压是误差信号电压0、$V_H$或$-V_H$。施加的权重更新电压被放大为0、2 V或$-2$ V,由

外围电路。本节介绍了训练单元所使用的忆阻器权重更新过程。

交叉阵列中的所有权重都可以使用以下方法进行更新。

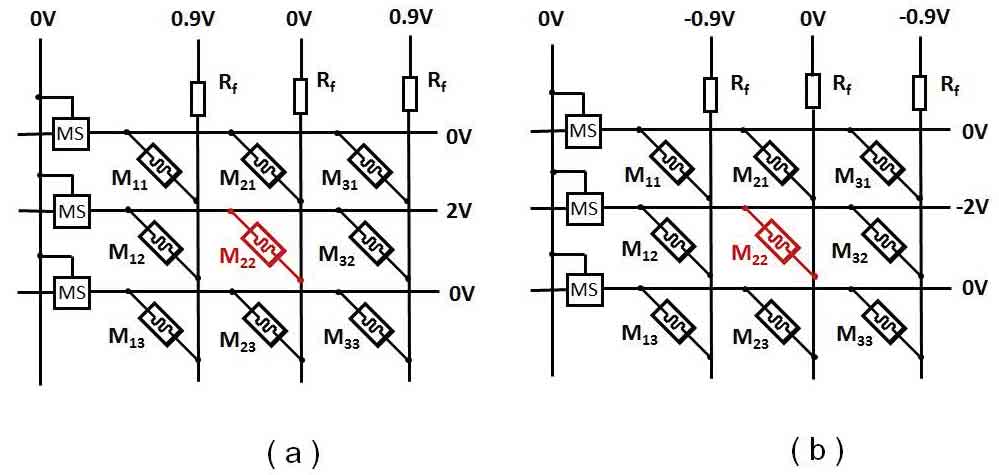

已评估了不同网格尺寸的交叉阵列,以3×3交叉阵列为例。当在忆阻器两端施加的电压大于忆阻器阈值时,忆阻值会根据器件端子的极性增加或减少。$\Delta V_j$的两种可能更新情况连同权重变化方向列于表I中,或者$\Delta V_j= 0$,此时权重保持不变。

1) 降低突触权重: 如果$\Delta V_j< 0$,$V_W> 0$。假设只有忆阻器M22发生变化,而其他忆阻器保持不变。一种可能的解决方案是在不同的行和列上施加不同的电压。在第2行施加$V_W= 2$ V电压,其他行连接到地,第2列连接到地,而在其他列施加0.9 V电压,如图4(a)所示。突触忆阻器的阈值电压($V_T$)为1.5 V,且$R_f$远小于$M_{ji}$的忆阻值。只有忆阻器M22上的电压为2 V,大于$V_T$,因此M22的忆阻值降低。忆阻器M11, 、M13,、M31,和M33上的电压为$-0.9$ V,忆阻器M12和M32上的电压为1.1 V,忆阻器M21和M23上的电压为0 V。这些电压的绝对值均小于$V_T$,因此它们的忆阻值保持不变。

2) 增加突触权重: 如果$\Delta V_j> 0$,$V_W< 0$。采用类似的方法,如图4(b)所示。

为了改变忆阻器电导,需在忆阻器两端施加适当幅值、极性和持续时间的电压[44]–[46]。在每一步中,所需持续时间$T^{(1)}_2, T^{(2)}_2,…, T^{(k)}_2,…, T^{(K)}_2$可由(27)和(24)确定,而$T^{(1)}_1, T^{(2)}_1,…, T^{(k)}_1,…, T^{(K)}_1$可由(29)和(24)确定。

V. 鲁棒性分析

工艺变化和噪声会显著影响电路性能。本节讨论这些噪声源、物理设计挑战的影响以及串扰电流。

A. 噪声来源

来自电源和邻近导线的电噪声会显著降低模拟信号的质量。与电路制造完成后保持不变的工艺变化不同,信号波动在电路操作期间会发生变化。当在片上进行字符识别时,输入电压可能会受到随机噪声的影响。通过将输入从0改变到$V_H$来评估所提出的MS和突触电路的鲁棒性。

B. 物理挑战

存在四个主要物理限制:1) MS和突触阵列中的忆阻器不同;2) 边界电压$V_H$小于忆阻器的$V_T$;3) $V_H$与噪声源的最大幅度之和小于$V_T$。4) 突触调节过程的精度取决于忆阻器电导的精度,并通过施加不同数量的电压脉冲进行调整。

C. 串扰电流

训练过程不受串扰电流[47]的影响。仅有一条写入线被抬升至达到权重改变电压$V_W$,其他线路被保护,以确保电压的绝对值保持小于$V_T$,如图4所示。$V_W$被设置得高于$V_T$,因为在每次训练步骤中仅需忆阻值发生微小变化。因此,其他忆阻器上的电压降小于$V_T$,不会导致忆阻值的意外变化。然而,在更大的阵列中,经过大量脉冲后(例如16 kb阵列经过$5 \times 10^6$个脉冲),写入操作受到干扰,并出现164个错误位[48]。

VI. 仿真结果

使用PSPICE对所提出的基于忆阻器的MNN电路进行评估。电路和学习过程也在Matlab中进行了评估。仿真中同时采用了基本忆阻器模型[38]和具有阈值电压的突触模型[41]。基于忆阻器的MNN的参数列于表II中。放大器A0和A1的驱动电压分别为±5 V、0.9 V和0 V,对应于A2,以及±0.9 V对应于A3。需要多种不同的电压电平,±5 V电压通过降压电路用于产生±0.9 V和±2 V电压。由基于忆阻器的突触联支持的权重范围为$[-1,+1]$。

A. 突触权重更新

考虑了不同网格尺寸的交叉阵列。例如,一个3×3交叉阵列考虑了忆阻器

M22在第二行第二列被访问。通过采用突触权重更新方法,仿真结果表明,在权重更新过程中,只有M22可以从$R’ {OFF}$更新到$R’ {ON}$,或从$R’ {ON}$更新到$R’ {OFF}$(如图5所示),而其他忆阻器保持不变,验证了串扰电流在权重更新过程中已被消除。

用于权重调整操作的输入电压$V_W$,(b) 忆阻器M11的忆阻值(M13、M31、M33相同),(c) 忆阻器M12的忆阻值(M32相同),(d) 忆阻器M21的忆阻值(M23相同),以及(e) 忆阻器M22的忆阻值。X表示时间,Y表示电压。)

用于权重调整操作的输入电压$V_W$,(b) 忆阻器M11的忆阻值(M13、M31、M33相同),(c) 忆阻器M12的忆阻值(M32相同),(d) 忆阻器M21的忆阻值(M23相同),以及(e) 忆阻器M22的忆阻值。X表示时间,Y表示电压。)

开关时间(门延迟)从(5)得出约为0.02纳秒,误差从(6)得出约为0.01伏特。从(8)得出,一个幅值为2 V、宽度为0.61 ns的脉冲将忆阻值从$R’ {OFF}$变为$R’ {ON}$(突触联的权重从1变为$-1$)。类似地,一个幅值为$-2$ V、宽度为0.61 ns的脉冲将忆阻值从$R’ {ON}$变为$R’ {OFF}$(突触联的权重从$-1$变为1),如图5所示。

B. 异或函数

一个简单的双层神经网络被用于验证该学习方法的正确性。如图7所示,该网络在具有2个输入 × 3 hiddens × 1输出的结构上学习异或函数。在第1层中,一个3 × 2忆阻器矩阵对应三个神经元和两个输入。在第2层中,一个1×3忆阻器矩阵对应三个输入和一个输出。

一个周期包含针对四种不同输入模式的四次迭代,学习率为$\eta= 0.1$。每次迭代期间的输出电压如图6所示。每个周期中每个神经元的硬件训练过程的误差如图8所示(测试了1000个事件以生成不同的样本)。误差$E_e$是

$$

E_e=\sqrt{ \frac{1}{K_0} MSE}.

$$

输入电压$V_{I11}$,(b) 输入电压$V_{I12}$,以及(c) 输出电压$V’_{O21}$.)

输入电压$V_{I11}$,(b) 输入电压$V_{I12}$,以及(c) 输出电压$V’_{O21}$.)

MNN,和(b) 真值表。)

MNN,和(b) 真值表。)

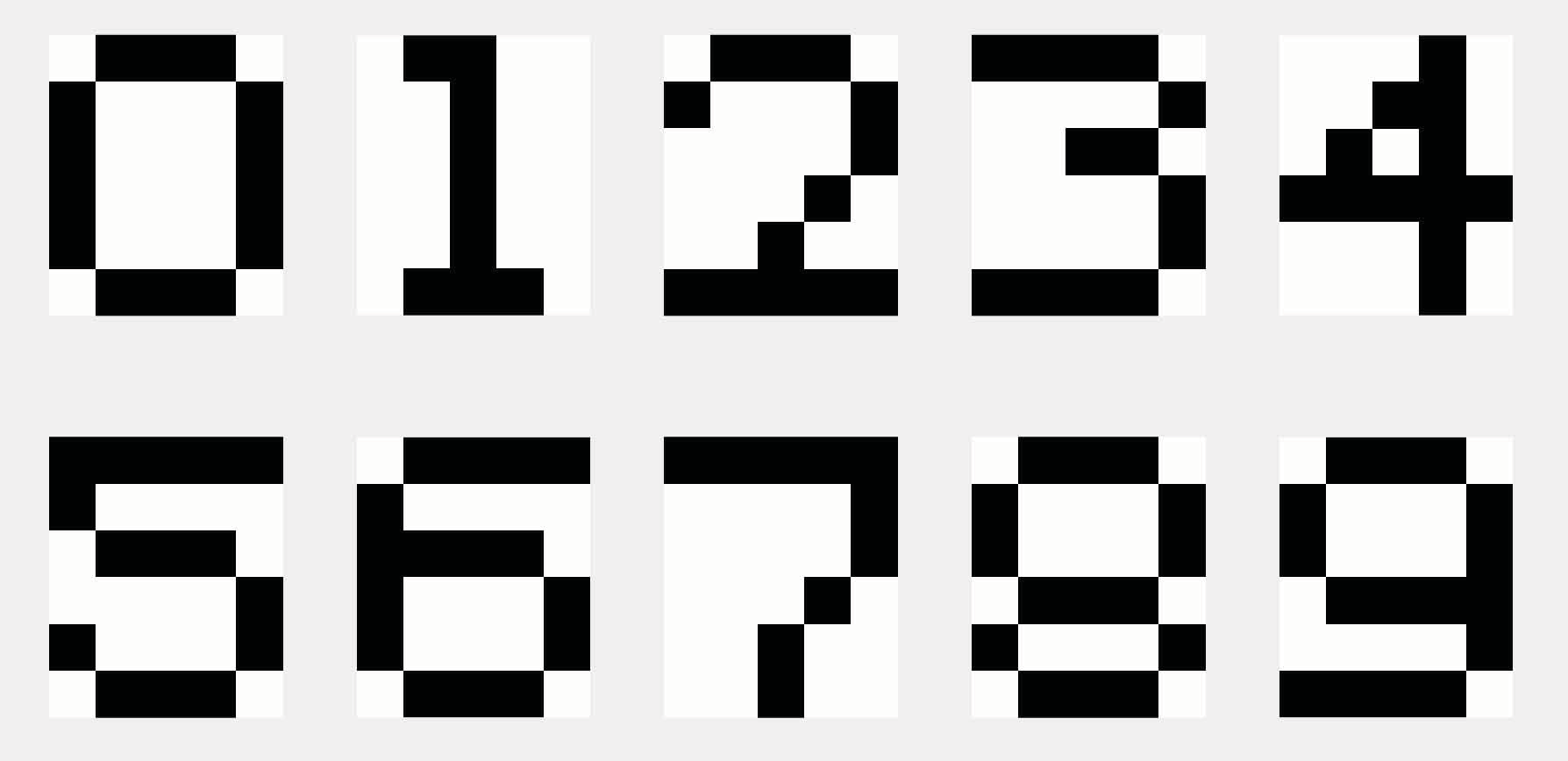

C. 字符识别

更复杂的函数在用于字符识别的两个不同的网络上进行模拟。其中一个网络是单个

由30个输入 × 10输出组成的层。该网络在尺寸为5×6像素的黑白图像上进行训练,如图9所示。以图像5为例,输入和输出电压如表III所示(“1”表示$V_H$)。一个周期包含针对十种不同的输入模式的十次迭代,学习率为$\eta= 0.1$。硬件的误差($K_0= 10$)

输入图像无噪声,(b) 输入图像含有20%噪声。)

每个周期中每个神经元的训练如图11(a)所示(测试了1000个事件以生成不同的样本)。

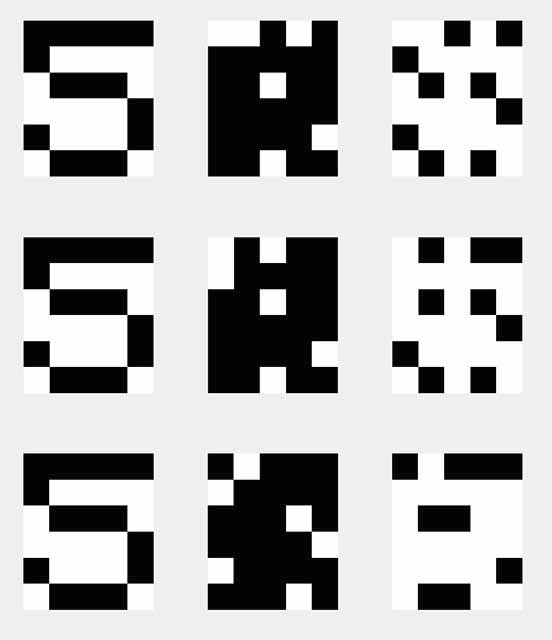

使用以下方法测试司法电阻式神经网络电路的鲁棒性。向输入图像添加噪声

(例如数字5)生成噪声图像,如图10所示。数字5的原始图像显示在左列,均匀随机噪声掩码图像显示在中间列。通过在噪声掩码图像中存在白像素的位置翻转字符图像中的所有像素来获得噪声图像(假设噪声为20%)。正确识别的平均循环次数如图11(b)所示。当图像中加入20%噪声时,网络的识别率为99.0%,如表IV所列。

另一个示例网络包含两层,分别为30个输入 × 6隐含层 × 4输出层。再次以图像5为例,其输入和输出电压列于表III中。一个周期包含十次迭代,对应十种不同的输入模式,学习率为$\eta= 0.04$。图12显示了每个周期中每个神经元的硬件训练误差($K_0= 10$)(测试了1000个事件以生成不同样本)。仿真结果显示,当图像加入20%噪声时,该网络的识别率为95.4%。

在向图像添加噪声的情况下,所提出的基于忆阻器的神经网络的识别率与[18]在表IV中进行了比较。所提出的基于忆阻器的BP算法与胜者为王算法在表V中进行了比较[18]。需要注意的是,所提出的系统表现出更高的识别率且需要更少的周期。

D. 忆阻值变化的影响

在实际制造的忆阻器阵列中,更新过程通过施加不同数量的正或负电压脉冲来实现。在每一步中,忆阻器的忆阻值或电导无法被精确调整,因此本节讨论忆阻值变化的影响。

为了获得期望的忆阻值变化,需要施加适当幅值和极性的电压,并持续适当的时间

脉冲次数施加在忆阻器上。然而,由于周期间的差异,每一步的变化无法被精确控制。因此,在每一步中向忆阻值添加了范围从5%到15%的不同随机噪声,如图13所示。相应的周期数分别为14、30和48。所提出的基于忆阻器的MNN表现出对忆阻值变化的固有容忍性。

VII. 结论

提出了一种用于具有片上学习功能的多层神经网络的单个基于忆阻器的突触结构。此外,应用一种适用于该忆阻器基多层神经网络的自适应BP算法来训练神经网络,并实现异或函数和字符识别。通过结合忆阻器基突触结构与所提出的BP权重变化算法的优势,可构建一种简单、紧凑且可靠的神经网络,用于模式识别应用。仿真结果验证了所提结构的优势,表明所提出的自适应BP算法具有更高的识别率并需要更少的周期。

113

113

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?