- 在FPGA开发过程中,在使用AXI4总线传输的过程中,需要用的各种不同的IP核,尤其是AXI4-Stream Interconncet IP核,在具有多个M端和S端的时候,需要用到通道切换,这里对通道切换的过程进行说明。

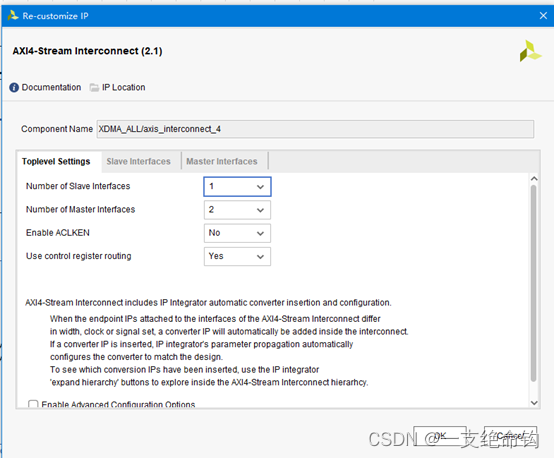

- IP核设置

首先对IP核进行设置,这里以两个Msater为例,注意选择Use control register routing选项。

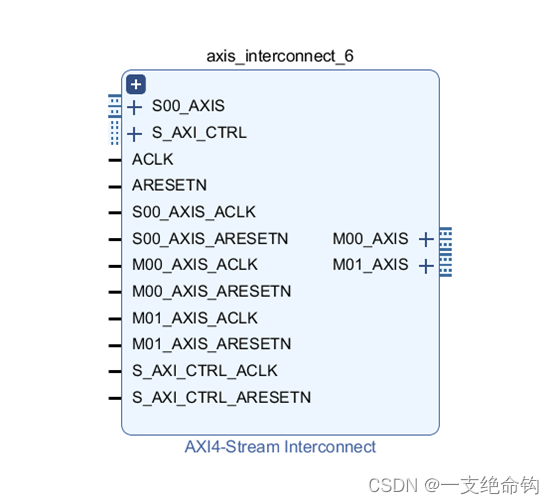

在设置好后,会在生成的IP核看到一个S_AXI_CTRL,这个通道的接口就是用来控制选择S端与M端通道匹配的;

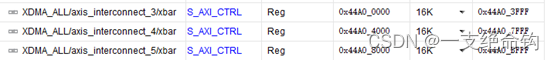

2. 配置bar空间地址

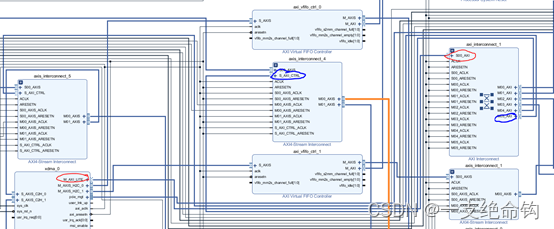

图中为相连接的线,通过连接到xdma中的M_AXI_LITE分配bar空间地址,

然后在address editor中进行地址的分配,这里地址和对应的IP核参照表格,

图中现在想控制的通道为中间的axis_interconnect_4 IP 核的通道,根据不同的需求,可以切换为数据走M00_AXIS通道或者M01_AXIS通道。

3. 寄存器配置

为了控制通道的切换,需要进行寄存器的配置工作,参考PG085

本文详细阐述了在FPGA开发中使用AXI4-StreamInterconnect IP核时,如何配置多通道切换,包括设置IP核、分配bar空间地址、寄存器配置等步骤,重点讲解了S_AXI_CTRL接口的选择和通道关闭技巧。

本文详细阐述了在FPGA开发中使用AXI4-StreamInterconnect IP核时,如何配置多通道切换,包括设置IP核、分配bar空间地址、寄存器配置等步骤,重点讲解了S_AXI_CTRL接口的选择和通道关闭技巧。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

3085

3085

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?