VCS和Quartus联合仿真

使用VCS对Quartus工程进行编译仿真,仿真的内容主要是IP核,仿真过程分为单IP核和多IP核两种情况,以乘法器IP核和除法器IP核为例,进行说明

文章目录

1. 单IP核仿真

1.1 新建工程,添加IP核文件

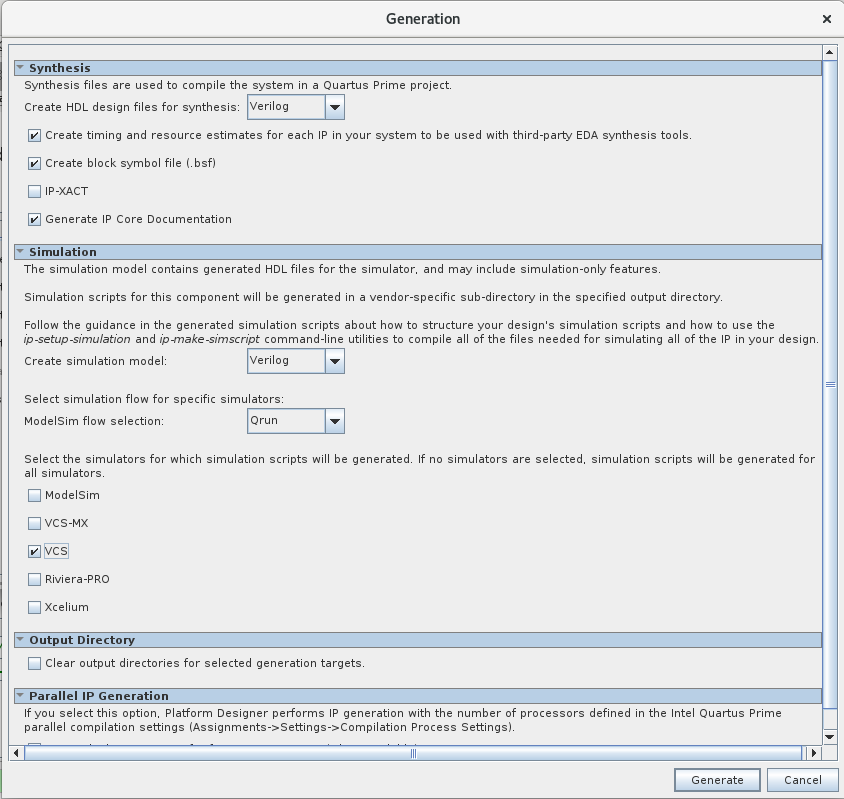

新建Quartus工程,随便命名,这里命名为mult_top,通过IP catalog添加IP核,这里面添加乘法器IP核,设置输入8位,输出16位,然后点击生成HDL文件,在弹出的生成界面,需要设置仿真选项,这里面使用的是VCS仿真器,所以需要选中VCS。

仿真中IP核设置的名字为MultiIP,这里面在工程目录中创建了名称IP的文件夹,用来放IP核文件,输入数据的位宽为8位,输出数据的位宽为16位。

1.2 添加顶层文件

新建顶层文件,其实可以直接添加testbench文件,在这还是添加一个顶层文件。

新建文件mult_top.v,内容如下:

module mult_top(

input clk ,

input rst_n ,

input [7:0] a,

input [7:0] b,

output [15:0] c,

output reg [3:0] cnt );

always @(posedge clk or negedge rst_n) begin

if(!rst_n)

cnt <= 0;

else if(cnt == 9)

cnt <= 0;

else

cnt <= cnt + 1;

end

multIP u0 (

.result (c), // output, width = 9, result.result

.dataa_0 (a), // input, width = 8, dataa_0.dataa_0

.datab_0 (b) // input, width = 8, datab_0.datab_0

);

endmodule

1.3 添加testbench文件

新建testbench文件,也可以利用生成的模板进行修改,在这里自己新建文件。Testbench文件为top_tb.sv,内容如下:

`timescale 1 ps/ 1 ps

module top_tb();

//----------------------------------------

reg clk ;

reg rst_n ;

reg [7:0] add_a;

reg [7:0] add_b;

wire [15:0] result_c;

wire [3:0] cnt ;

//----------------------------------------

mult_top u_top

(

.clk (clk ),

.rst_n (rst_n ),

.a(add_a),

.b(add_b),

.c(result_c)

);

//----------------------------------------

initial clk = 1'b1;

always #10 clk = ~clk;

initial begin

rst_n = 0; #11 rst_n = 1;

end

//----------------------------------------

`ifdef DUMP_VPD

initial begin

$vcdpluson;

#1000;

$vcdplusflush;

$finish;

end

`elsif DUMP_FSDB

initial begin

add_a = 8'd10;

add_b = 8'd10;

#100;

add_a = 8'd5;

#100;

add_a = 8'd24;

#100;

add_b = 8'd17;

#800

$finish;

end

initial begin

$fsdbDumpfile("tb_top.fsdb");

$fsdbDumpvars("+all");

end

`endif

endmodule

在Assignments->Settings->EDA Tool Settings中设置仿真工具和Testbench

在simulation选项中,选择VCS仿真工具,verilog语言,输出文件夹。

在Testbench specification选项中点击Edit,添加创建好的Testbench文件,这里面是top_tb.sv文件

1.4 Dump波形

为了能够在verdi中仿真波形,需要保存波形文件,在testbench中已经添加以下代码:

$fsdbDumpfile("tb_top.fsdb);

$fsdbDumpvars(0, tb_top); //0表示从0开始

//$fsdbDumpvars("+add"); //+add表示将所有变量都保存到波形文件中

1.5 编译仿真脚本创建

在生成的IP核保存的目录中,{project_dir}/ip/multIP/sim/synopsys/vcs下,有一个名为vcs_setup.sh的脚本,仿真主要是使用这个脚本,需要参照该脚本中的内容,创建一个.sh的仿真脚本,一个filelist.f文件。

- vcs_sim.sh

在这个仿真过程中,在工程目录中创建了名为vcs_sim.sh的脚本,在脚本中添加了仿真指令,具体指令如下:

source {project_dir}/ip/multIP/sim/synopsys/vcs/vcs_setup.sh \

TOP_LEVEL_NAME=top_tb \

SKIP_SIM=1 \

QSYS_SIMDIR="{project_dir}/ip/multIP/sim" \

USER_DEFINED_ELAB_OPTIONS="\"-f filelist.f\"" \

USER_DEFINED_SIM_OPTIONS=""

- filelist.f

创建flielist.f文件,在文件中添加需要仿真的文件,

因为在Testbench中Dump波形在verdi中使用,编译的时候,需要在编译选项中添加novas.tab文件和pli.a文件的路径,否则编译的时候会提示FSDB相关的错误。添加的具体编译指令如下:

-P ${VERDI_HOME}/share/PLI/VCS/LINUX64/novas.tab ${VERDI_HOME}/share/PLI/VCS/LINUX64/pli.a

最终filelist.f文件中的具体指令如下:

+systemverilogext+.sv

-top top_tb -full64 -l sim.txt -debug_access+r+w+nomemcbk +define+DUMP_FSDB -debug_pp -LDFLAGS -rdynamic -kdb -debug_region+cell+encrypt -line -timescale=1ps/1ps -sverilog +v2k +verilog2001ext+.v -P ${VERDI_HOME}/share/PLI/VCS/LINUX64/novas.tab ${VERDI_HOME}/share/PLI/VCS/LINUX64/pli.a {project_dir}/mult_top.v {project_dir}/top_tb.sv

需要把其中的{project_dir}替换为实际的工程目录。

然后就可以在终端直接运行vcs_sim.sh脚本,会在文件夹中生成simv文件。

可以在vcs_sim.sh脚本中直接添加仿真命令,这里没有添加,需要再运行一下simv文件。

之后启动verdi加载工程和tb_top.fsdb文件,进行仿真。

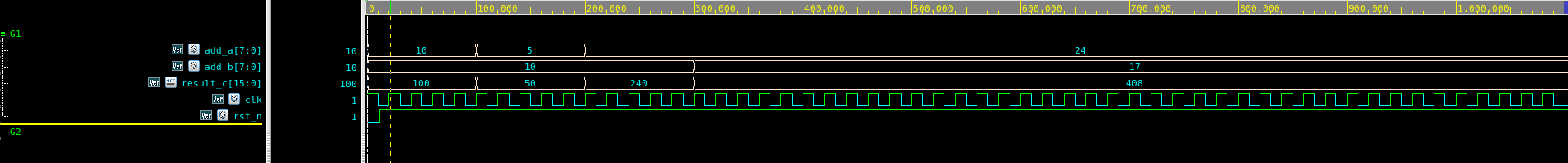

可以得到如下的波形,乘法过程,说明整个编译仿真过程顺利完成。

2. 多IP核仿真

接下来增加一个除法器IP核,实现除法功能,实现多IP核仿真。

2.1 添加IP核

在这里除法器命名为dividIP,输入分子16位,输入分母8位,(主要是对应乘法器)添加过程和添加乘法器IP核的过程相同,最后生成IP核文件。

2.2 修改testbanch文件

为了测试方便,不对顶层文件进行更改,可以直接修改testbench文件,在里面例化除法器IP核,然后进行仿真。用乘法器的输出作为除法器的输入,需要增加除法器的输出,注意位宽大小匹配。

修改后具体内容如下:

`timescale 1 ps/ 1 ps

module top_tb();

//----------------------------------------

reg clk ;

reg rst_n ;

reg [7:0] add_a;

reg [7:0] add_b;

wire [15:0] result_c;

wire [3:0] cnt ;

wire [15:0] da;

wire [7:0] db;

//----------------------------------------

mult_top u_top

(

.clk (clk ),

.rst_n (rst_n ),

.a(add_a),

.b(add_b),

.c(result_c)

);

dividIP divid_u0(

.numer(result_c), // lpm_divide_input.numer, Numerator of the fraction for the division, can be signed or unsigned

.denom(add_a), // .denom, Denominator of the fraction for the division, can be signed or unsigned

.quotient(da), // lpm_divide_output.quotient, Result of the division

.remain(db) // .remain, Remain of the Divison

);

//----------------------------------------

initial clk = 1'b1;

always #10 clk = ~clk;

initial begin

rst_n = 0; #11 rst_n = 1;

end

//----------------------------------------

`ifdef DUMP_VPD

initial begin

$vcdpluson;

#1000;

$vcdplusflush;

$finish;

end

`elsif DUMP_FSDB

initial begin

add_a = 8'd10;

add_b = 8'd10;

#100;

add_a = 8'd5;

#100;

add_a = 8'd24;

#100;

add_b = 8'd17;

#800

$finish;

end

initial begin

$fsdbDumpfile("tb_top.fsdb");

$fsdbDumpvars("+all");

end

`endif

endmodule

2.3 生成仿真脚本

需要在工程目录中利用如下指令生成多IP核仿真脚本,在生成的脚本中有解释,该指令会识别工程中的不同IP核,然后可以用生成的脚本进行仿真。

ip-setup-simulation --quartus-project=mult_top //后面是工程名

可以用参数--output-directory=<directory>指定脚本输出目录,否则默认输出文件的位置为当前目录位置(最好是指定输出目录,或者在选定的目录中执行,输出文件不止一个)

该指令执行完毕之后,和单IP核一样,使用的是文件夹中synopsys/vcs/vcs_setup.sh文件。

2.4 创建脚本

利用synopsys/vcs/文件夹下的vcs_setup.sh文件来创建vcs_sim.sh文件和filelist.f文件,这文件夹是刚才运行ip-setup-simulation指令生成的目录。创建这两个文件的过程与上面单IP核一致,需要参考vcs_setup.sh文件。

其实也可以直接对单IP核中的使用过的两个文件直接进行更改,这里面需要更改的是vcs_sim.sh文件,

- vcs_sim.sh

需要把其中的source后面的脚本更换为synopsys/vcs/文件夹下的vcs_setup.sh,QSYS_SIMDIR改为ip-setup-simulation指令输出的目录。

具体如下:(这里面是运行ip-setup-simulation指令是在工程目录运行的,没有指定输出目录,所以输出文件在当前目录下)

source {project_dir}/synopsys/vcs/vcs_setup.sh \

TOP_LEVEL_NAME=top_tb \

SKIP_SIM=1 \

QSYS_SIMDIR="{project_dir}" \

USER_DEFINED_ELAB_OPTIONS="\"-f filelist.f\"" \

USER_DEFINED_SIM_OPTIONS=""

- filelist.f

filelist.f文件不需要更改。

2.5 仿真结果

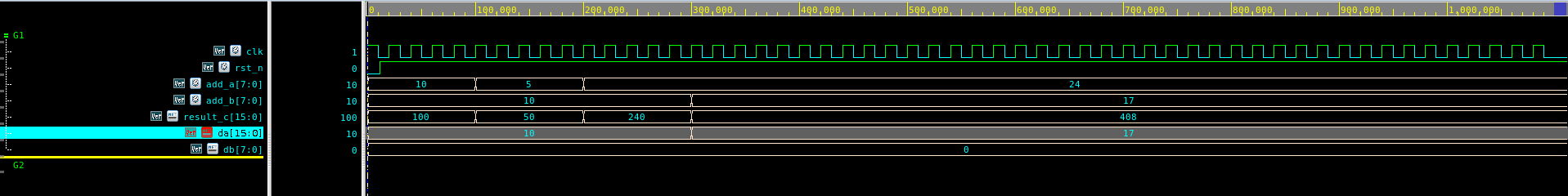

运行vcs_sim.sh文件,利用生成的simv文件进行仿真,结果如下:

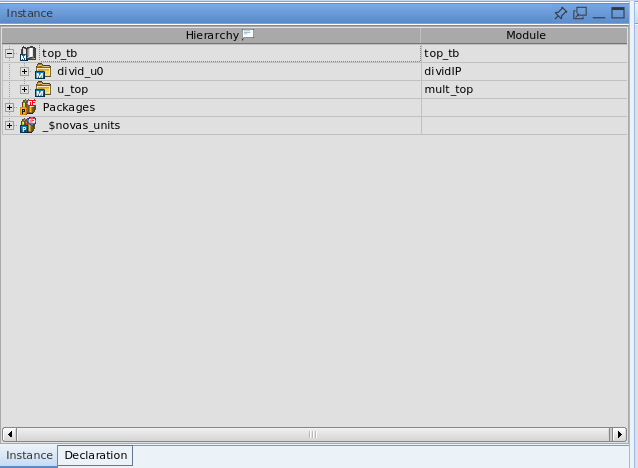

在verdi中可以看到增加除法器IP后的层次结构,已经正确识别

加载波形文件,对照乘法器输入输出,除法器输入输出,数值结果对照正确,说明用VCS仿真Quartus中多IP核的过程正确。

2906

2906

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?