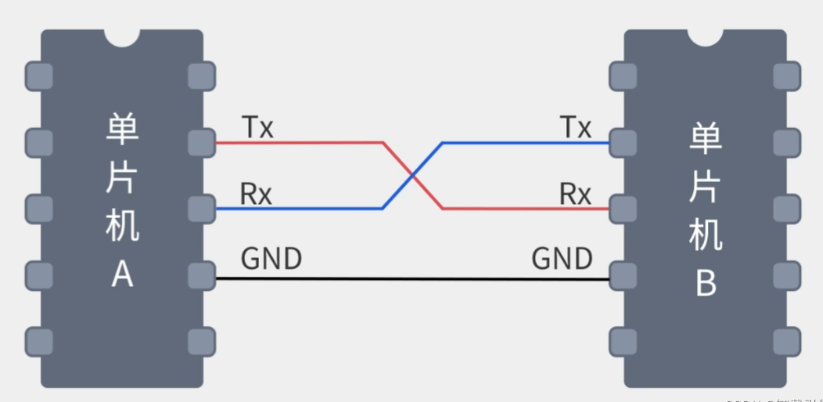

串口 UART 全双工异步串行

高电平(逻辑“1”或HIGH):典型值为+2.4V至+5V(对于标准5V电源供电的TTL)代表有效信号。

低电平(逻辑“0”或LOW):典型值接近于地电压(0V至+0.4V),代表无效信号。

对于TX引脚,GPIO_Mode字段设置为GPIO_Mode_AF_PP(复用推挽输出)

对于RX引脚,GPIO_Mode字段设置为GPIO_Mode_IN_FLOATING(浮空输入)

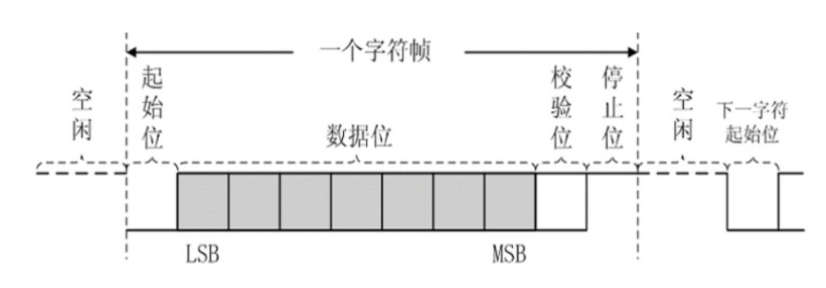

起始位、数据位、奇偶校验位和停止位

空闲:线路上为高电平,即逻辑值为1。

起始位:逻辑值为0,表示字符帧的开始。

数据 :先发低位再发高位。

校验位:奇偶校验。

停止位:高电平代表一个字符帧结束。

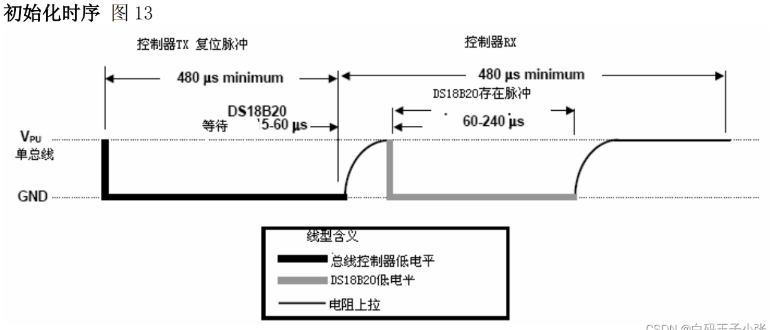

单总线协议

1、初始化(复位脉冲 + 存在脉冲)

复位序列:复位脉冲和存在脉冲

在初始化序列期间,总线控制器拉低总线并保持 480us 以发出(TX)一个复位脉冲,然后释放总线,进入接收状态(RX)。单总线由 5K 上拉电阻拉到高电平。当DS18B20 探测到 I/O 引脚上的上升沿后,等待 15-60us,然后发出一个由 60-240us低电平信号构成的存在脉冲。

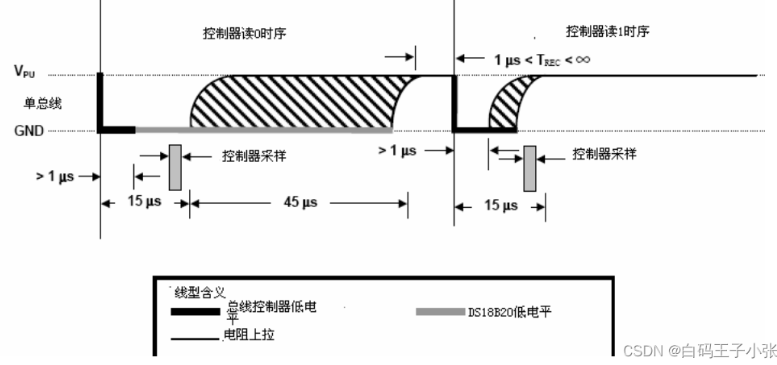

2、写时序

写时序分为写 1 时序和写 0 时序,总线控制器通过写 1 时序写逻辑 1 到

DS18B20,写 0 时序写逻辑 0 到 DS18B20。所有写时序必须最少持续 60us,包括两个写周期之间至少 1us 的恢复时间。当总线控制器把数据线从逻辑高电平拉到低电平的时候,写时序开始,如下图所示:

总线控制器要生产一个写时序,必须把数据线拉到低电平然后释放,在写时序开始后的 15us 释放总线。当总线被释放的时候,5K 的上拉电阻将拉高总线。总控制器要生成一个写 0 时序,必须把数据线拉到低电平并持续保持(至少 60us)。总线控制器初始化写时序后,DS18B20 在一个 15us 到 60us 的窗口内对 I/O 线采样。线上是高电平,就是写 1。如果线上是低电平,就是写 0。

3、读时序

总线控制器发起读时序时,DS18B20 仅被用来传输数据给控制器。因此,总线控制器在发出读暂存器指令[BEh]或读电源模式指令[B4H]后必须立刻开始读时序,DS18B20可以提供请求信息。除此之外,总线控制器在发出发送温度转换指令[44h]或召回 EEPROM 指令[B8h]之后读时序。

所有读时序必须最少 60us,包括两个读周期间至少 1us 的恢复时间。当总线控制器把数据线从高电平拉到低电平时,读时序开始,数据线必须至少保持 1us,然后总线被释放。在总线控制器发出读时序后,DS18B20 通过拉高或拉低总线上来传输 1 或 0。当传输逻辑 0 结束后,总线将被释放,通过上拉电阻回到上升沿状态。从 DS18B20 输出的数据在读时序的下降沿出现后 15us 内有效。因此,总线控制器在读时序开始后必须停止把 I/O 脚驱动为低电平 15us,以读取I/O 脚状态。

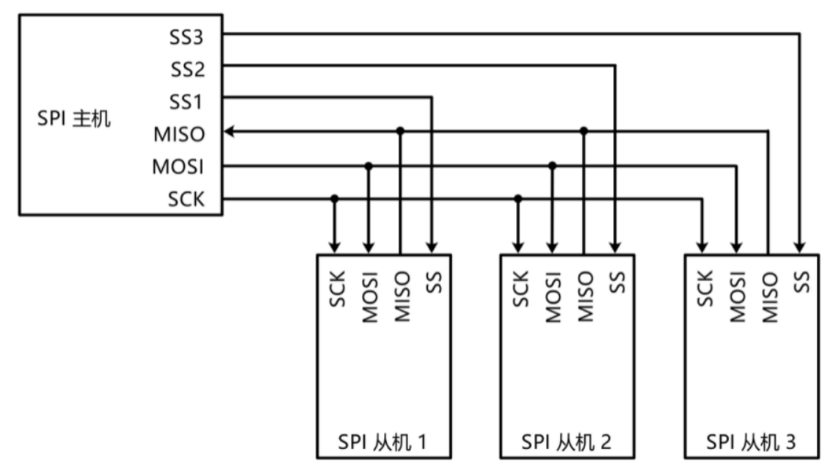

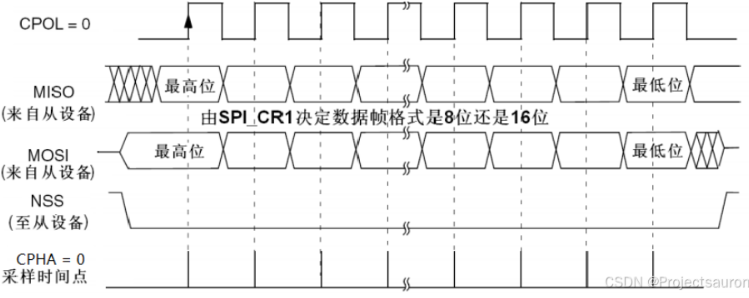

SPI 全双工同步 高位先行

MISO(Master In / Slave Out)主设备数据输入,从设备数据输出。

MOSI(Master Out / Slave In)主设备数据输出,从设备数据输入。

SCLK(Serial Clock)时钟信号,由主设备产生。

CS(Chip Select)从设备片选信号,由主设备产生

起始条件:SS 从高电平切换到低电平

终止条件:SS 从低电平切换到高电平

因此,在从机的整个选中状态中,SS 要始终保持为低电平。

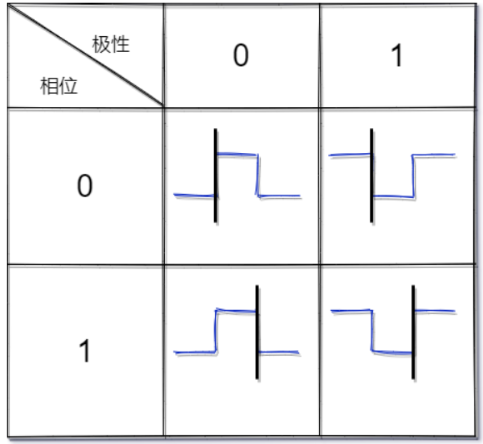

CPOL(Clock Polarity,时钟极性)

CPHA(Clock Phase,时钟相位)

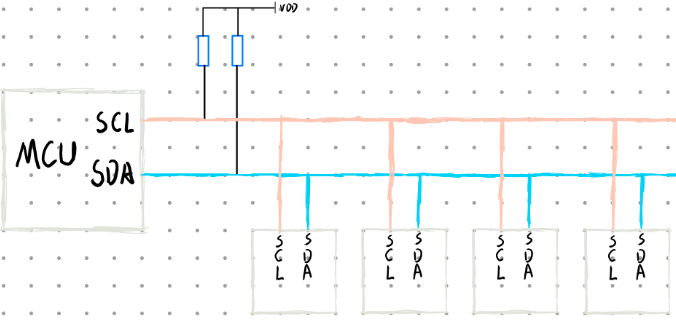

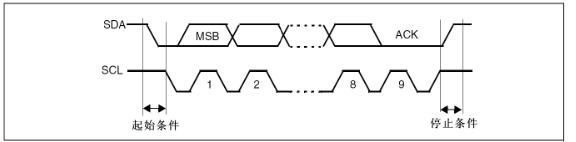

IIC 读写操作都是一字节大小,从高到低收发数据

时钟信号SCL为高电平期间,数据线SDA上的数据必须保持稳定,只有在时钟线SCL上的信号为低电平期间,数据线SDA上的高电平或低电平状态才允许变化,因为当SCL是高电平时,数据线SDA的变化被规定为控制命令(START或STOP,也就是起始信号和停止信号)

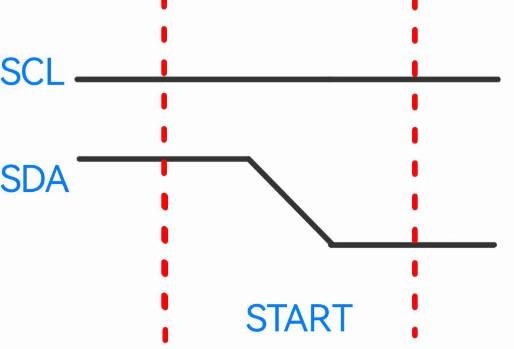

空闲状态(IDLE)钟信号SCL和数据信号SDL均为高电平起始信号(START) 时钟信号SCL继续保持高电平,数据信号SDL出现由高电平转换为低电平的下降沿,

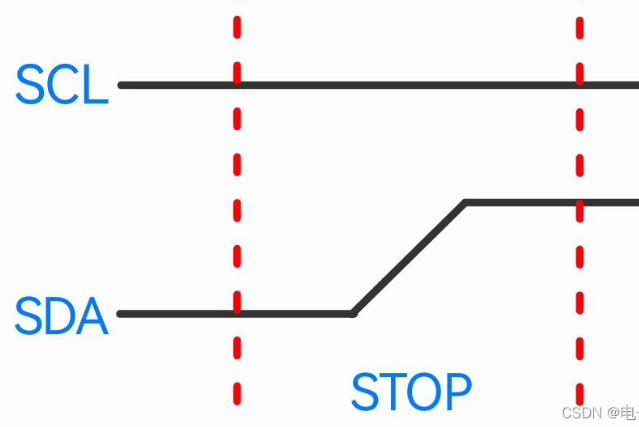

停止信号(STOP)SCL保持高电平,SDA由低电平跳变到高电平

应答(ACK)与非应答(NACK)

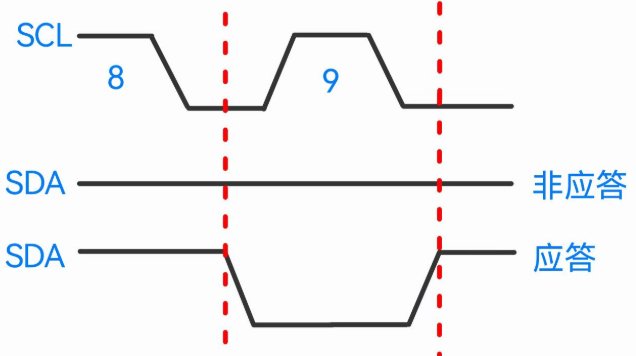

发送端每发送一个字节(8位)数据,在第9个时钟周期释放数据线去接收对方的应答

在第9个时钟周期:

当SDA是低电平为有效应答(ACK),表示对方接收成功;

当SDA是高电平为无效应答(NACK),表示对方没有接收成功。

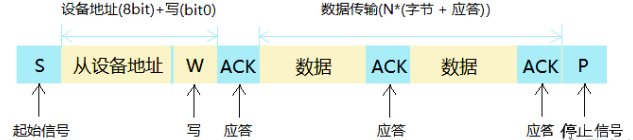

- 主设备发送起始(START)信号

- 主设备发送设备地址到从设备

- 等待从设备响应(ACK)

- 主设备发送数据到从设备,一般发送的每个字节数据后会跟着等待接收来自从设备的响应(ACK)

- 数据发送完毕,主设备发送停止(STOP)信号终止传输

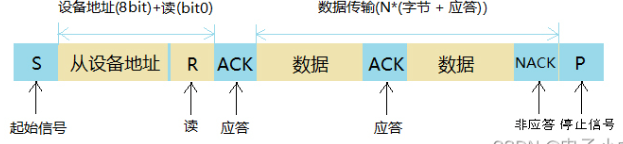

- 设备发送起始(START)信号

- 主设备发送设备地址到从设备

- 等待从设备响应(ACK)

- 主设备接收来自从设备的数据,一般接收的每个字节数据后会跟着向从设备发送一个响应(ACK)

- 一般接收到最后一个数据后会发送一个无效响应(NACK),然后主设备发送停止(STOP)信号终止传输

578

578

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?