在实际开始设计之前,首先要解决的问题是如何实现双速率数据接口和单速率数据接口的转换。

一、原理

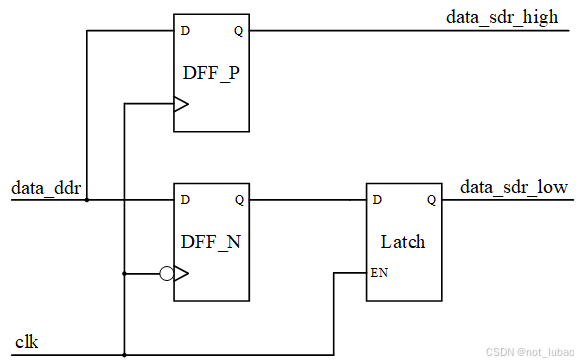

1. 双转单

如上图所示,在clk的下降沿时,DFF_N寄存数据 ;在clk的上升沿时,DFF_P寄存数据 ;clk为低电平时Latch的输出Q和输入D断开,输出依旧保持之前值不变;clk为高电平时Latch的Q和D直通,D输入即为DFF_N的值。

这样即可实现在上升和下降沿分别对data_ddr采样,并在上升沿输出采到的值,实现双速率到单速率的转换。

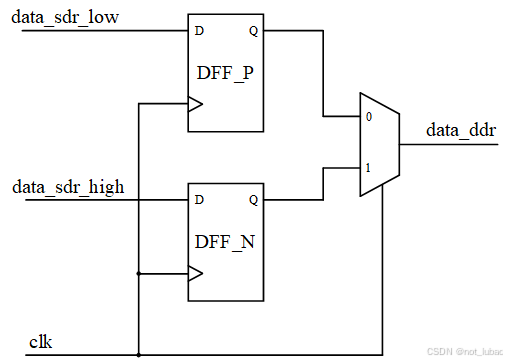

2. 单转双

data_sdr_high和data_sdr_low通过寄存器后接到一个二选一多路器,该二选一多路器的输出选择由clk控制,当clk为高电平,输出data_sdr_high;当clk为低电平,输出data_sdr_low。

显然,如果希望一个模块同时拥有以上两个功能,就需要再添加一个信号以控制inout接口的状态转换(三态门),在此不再赘述。

二、实现

由于双速率数据接口大多用于高速接口,所以时钟和数据一点小偏差也是十分关键的,所以单双速率数据接口的转换不能根据原理使用代码自己编写实现,需要直接使用包装好的IP核。在Quartus II软件中,可以调用altddio IP核;而在Vivado中,通常采用原语IDDR、ODDR、IDDRE1和ODDRE1等实现。不同器件的原语也不同,这里主要以7 Series FPGAs为例,参考

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

684

684

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?