背景

再认识它之前,先来了解了解它的几个预备知识

指令集架构(Instruction Set Architecture,ISA)

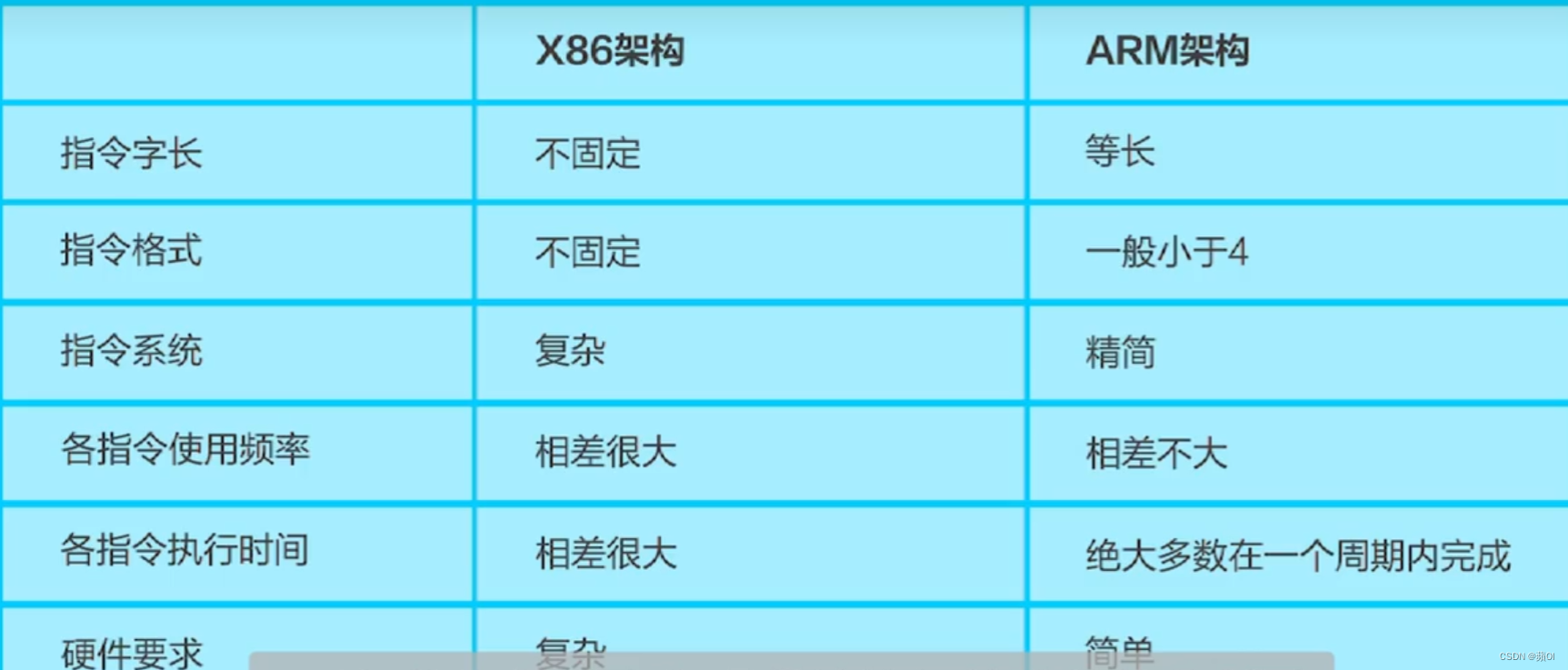

也称指令集、指令集体系,是计算机体系结构中与程序设计有关的部分。指令集架构是计算机体系结构中的重要组成部分,它定义了计算机如何执行指令、访问数据、控制存储器以及与外部设备交互的方式。不同的指令集架构有不同的特点和适用场景。国内外的主流指令集主要包括X86、ARM

X86架构

它采用的是一种基于复杂指令集(CISC);是计算机领域中最为广泛应用的指令集架构之一,它具有强大的处理能力和高度的可编程性,广泛应用于各个领域。主要用于个人电脑、服务器和其他类型的计算机系统,逐渐演变为现代计算机体系结构的基础。

厂商:inter和AMD是主要的X86架构授权厂商,他们通过授权和许可,来让其他公司和组织使用他们的X86架构。

开发商:英特尔(Intel)、AMD、兆芯(Zhaoxin)、海光(Hygon)

特点:性能高、速度快、兼容性好,复杂指令集,可编程性强,处理能力强

- 复杂指令集:X86架构的指令集,相对于RISC精简指令集架构而言更为复杂,这意味着X86架构CPU可以执行更多的操作,但同时也会带来一些性能上的损失

- 可编程性强:X86架构具有高度的可编程性,可以通过编写汇编语言或高级编程语言,来编写程序

- 处理能力强:X86架构具有较强的处理能力,可以支持高频率多核的CPU

- 向下兼容:X86架构具有向下兼容的特点,极较新版本的CPU可以运行较旧版本的软件

ARM架构

它采用的是一种精简指令集(RISC):广泛应用于移动设备,嵌入式系统和其他低功耗设备,在移动通信领域,arm指令集已成为主流,其垄断了95%以上的移动市场。主要依托于它低功耗、高效率,设计上更偏重节能。

厂商:ARM,将其架构授权给其他公司,以便他们可以设计制造和销售,一来是减低本身研发风险和资金投入;二来可通过IP和授权标准和授权和定制和授权来赚取收益

开发商:三星Exynos处理器、高通的骁龙处理器(Qualcomm Snapdragon)或苹果(Apple) A11芯片等等...

特点:高效率、低功耗、节能

- 精简指令集:arm架构采用精简指令集,每个指令都非常简单且执行速度快,因此具有高效率和低功耗的特点

- 抽象层次多:arm架构在硬件和软件之间引入了多个抽象层次,使得软件开发变得更加灵活,且具有更高的可疑之性

- 强大的架构扩展:arm架构有许多的扩展,如M2neon和trust zone等,可以满足不同应用的需求

- 多种不同的实现:arm架构的实现具有很高的灵活性,不仅可以在不同的芯片制造商之间切换,还可以选择不同的封装形式,不同的和数量和频率等

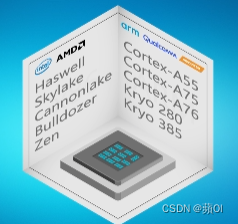

微架构:整体架构下的分支

x86微架构:Intel的NetBurst微架构、Pentium 4的微架构、Core微架构、Nehalem微架构、Sandy Bridge微架构、Haswell微架构等

ARM微架构:Cortex-A53、Cortex-A57、Cortex-A72、Cortex-A73等

其他指令集

目前 、国内外的主流指令集还有:RISC-V、MIPS、中科龙芯

RISC-V

是基于RISC精简指令集的设计思想而建立的,设计原则是简单、模块化和可扩展,主要运用在服务器、嵌入式系统、物联网、人工智能等领域、目前已经成为开源社区中备受关注的技术之一、在未来几年中RISC-V将会在各个领域中得到更广泛的应用

厂商:RISC-V国际基金会

开发商:博世、高通、英飞凌、Nordic半导体以及恩智浦等

特点:

- 简单性指令集架构简单易于理解和实现

- 可定制性可以根据应用需求进行扩展和定制

- 兼容性可以与其他CPU架构和系统进行交互

- 开放性指令集架构开放没有专利或版权限制任何人都可以使用

- 高性能提供高性能和低功耗的计算能力而RISC-V指令集架构的开放性和可定制性使得它在各种应用领域都具有广泛的应用前景

MIPS:

也是一种基于RISC精简指令集的处理器架构,一种固定长度的定期编码指令集,并采用导入存储数据模型,经改进,这种架构可持高级语言的优化执行,如今基于该架构的芯片广泛被使用在许多电子产品、网络设备、个人娱乐装置与商业装置上

厂商:MIPS科技公司

开发商:龙芯中科、北京君正

LoongArch:

技术先进,兼容生态运营机构龙芯。最早是采用MIPS指令集,但从3A50开始,自研了learn arch指令集,就全面装换成自研的道路。从顶层架构到指令功能和奥比标准等,全部自主设计,无需国外授权,并且龙架构还得到了上百个与指令系统相关的国际软件开源社区的支持

同性麒麟、欧拉、龙芯、鸿蒙等操作系统的支持

最新的龙芯3A6000、性能可对标7NM的AMD的CIN2,相当于英特尔第十代酷睿的水平

虽然生态环境艰难,但不管怎么样自研指令集的国产CPU真正实现了独立自主,不再被任何指令集卡脖子,代表了我国自主桌面CPU设计领域的最新里程碑成果,值得我们去长期期待和支持。

厂商:龙芯中科

开发商:龙芯中科

以上背景 就介绍到这

由于STM32采用的是ARM架构的,我们再来具体聊一聊吧

ARM

含义

它有两个含义,一家公司和一项技术

一家公司:一家全球领先的半导体知识产权(IP)提供商,设计了大量高性价比、耗能低的RISC处理器、相关技术及软件。

一项技术:一项具有性能高、成本低和能耗省的特点的技术。是一类微型处理器的统称,其微型处理器包含多个系列,每个系列各自有不同的特点和应用领域。它采用的是RISC指令集,在智能机、平板电脑、嵌入控制、多媒体数字等处理器领域拥有主导地位。

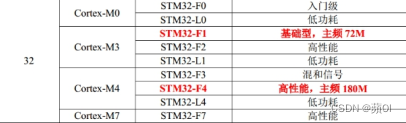

ARM 是英国的芯片设计公司, 其最成功的莫过于 32 位嵌入式 CPU 核--ARM系列, 最常用的是 ARM7 和 ARM9,为了对付 8 位机市场, 推出了一系列 Cortex-M 核,STM32 就是将 Cortex-M 作为内核, 通过一些外设等组合封装在一起就成了如今火爆的 32 位嵌入式处理器STM32F103, 也就是 M3 内核,Cortex-M3 采用ARMv7-M 架构。

分类

ARMv7 架构定义了三大分工明确的系列:

“A” 系列: 面向尖端的基于虚拟内存的操作系统和用户应用

“R” 系列: 针对实时系统;

“M” 系列: 针对微控制器

STM32

功能:能做些啥

STM32 的应用取决于其内部资源。

USART: ESP8266 WIFI 模块、 GSM 模块、 蓝牙模块、 GPS 模块、 指纹识别模块、 IOT 模块、 串口屏等。

IIC: EEPROM、 MPU6050 陀螺仪、 0.96 寸 OLED 屏、 电容屏等。

SPI: 串行 FLASH、 以太网 W5500、 VS1003/1053 音频模块、 SPI 接口的 OLED屏、 电阻屏等。

AD/DA: 光敏传感器模块、 烟雾传感器模块、 可燃气体传感器模块、 简易示波器等

- 无人机:STM32单片机可以通过控制无人机的飞行路径、速度、高度等参数,实现无人机的各种飞行任务。

- 智能家居:STM32单片机可以通过控制家居电器的开关、温度、湿度等参数,实现智能家居的各种智能化控制。

- 汽车电子:STM32单片机可以通过控制汽车的油门、刹车、灯光等参数,实现汽车的各种安全、舒适的驾驶功能。

- 医疗设备:STM32单片机可以通过控制医疗设备的各种参数,如血压、血糖、心电图等,实现医疗设备的各种智能化控制。

- 智能穿戴:STM32单片机可以通过控制智能手表、智能手环等设备的各种参数,实现各种健康监测、运动计步等功能。

- 智能门锁:STM32单片机可以通过控制门锁的开关、密码等参数,实现智能门锁的各种安全、便捷的控制功能。

- 工业控制:STM32单片机可以通过控制工业设备的各种参数,如温度、压力、液位等,实现工业设备的各种智能化控制。

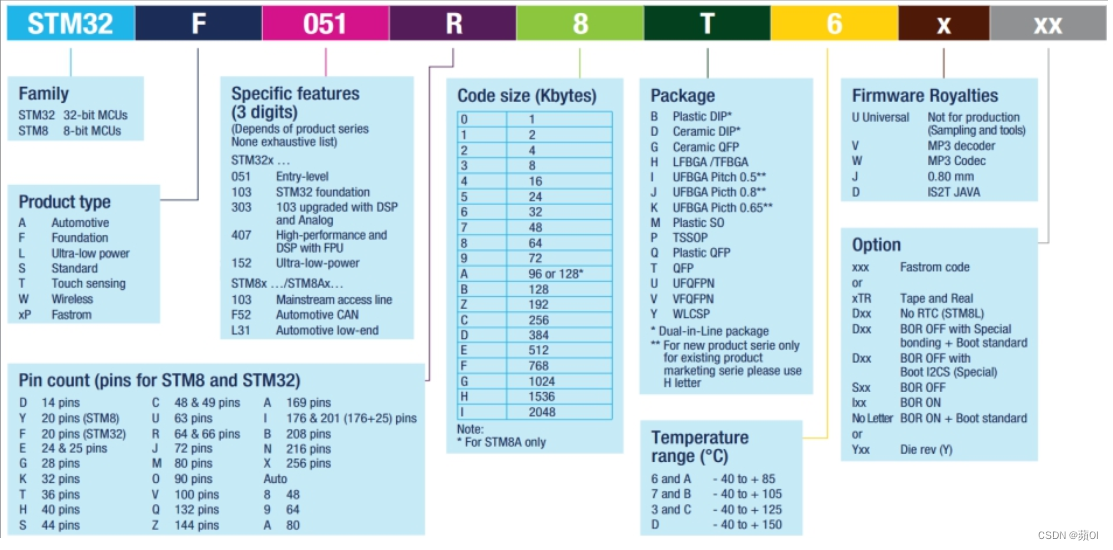

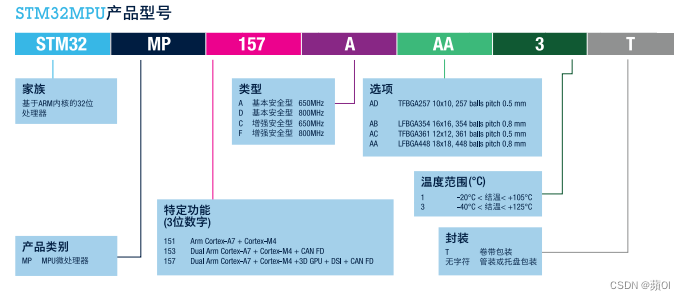

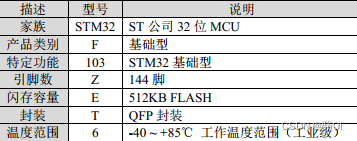

命名:名字含义

ST: 意法半导体, 是一个公司的名字。

M: Microelectronics 的缩写, 表示微控制器, 要注意微控制器和微处理器

的区别

32: 32bit 的意思, 表示这是一个 32bit 的微控制器

STM32 仅 M3 内核就拥有 F100、 F101、 F102、 F103、 F105、 F107、 F207、F217 等 8 个系列上百种型号,具有 QFN、 LQFP、 BGA 等封装可供选择。还有STM32L 和 STM32W 等超低功耗和无线应用型的 M3 芯片和STM32F4/F7/H7 等更高性能的芯片

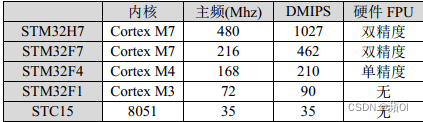

最强 H7 的 DMIPS 性能约为 STC15 的 30 倍,即便是 STM32F103 也大概有 STC15性能的 3倍,由此可见 STM32 的强大,而且最便宜的 STM32F103,价格大概在 5 块多人民币,和 STC15 系列的价格差不多。8 位机的价格, 32 位机的性能,是 STM32 最大的优势。

DMIPS:(一种衡量嵌入式处理器性能的指标,它以Dhrystone程序为测量标准,表示处理器每秒能够执行的百万条指令)

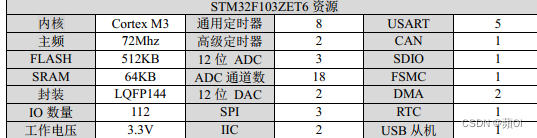

内部资源:以F103ZET6为例

内核:32位,高性能ARM Cortex - M3处理器

时钟:可达72M,可超频

IO口:144个引脚,112个IO,大部分 IO 口都可承受5V(模拟通道除外), 支持调试: SWD 和 JTAG, SWD 只要 2 根数据线

存储器容量: 512K FLASH, 64K SRAM。512K FLASH = 512 * 1024字节,即524288字节,而64K SRAM = 64 * 1024字节,即65536字节。

时钟系统:

- 4-16M的外部高速晶振

- 32.768K外部低速晶振 --> rtc时钟源

- 8M内部高速RC振荡器

- 40K内部低速RC振荡器 --> 看门狗时钟

内部锁相环(PLL,倍频),一般系统时钟都是外部或者内部高速,时钟经过 PLL 倍频后得到

低功耗:有睡眠、停止、待机三种模式,可用电池为 RTC 和备份寄存器供电

AD:3个12位AD,转换范围(0-3.6V),内部通道可以用于内部温度测量,

DA:2 个 12 位 DA

DMA:12 个 DMA 通道(7 通道 DMA1, 5 通道 DMA2) , 支持外设: 定时器,

ADC,DAC, SDIO,I2S,SPI,I2C,和 USART

定时器:4 个通用定时器、2 个基本定时器、2 个高级定时器、1 个系统定时器、2 个看门狗定时器

通信接口:2 个 I2C 接口、5 个串口、3 个 SPI 接口、1 个 CAN2.0、1 个 USB FS、1 个 SDIO

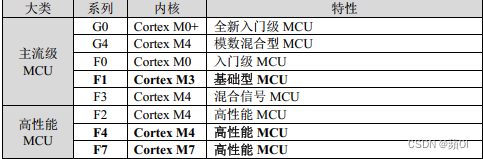

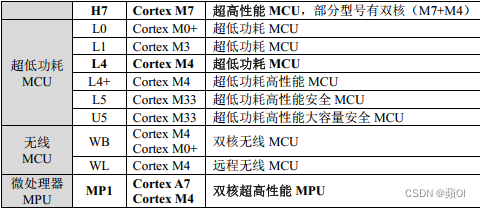

对于做项目开发,需要用到多少个内设资源的MCU,都可以参考ST MCU选型手册来选择,STM32 从 2007 年推出至今,已经有 18 个系列,超过 1000 个型号,目前共有5个大类,18个系列:

(其中MPU是可以跑Linux的)

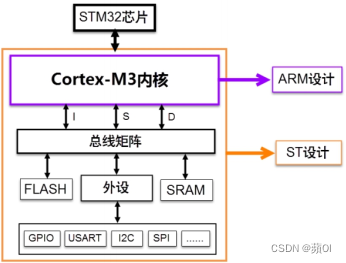

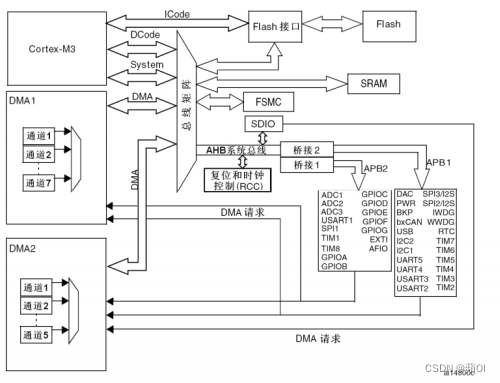

系统结构

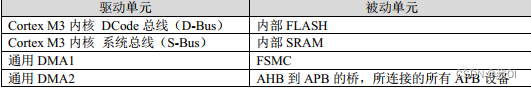

根据以上的系统结构简图,我们来分析分析哈,主要记得八个大字 -- “四个驱动,四个被动”

首先,你要明白什么是总线? 它就是计算机各种功能部件之间传送信息的公共通信干线。

然后,再来认识认识几个图上的总线:

ICode 总线:主要用于读取指令,几乎每时每刻都需要被使用。由图可看出,它比较特殊,没有走总线矩阵这条路,而是直接连Flash接口上跟Flash传送信息,这样设计,可以提升flash程序里的响应速度。

DCode 总线:主要用于数据的读取和传输。该总线通过总线矩阵与闪存存储器(SRAM)的数据接口相连接

System 总线:系统总线(也称外设总线)到总线矩阵, 总线矩阵协调着内核和 DMA 间的访问

DMA总线:通过总线矩阵与AHB主控接口相连,AHB又桥接APB1和APB2,分别相连的片内外设资源。两个 AHB全速为72Mhz, APB1 操作速度限于 36MHz, APB2 操作于全速(最高 72MHz)

在AHP系统总线上,也会看到SD卡接口(SDIO),复位和时钟控制(RCC)也是直接相连的,以满足其高速的要求

Flash:内部闪存存储器,用于代码/数据存储,CPU通过ICode总线经FLASH接口访问内FLASH, FLASH最高访问速度是24Mhz,因此以72M速度访问时,需要插入2个时钟周期延迟。

SRAM:内部随机存储器,用于数据存储,直接挂载在总线矩阵上面, CPU通过DCode总线实现0等待延时访问SRAM,最快总线频率可达72Mhz,从而保证高效高速的访问内存

FSMC:可变静态存储控制器,一种新型的存储器扩展技术。它可以根据系统的应用需要,方便地进行不同类型大容量静态存储器的扩展。

八个大字 -- “四个驱动,四个被动”

四个驱动:DCode 总线、System 总线、DMA1总线、DMA2总线

四个被动:Flash、SRAM、FSMC、AHP桥接到APB1/APB2上的外设

四个驱动和四个被动。分别DCode 总线 控制着 SRAM、System 总线 控制着 FSMC、DMA1总线和DMA2总线 控制着 AHP桥接到APB1/APB2上的外设

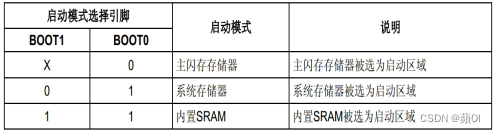

启动配置

共有三种启动模式:可分别通过BOOT1和BOOT0来选择

(0为低电平,1为高电平)

当BOOT0为0,启动模式为主闪存存储器,即程序是从Flash执行的。

当BOOT0为1,BOOT1为0,启动模式为系统存储器,即程序从串口下载执行

当BOOT0为1,BOOT1为1,启动模式为内置SRAM,不推荐使用

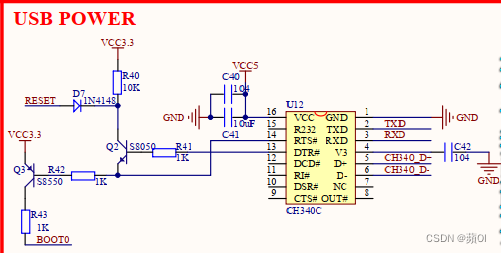

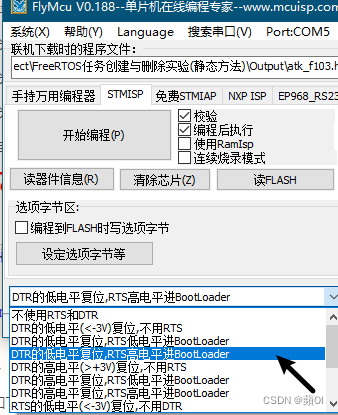

一键下载电路

当使用串口下载程序时,会使用到这个电路。省了来回插拔两回跳线帽,即操作DTR复位时为低电平,RTS为高电平。当RTS为低电平,三极管S8550导通,使得BOOT0为高电平。复位时,DTR为低电平,三极管S8050截止,则集电极为低电平,Q3不导通,为低电平,程序就冲flash执行(通过烧录软件配置)

存储器

介绍

存储器映射:存储器本身不具有地址信息, 它的地址是由芯片厂商或用户分配, 给存储器

分配地址的过程称为存储器映射, 如果再分配一个地址就叫重映射

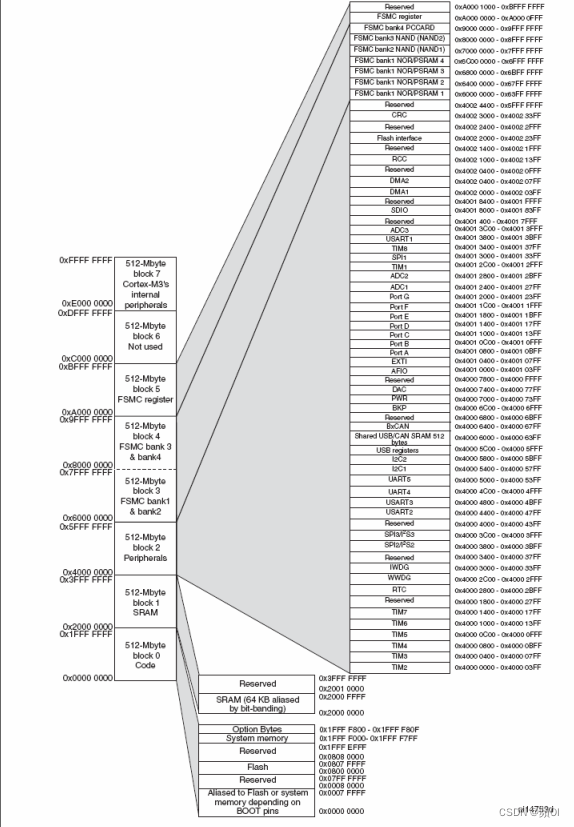

STM32存储器映射图

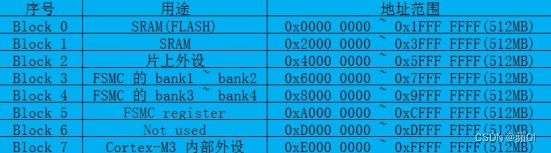

存储器上总共4G的储存地址被平等的分成了八块,没块都是512MB,虽然空间是如此的大,但STM32实际分配上远远过剩,要知道一点每块区域容量占用越大, 芯片成本就越高。

八块空间的功能划分

其中,Block0、 Block1 和 Block2是至关重要的,也是STM32外设资源的核心区块了

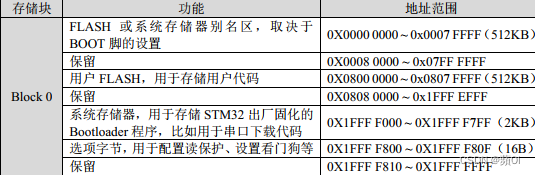

Block0:

STM32F103 系列芯片内部 FLASH 最大是 512KB,这个大小也足够完成正常使用了。

0x0000 0000-0x0007 FFFF: 取决于 BOOT 引脚, 为 FLASH、 系统存储器、SRAM 的别名。

0x0008 0000-0x07FF FFFF: 预留

0x0800 0000-0x0807 FFFF: 片内 FLASH, 我们编写的程序就放在这一区域(512KB)

0x0808 0000-0x1FFF EFFF: 预留

0x1FFF F000-0x1FFF F7FF: 系统存储器, 里面存放的是 ST 出厂时烧写好的isp 自举程序, 用户无法改动。 使用串口下载的时候需要用到这部分程序。

0x1FFF F800-0x1FFF F80F: 选项字节, 用于配置读写保护、 BOR 级别、 软件/硬件看门狗以及器件处于待机或停止模式下的复位。 当芯片不小心被锁住之后, 我们可以从 RAM 里面启动来修改这部分相应的寄存器位。

0x1FFF F810-0x1FFF FFFF: 预留

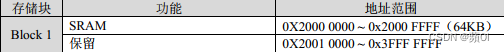

Block1 :

用于设计片内的SRAM, 使用的 STM32F103ZET6 的 SRAM是64KB。

0x2000 0000-0x2000 FFFF: SRAM, 容量为 64KB。

0x2001 0000-0x3FFF FFFF: 预留。

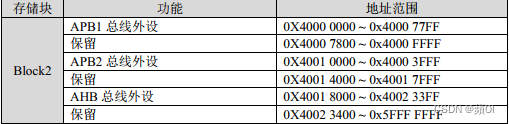

Block2

用于设计片内外设, 根据外设总线速度的不同, Block2 被划分为 AHB和 APB 两部分, APB 又被分成 APB1 和 APB2 总线。 这些都可以在存储器映射图中看到, 我们按地址由低到高顺序依次介绍。

0x4000 0000-0x4000 77FF: APB1 总线外设。

0x4000 7800-0x4000 FFFF: 预留。

0x4001 0000-0x4001 3FFF: APB2 总线外设。

0x4001 4000-0x4001 7FFF: 预留。

0x4001 8000-0x4002 33FF: AHB 总线外设。

0x4002 4400-0x5FFF FFFF: 预留。

Block3/4/5 中还包含了 FSMC 扩展区域, 这 3 个块可用于扩展外部存储器,

比如 SRAM, NORFLASH 和 NANDFLASH 等

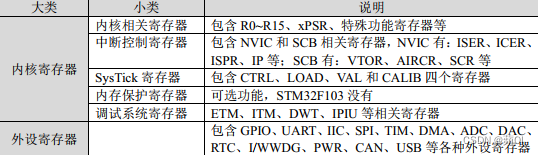

寄存器

介绍

即储存器的地址的新名字。是单片机内部一种特殊的内存,可以实现对单片机各个功能的控制,简单的来说可以把寄存器当成一些控制开关,控制包括内核及外设的各种状态。所以无论是 51单片机还是 STM32,都需要用寄存器来实现各种控制,以完成不同的功能。寄存器资源非常宝贵,一般都是一个位或者几个位控制一个功能,对于 STM32 来说,其寄存器是 32 位的,一个 32 位的寄存器,可能会有 32 个控制功能,相当于 32 个开关

内核寄存器:一般只需要注意中断控制寄存器和 SysTick 寄存器,其他基本用不到

外设寄存器:用到什么学习哪个

寄存器映射:打个比方,例如给储存器中的0x4001 0C10地址附一个新名字,叫作GPIOB_BSRR,这个赋予的过程就是寄存器映射。那么程序上该咋实现呢?

正常赋值:(*(unsigned int *))(0x4001 0C10) = 0xffff

映射:#define GPIOB_BSRR *(unsigned int *)(0x4001 0C10)

映射后赋值:GPIOB_BSRR = 0XFFFF

这要我们就完成了对GPIOB的 --> BSRR寄存器的赋值,全部赋值为1

但是我们还有一种更好的写法,可读性更高

映射后赋值:GPIOB -> BSRR = 0xffff

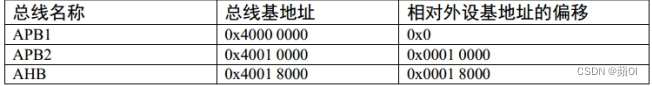

寄存器地址

具体某个寄存器地址,由三个参数决定:总线基地址(BUS_BASE_ADDR)、外设基于总线基地址的偏移量(PERIPH_OFFSET)、寄存器相对外设基地址的偏移量(REG_OFFSET)。可以表示为:寄存器地址 = BUS_BASE_ADDR + PERIPH_OFFSET + REG_OFFSET

总线基地址(BUS_BASE_ADDR)

STM32内部有三个总线(APB1、 APB2和AHB)

在存储器映射表上 ,APB1起始地址是0x4000 0000,这个地址就是基地址,同时也是APB2总线的起始地址是0x4001 0000,AHB总线的起始地址是0x4001 8000。其中相对外设基地址的偏移, 偏移量就是相对于外设基地址的偏移量

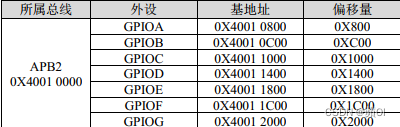

外设基于总线基地址的偏移量(PERIPH_OFFSET)

寄存器相对外设基地址的偏移量(REG_OFFSET)

若我们计算一个GPIOB_ODR的地址,则表示:

GPIOB_ODR地址 = APB2总线基地址 + GPIOB外设偏移量 + 寄存器偏移量

GPIOB_ODR 地址 = 0X4001 0000 + 0XC00 + 0X0C = 0X4001 0C0C

总结

该篇主要介绍了STM32的一些背景知识、ARM、STM32,为后续的编程编写打下基础。再学这方面的东西,理论原理最好要理明白,不然就算是知道程序是这样写,但还是因为缺乏原理而感到自己没掌握好。

最后,再共勉大家一句话 ,嵌入式领域如同浩瀚一般,怎可说的穷尽,唯有不积硅步,方可成江河;道阻且长,行则将至!

参考

STM32F103 正点原子精英开发指南

STM32F103 普中科技开发指南

CPU的x86架构和ARM架构有啥区别?指令集又是什么?_哔哩哔哩_bilibili

深度解读:X86、ARM、RISC-V、MIPS、LoongArch有什么区别?_哔哩哔哩_bilibili

本文介绍了STM32相关知识。先阐述指令集架构,如X86、ARM等特点与应用;接着说明ARM含义与分类;重点讲解STM32,包括功能、命名、内部资源、系统结构、启动配置等,还介绍了存储器和寄存器相关内容,为后续编程打下基础。

本文介绍了STM32相关知识。先阐述指令集架构,如X86、ARM等特点与应用;接着说明ARM含义与分类;重点讲解STM32,包括功能、命名、内部资源、系统结构、启动配置等,还介绍了存储器和寄存器相关内容,为后续编程打下基础。

731

731

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?