Verilog编程

门电路

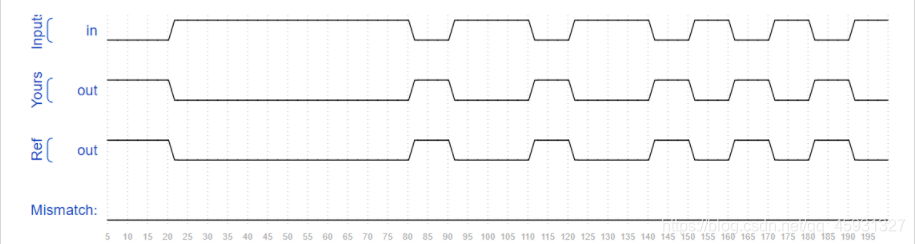

非门

代码内容:

module top_module( input in, output out );

assign out=~in;

endmodule

结果图形展示:

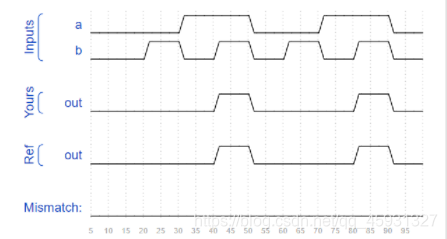

与门

代码内容:

module top_module(

input a,

input b,

output out );

assign out=a&b;

endmodule

结果图形展示:

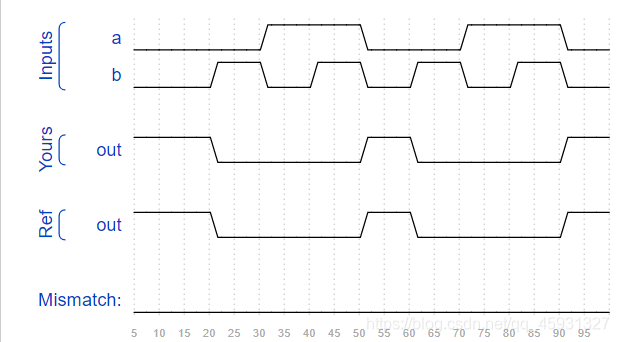

或非门

代码内容:

module top_module(

input a,

input b,

output out );

assign out=~(a|b);

endmodule

结果图形展示

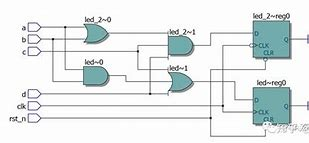

逻辑相关

组合逻辑:

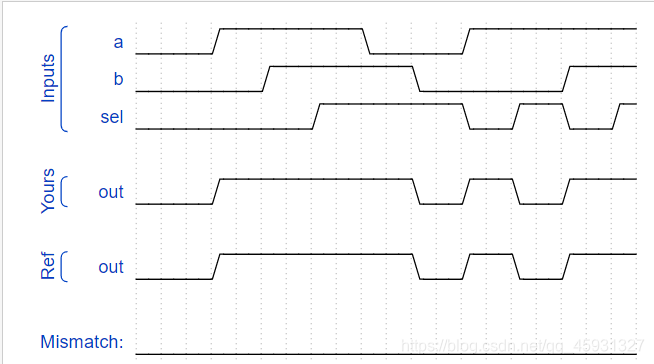

创建一个位宽,2比1的多路复用器。当sel=0时,请选择a。当sel=1时,选择b。

代码内容:

module top_module(

input a, b, sel,

output out );

assign out = (sel) ? b : a;

endmodule

结果图形展示

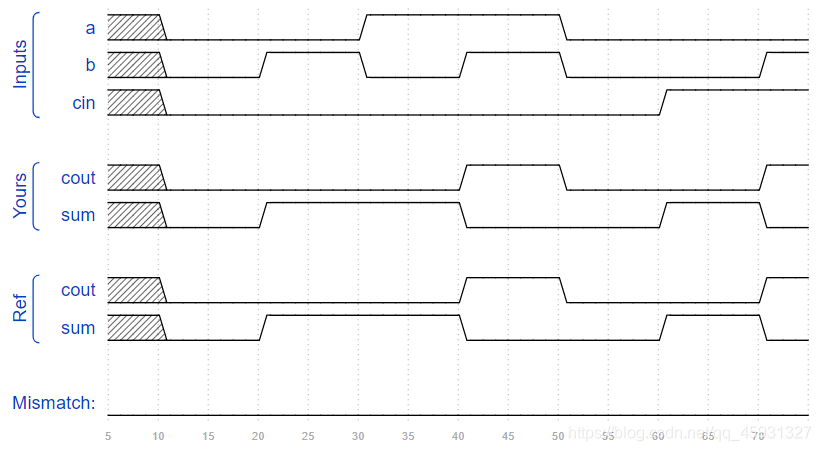

2.完整加法器

创建一个完整的加法器。一个完整的加法器添加三个位(包括随身行李),并产生一个总和和进行。

代码相关内容

module top_module(

input a, b, cin,

output cout, sum );

assign{cout,sum} = a + b + cin;

endmodule

结果图形展示

本文介绍了使用Verilog编程实现基本门电路,包括非门、与门和或非门,并展示了对应的逻辑结果。此外,还通过示例展示了如何设计组合逻辑,如2比1的多路复用器以及完整的加法器,提供了相关Verilog代码及图形化表示。

本文介绍了使用Verilog编程实现基本门电路,包括非门、与门和或非门,并展示了对应的逻辑结果。此外,还通过示例展示了如何设计组合逻辑,如2比1的多路复用器以及完整的加法器,提供了相关Verilog代码及图形化表示。

851

851

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?