一、稳态、亚稳态

时序分析的主要目的就是不产生亚稳态。而亚稳态是在建立时间和保持时间不满足的时候产生。

建立时间和保持时间不满足的情况:

- 时序不满足的时候

- 不同时钟域的信号

- 按键、外部芯片读写等

- 有可能在时钟上升沿变化的信号,均有可能出现亚稳态

减少亚稳态的方法

- 对于1bit信号,建议使用同步机制,即打两拍(甚至是三排)

- 对于多比特数据流,建议使用异步FIFO

- 对于少量,发送可控数据流,建议通过增加指示信号的方法

采样时间(Tsu)

例如dff。在采样沿之前,数据d要保持最小时间不发送改变,则这段时间称作dff器件所要求的最小建立时间

裕量

从在Tsu之前就稳定的时间点到Tsu之间的时间段,称为裕量。

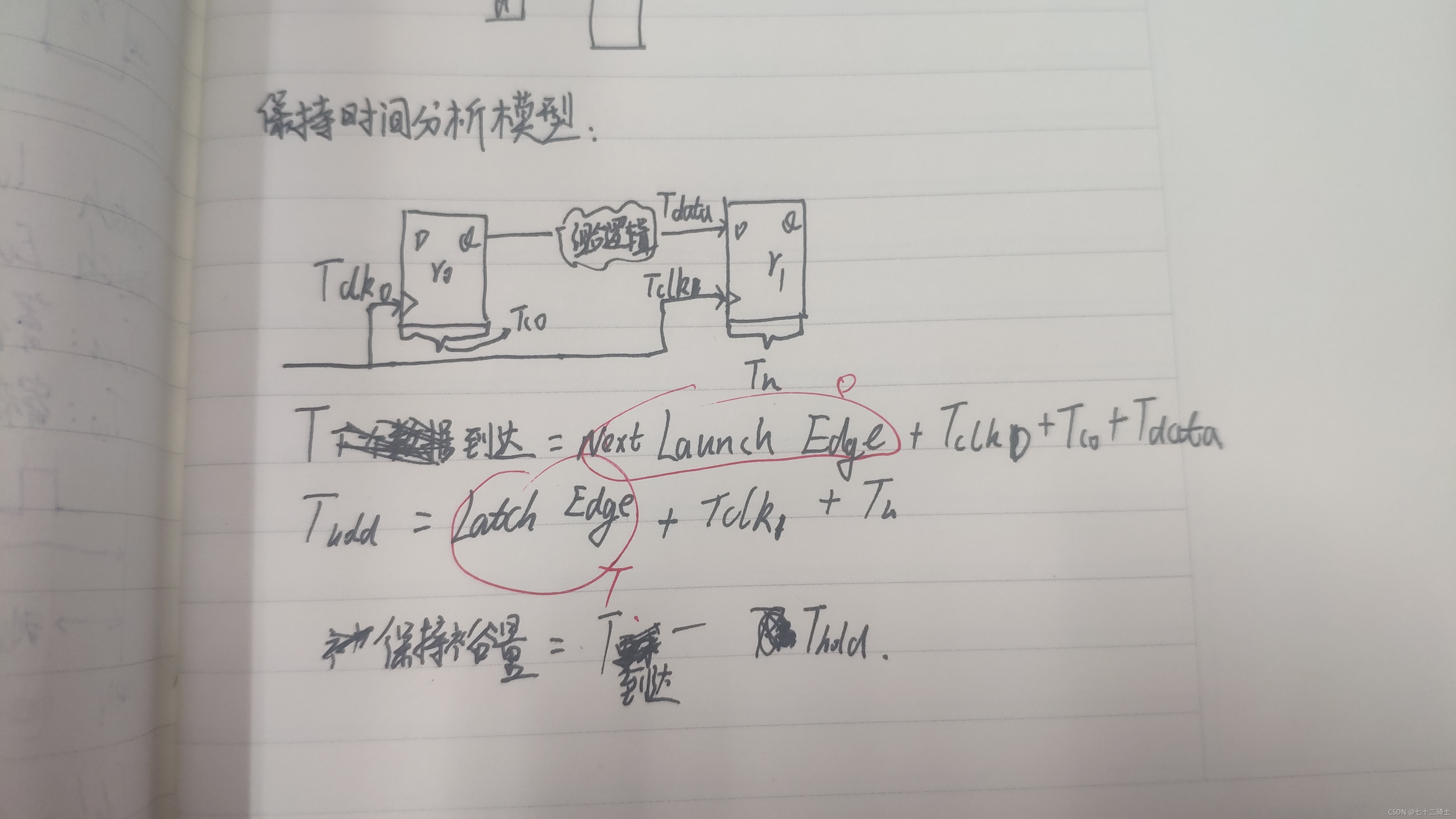

保持时间

在采样沿之后的一段时间称作为保持时间

二、学习笔记

8577

8577

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?