AHB(Advanced High Performance Bus)高级高性能总线,如同USB(Universal Serial Bus)一样,也是一种总线接口。

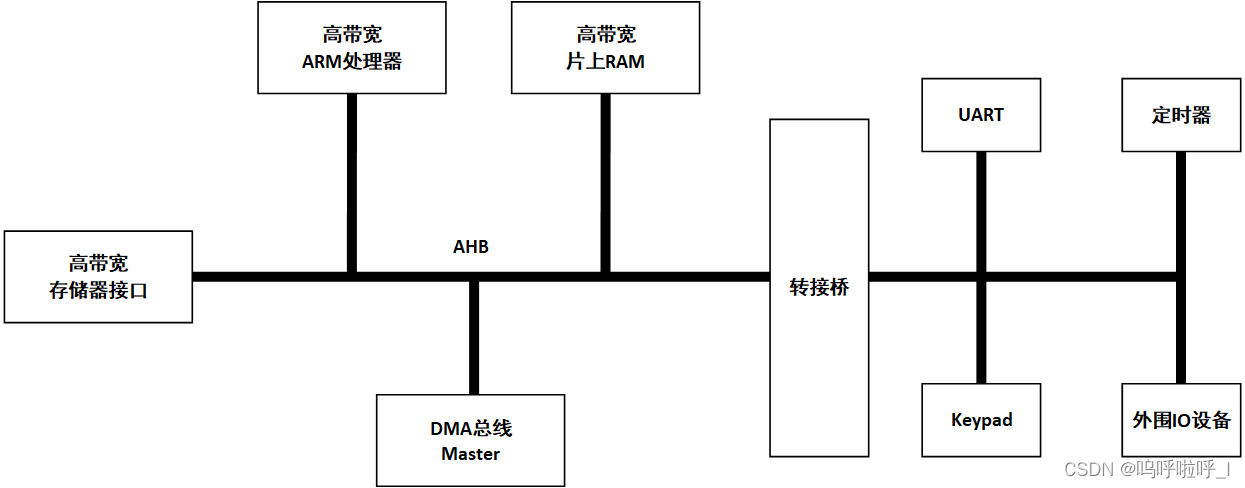

AHB主要用于高性能模块(如CPU、DMA和DSP等)之间的连接,作为SoC的片上系统总线,它包括以下特性:支持突发传输;支持分段传输;支持多个主控制器;可配置32位~128位总线宽度;支持字节、半字和字的传输。AHB 系统由主模块、从模块和基础结构(Infrastructure)3部分组成,整个AHB总线上的传输都由主模块发出,由从模块负责回应。基础结构则由仲裁器(arbiter)、主模块到从模块的多路器、从模块到主模块的多路器、译码器(decoder)等。

本文主要介绍AHB总线的简化本本AHB-lite总线,相对于AHB总线的区别是他只有一个主机,结构相对AHB总线要简单一些,在很多实际应用中实际上也只有一个Master,因此可以简化设计。

AHB总线的结构如下:

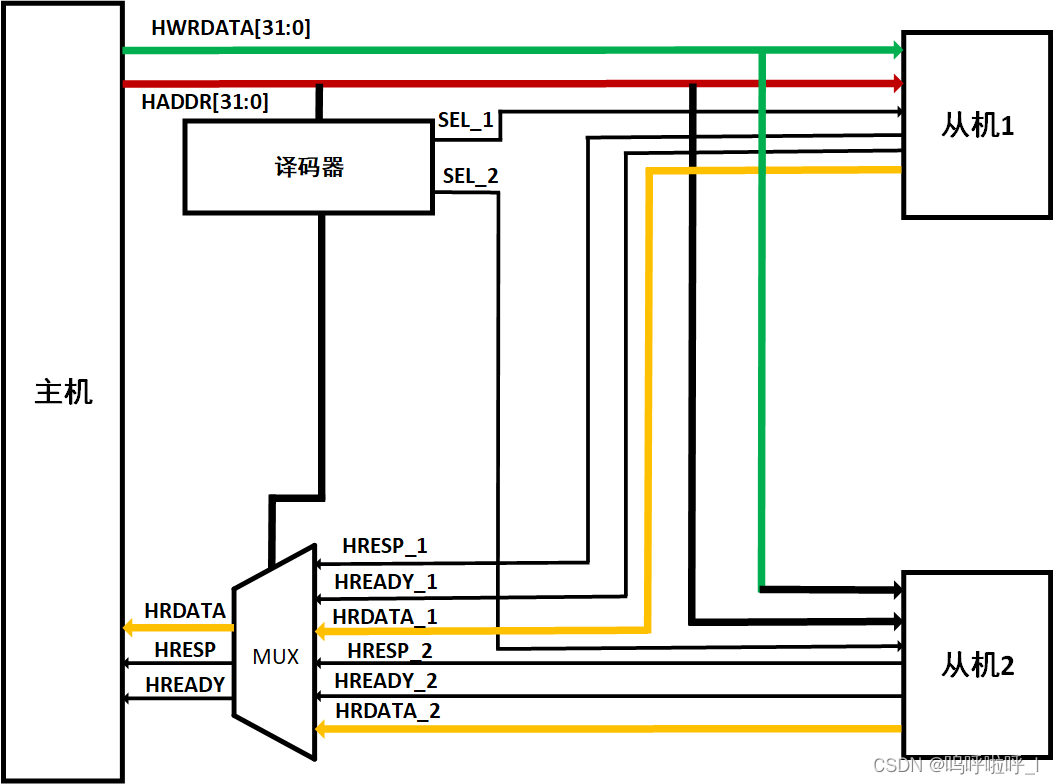

当主机需要对从机进行操作时,首先会根据地址进行译码,选择要操作的从机,将SEL信号给到对应的从机。对于从机来说,只有当输入的片选信号有效时,才能够进行后续的一些操作。

AHB总线的信号

| 信号名 | 位宽 | 方向 (对于CPU) | 说明 |

|---|---|---|---|

| clk | 1 | IN | 总线时钟 |

| rst_n | 1 | IN | 总线复位 |

| Trans | 2 | OUT | 传输方式控制 0:总线空闲 1:总线忙 2:只传输一个数据 3:连续传输数据 |

| Size | 3 | OUT | 数据大小控制 0:每次传输1字节 1:每次传输2字节 2:每次传输4字节 3:每次传输8字节 4:每次传输16字节 5:每次传输32字节 6:每次传输64字节 7:每次传输128字节 |

| write | 1 | OUT | 传输方向控制 0:CPU读取设备 1:CPU像设备写数据 |

| Port | 4 | OUT | 数据保护策略 bit0:表示传输数据类型。为0表示传输指令,为1表示传输数据; bit1:表示数据权限。为0时表示使用普通用户权限,为1时表示使用特权; bit2:是否允许数据被Buffer存储和延迟。为0时表示不允许,为1表示允许; bit3:是否允许数据被Cache缓存,为0时表示不允许,为1表示允许。 |

| Burst | 3 | OUT | Burst传输策略。 0:只传一个数据; 1:不定长的Burst传输; 2:4次连续传输; 3:8次连续传输; 4:16次连续传输; 5:4次连续WRAP传输; 6:8次连续WRAP传输; 7:16次连续WRAP传输; |

| addr | 32 | OUT | 读写操作地址 |

| wdata | 32 | OUT | 写数据 |

| rdata | 32 | IN | 读数据 |

| HRESP | 1 | IN | 设备状态反馈 0:传输成功; 1:传输中出现错误 |

| HREADY | 1 | IN | 全部设备状态反馈。 0:总线上有设备在忙,需等到空闲时才能进行传输; 1:所有设备空闲 |

| 闲 |

HSIZE指的是一次传输的数据宽度,而AHB读写数据线的宽度只有32位,因此其HSIZE只会出现0、1、2。

反馈信号HRESP 指的是设备是否处于错误状态,当传输中出现错误即HRESP为1时,表示设备无法满足CPU对其的读写要求,可能出现设备错误导致读写操作无法进行,亦或是设备的处理速度慢,读写存在一定的延时。

反馈信号HREADYOUT是设备内部有一定读写时延时来向CPU反馈的信号,当其 为1时表示总线上的所有设备都是空闲的,此时可以正常进行操作;当其为0时表示总线上有设备正在忙,无法写入数据,只有等待其为1时才能将上次要写入的数据写入设备。而HREADY信号是所有从机HREADYOUT信号相与后的结果

读写时序

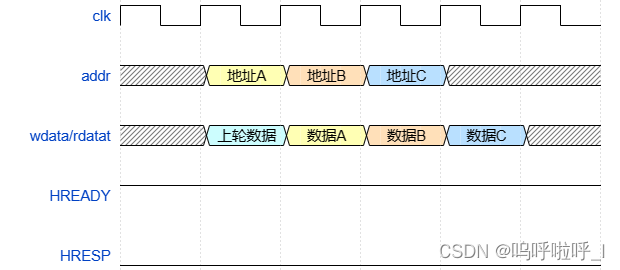

AHB总线的读写时序分为两拍完成,分别成为地址阶段和数据阶段,其时序图如下:

在地址阶段,将所有的控制信号都给出,以便使设备能够获取必要的传输信息,主要包括地址等;

在数据阶段,如果为写数据,则主机将会在地址出现的下一拍将数据信号送到总线上;如果为读数据,那么被读设备将会在地址的下一拍将读地址对应的数据传输到总线上。 数据的传输是按照流水线的方式,也就是说在本轮地址给出的下一拍,下一轮的地址便可紧接着给出,此时也正是第一轮的数据被给出的时候。

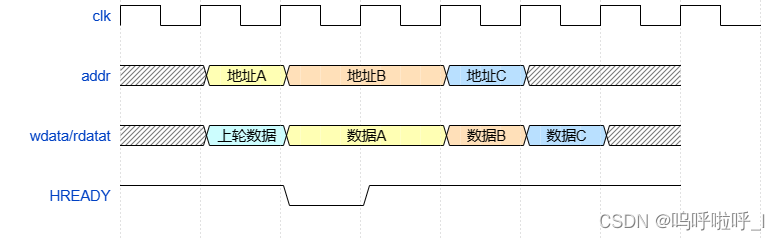

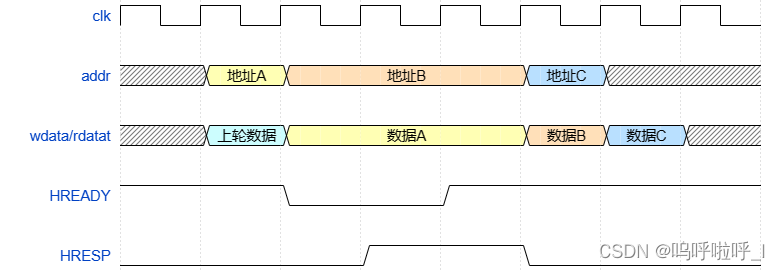

上面的时序图是在反馈信号HREADY信号一直为1的情况下,当某个设备反应速度较慢并不能在下一拍立刻完成读写时,从机会将自己的HREADYOUT信号拉低,对于主机的HREADY信号也将同时变低,本次读写将不能正常进行,直至这个从机的HREADYOUT信号拉高,才能进行正常写入,时序图如下:

当传输发生错误时,操作地址对应设备的HRESP信号会拉高,此时的传输时序图如下:

AHB总线的优点

优点:

- 高性能:AHB总线采用分段和流水线设计,可实现高带宽、低延迟的数据传输,适用于高性能系统。

- 可扩展性:AHB总线允许多个主设备和多个从设备同时连接,通过地址映射和优先级控制实现对不同设备的访问管理,提供了灵活的系统扩展性。

- 多设备支持:通过优化的仲裁方案和属性控制线,AHB总线可以同时支持多个主设备和多个从设备,实现对系统资源的共享和并行访问。

- 可靠性和容错性:AHB总线支持错误检测和纠正机制,可以通过错误检查位和冗余数据传输进行数据完整性的验证和故障容错。

缺点:

- 复杂性:AHB总线的设计较为复杂,包括仲裁、地址映射、优先级控制等方面,需要相应的硬件和软件支持,并且需要清晰的总线协议来确保正确的通信。

- 功耗:AHB总线的高性能和复杂性可能会导致相对较高的功耗,特别是在高频率和大数据传输的情况下。

4162

4162

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?