目录

二、estimating power consumption

3、 running RTL power estimation

三、Generating a Value Change Dump (VCD) File

1、Generating a VCD file with Tcl commands

2、Generating a VCD file with VCD system tasks

1.2 Special Library Cells for Power Management

前言

上一篇文章介绍了Cadence公司的INCISIVE工具使用全流程,具体见:Cadence公司的数字IC设计工具:仿真工具(INCISIVE)_qq_42922513的博客-优快云博客 https://blog.youkuaiyun.com/qq_42922513/article/details/130803606?csdn_share_tail=%7B%22type%22%3A%22blog%22%2C%22rType%22%3A%22article%22%2C%22rId%22%3A%22130803606%22%2C%22source%22%3A%22qq_42922513%22%7D

https://blog.youkuaiyun.com/qq_42922513/article/details/130803606?csdn_share_tail=%7B%22type%22%3A%22blog%22%2C%22rType%22%3A%22article%22%2C%22rId%22%3A%22130803606%22%2C%22source%22%3A%22qq_42922513%22%7D

本篇文章介绍INCISIVE在低功耗设计方面的使用方法

一、dumptcf命令

1 介绍

dumptcf命令允许在simulation期间生成Toggle Count Format (TCF)文件。TCF是描述设计中switching activity information的Cadence标准。该文件中包含的switching activity information对于精确的功率分析或设计的功率优化是必需的。

switching activity包括:

(1)The toggle count

(2)The probability of the pin or net to be in the logic 1 state (total time in logic state 1 / total time of TCF dump)

This information is collected for pins (interface elements (输入输出) in Verilog) and for nets (wires (定义的wire变量)in Verilog).

INCISIVE工具的dumptcf命令生成的TCF文件格式与RTL Compiler(Genus)工具的write_tcf命令生成的TCF文件格式相同。

2 command options

dumptcf -output -internal -dumpwireasnet -overwrite-end:结束所有TCF探测活动。缺省情况下,在simulation结束时写入TCF文件。在simulation过程中的任何时候使用dumptcf -end命令关闭TCF数据库并写入TCF文件。在dumptcf -end命令之后的任何simulation活动都不会反映在输出文件中。

-dumpwireasnet:

Dump only ports in the pins section of the TCF file.

By default, the simulator reports the toggle count for nets/wires in the pins category of the TCF file. This format could cause annotation issues in downstream power analysis tools.

Use the -dumpwireasnet option to dump only ports in the pins section. All wires will be dumped in the nets section of the file.

tcf文件中共有两个section,分别为“pin”和“net”。输入输出变量被收集到“pin” section中。-dumpwireasnet选项使得verilog文件中定义的wire变量收集到“net” section中。

-flatformat:

By default, the dumptcf command dumps a TCF file in hierarchical format. Use the -flatformat option if you want a flat representation.

-internal:

By default, ports and Verilog internal wires are probed. Use the -internal option to include internal Verilog regs in the probe.

-internal选项使得verilog文件中定义的reg变量被收集到“net” section中。

-output filename:指定输出TCF文件的路径

-overwrite:启用覆盖现有的TCF文件

-inctoggle:为X和Z转换转储TCF数据。默认情况下,切换计数中只包含从0到1和1到0的转换。

-scope scope_identifier: specify the scope of the hierarchy for which the TCF needs to be dumped. The scope_identifier argument is a Verilog hierarchical path that determines the domain of the probing activity. All instances and cells below this hierarchy are probed for the TCF information.

-memories: Generate switching and toggle information for unpacked registers and unpacked nets.

3 使用方式

3.1 启动ncsim的交互模式

ncsim -tcl3.2 使用dumptcf命令

dumptcf -output -internal -dumpwireasnet -overwrite -memories -scope 3.3 使用run命令

run xxns3.4 结束dump

dumptcf -end二、estimating power consumption

功耗要求是设计团队的关键规范。在RTL,估计功耗可以在设计周期的早期为团队提供数据,并指导在何处可以降低功耗。例如,可能会在设计中发现不必要的功率峰值,以便进行优化。

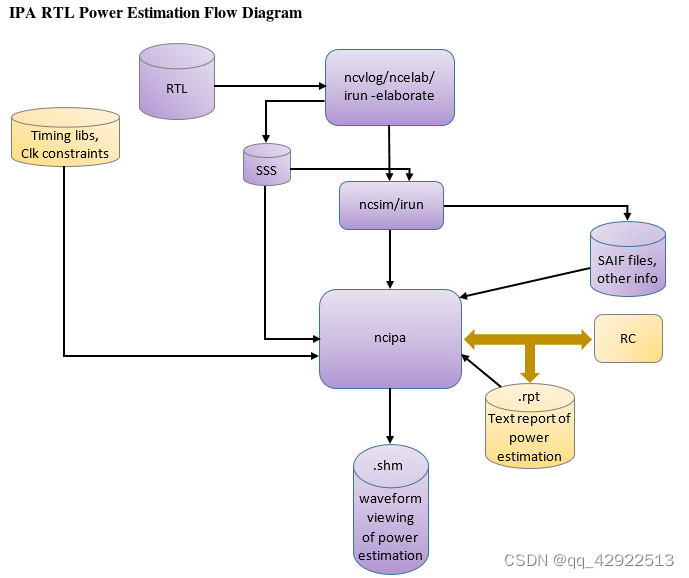

与传统的临时方法相比,The Incisive Power Analyzer (IPA) RTL功率估计功能增加了准确分析功率的能力。该特性基于从simulator创建的交换活动交换格式(Switching Activity Interchange Format, SAIF)文件中获取的逻辑生成power报告。

RTL Compiler (RC) 通过将模拟器逻辑与timing和power information以及clock constraints相结合,使用这些SAIF文件来生成准确的功率数。然后,IPA将生成的报告转换为可以在SimVision中用于波形分析的database。报告的功率数是设计中每个实例在指定模拟时间窗口内消耗的平均功率。

1、Generating SAIF files

电路消耗的动态功率取决于电路工作时设计中发生的逻辑转换。要捕获这些逻辑转换(或切换活动),必须在运行ncipa之前在irun或ncelab命令行上指定-lps_analyze。默认情况下,此选项使IES能够自动为整个模拟生成SAIF文件。

要在模拟期间为一个或多个SAIF文件定义更细粒度的时间规范,可以使用Tcl dumpsaif命令。

2、dumpsaif命令

2.1 介绍

dumpsaif命令在模拟期间生成Switching Activity Interchange Format(SAIF)文件。SAIF是Synopsys公司开发的一种ASCII格式,旨在帮助提取基于simulation过程中switching activity的toggle rate and state probability data。然后可以将该文件中的switching activity反向注释到功率分析和优化工具中。

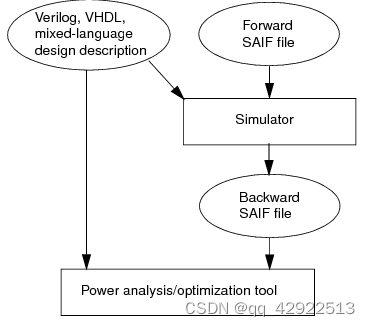

包含由simulator生成的switching activity information的SAIF文件称为backward SAIF file。可以使用dumpsaif命令(INCISIVE)为Verilog设计生成backward SAIF file。

backward SAIF file生成过程还支持使用SAIF文件,这些文件向simulator提供有关在模拟期间跟踪哪些设计元素以及监视哪些切换活动的指令。这些包含模拟器指令的文件通常由电源/优化工具生成,并称为forward SAIF files。

可以为RTL和门级的分析和优化生成forward和backward的SAIF文件。为了向simulator提供必要的指令,有两种类型的Forward SAIF文件:RTL forward SAIF file和Library forward SAIF file。

生成Library forward SAIF file可参考:

Cadence公司的数字IC设计工具:综合工具(Genus)——(1)_cadence工具_qq_42922513的博客-优快云博客

如果使用reset命令重置simulation,则会重新执行dumpsaif命令,重新启用SAIF探测,并且丢失之前的SAIF数据。

如果使用save命令创建当前模拟状态的snapshot(快照),则不会保存SAIF数据库的状态。但是,将保存所使用的dumpsaif命令。如果您然后使用restart命令加载保存的快照,那么SAIF探测将重新启用,以前的SAIF数据将丢失。

2.2 dumpsaif command options

在dumpsaif命令中,必须使用-scope选项指定需要为其转储backward SAIF的层次结构的范围,或者使用-input选项指定forward SAIF file。(下文仅介绍使用-scope下的dumpsaif命令选项)

-output: specify the path to the backward SAIF file.

-compress: 以压缩格式转储输出。该选项生成.gz格式的SAIF文件。

-overwrite

-end: 结束所有SAIF探测活动。当发出dumpsaif -end命令时,将关闭SAIF数据库。dumpsaif -end命令之后的任何模拟活动都不会反映在the backward SAIF database中。不能重新启动SAIF转储到同一数据库。

-inctoggle: Dumps the toggle count and inertial glithch count for X and Z transitions.

-internal: Enable dumping of internal wires and signals in the output SAIF file. By default, only ports are probed.

saif文件中共有两个section,分别为“PORT”和“net”。-internal选项是的verilog文件中定义的reg和wire变量存储到“net” section。

-hierarchy: enable a hierarchical dump of the backward SAIF file.

-interval time_spec: 指定在模拟期间捕获SAIF数据的特定时间段。time_spec参数可以是后跟时间单位的正整数。如果未指定时间单元,则使用默认模拟时间单元。当模拟时间与指定的时间间隔匹配时,将转储SAIF数据,并为下一个时间间隔自动创建一个新文件。

-scope cope_identifier: Specify the scope of the hierarchy for which the backward SAIF needs to be dumped.scope_identifier参数是Verilog的层次路径。指定的路径确定探测活动的域。该层次结构下的所有实例和单元都探测SAIF信息。如果不包含-scope选项的参数,则会生成警告,并将顶层设计单元用作范围。

-memories: Generate switching and toggle information for unpacked registers and unpacked nets.

2.3 使用方式

2.3.1 启动ncsim的交互模式

ncsim -tcl2.3.2 使用dumpsaif命令

dumpsaif -scope -internal -hierarchy -inctoggle -memories -output xxx.saif -overwrite2.3.3 使用run命令

run xxns2.3.4 结束dump

dumpsaif -end3、 running RTL power estimation

三、Generating a Value Change Dump (VCD) File

value change dump(VCD)文件是一个ASCII文件,其中包含有关设计中选定变量的值更改的信息。该文件包含头信息、变量定义和所有指定变量的值更改。

1、Generating a VCD file with Tcl commands

database -open dbase_name -vcd -default -timescale timescale_value -into filenameprobe -create [object | scope_name] -vcd -all -inputs -outputs -ports2、Generating a VCD file with VCD system tasks

可以在源描述中插入几个系统任务,以创建一个four-state VCD file。模拟器支持IEEE Verilog语言参考手册中指定的所有value change dump system tasks。

$dumpfile ("filename"); #VCD文件的名称。

$dumpvars; #指定要转储到VCD文件中的变量。当不带参数调用时,将转储设计中的所有变量,除了受源代码保护区域中的变量。

$dumpoff;$dumpon; #这些任务允许指定转储发生的模拟周期。$ dumpff挂起转储。将创建一个检查点,其中每个选定的变量将被转储为x值。

$dumpall #在转储文件中创建一个检查点,该检查点显示所有选定变量的当前值。$dumpfile和$dumpvars任务通常在仿真开始时指定,$dumpon, $dumpoff和$dumpall任务在仿真过程中控制转储过程。

普遍情况下,在仿真文件中添加下述代码即可:

initial begin

$dumpvars();

$dumpfile("file.vcd");

end四、CPF语言参考

1 术语

1.1 design objects

Design objects are objects named in the description of the design which can be in the form of RTL files or a netlist. Design objects can be referenced by the CPF command.

1.1.1 Design

The top-level module.

1.1.2 Followpins

Routing structures in the standard cells that allow routing of power and ground nets in a standard cell row through abutting of cells. Because the power and ground pins in the cells are aligned, the power and ground routing "follows the pins".

1.2.3 instance

模块或库单元的实例化。Hierarchical instances是模块的实例化。Leaf instances是库单元的实例化。

1.2.4 module

A logic block in the design.

1.2.5 Net

A connection between instance pins and ports.

1.2.6 pad

I/O cell的实例,也称为pad cell。cell通常有一个或多个pin,必须连接到芯片的封装引脚。这样的pins被称为pad pin或pad port。

1.2.7 pin

实例或库单元的入口点或退出点。

1.2.8 port

设计或模块的入口点或出口点。

1.2 Special Library Cells for Power Management

1.2.1 Always On Cell

位于switched-off domain中的一种特殊单元,除primary电源和接地引脚外,还具有secondary电源或接地引脚。只要给secondary电源或地引脚供电,单元的功能就不会改变。A special case of a global cell

1.2.2 Global Cell

A special cell that has secondary power or ground pins in addition to the primary power and ground pins (followpins). In some cell designs, when the primary power or ground are switched off, the cell function can be different from the normal function when the primary power and gound are on. Also, in some cases, the cell can also have isolation logic built in at the cell input pins. Examples of global cells are traditional always-on cells and other special low-power cells such as state retention cells and dual-rail isolation cells.

1.2.3 isolation cell

逻辑用于隔离两个电源域之间的信号,其中一个是接通的,另一个是关闭的。这种单元最常见的用途是将来自处于关闭状态的电源域的信号与接收这些信号并保持打开状态的电源域隔离开来。

1.2.4 level shifter cell

在不同电压下工作的功率域之间传递数据信号的逻辑。

1.2.5 power clamp cell

一种将信号箝位到特定电压的特殊二极管单元。

1.2.6 power switch cell

用于将电源与电源域中的gates连接和断开的逻辑。

1.2.7 state retention cell

专用触发器或锁存器,用于在primary电源关闭时保持单元的状态。

五、参考

值变转储文件_$dumpfile $dumpon $dumpoff_zhouyiiii11111的博客-优快云博客

modelsim打开和生成VCD文件的方法_modelsim vcd_90的天蝎的博客-优快云博客

PS:觉得有用就点个赞收藏吧

2515

2515

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?