module cy4(

input sig_a,

input clk,

input rstb,

output sig_a_anyedge

);

reg sig_a_d1;

always @(posedge clk or negedge rstb)

if(!rstb) sig_a_d1 <= 1'b0;

else sig_a_d1 <= sig_a;

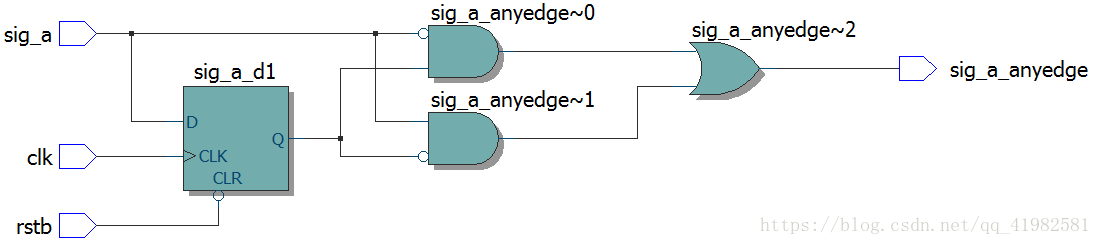

assign sig_a_anyedge

= (!sig_a & sig_a_d1) | (sig_a & !sig_a_d1);

//异或

endmodule

测试脚本代码:

`timescale 1 ns/ 1 ps

module cy4_vlg_tst();

reg eachvec;

reg clk;

reg rstb;

reg sig_a;

wire sig_a_anyedge;

cy4 i1 (

.clk(clk),

.rstb(rstb),

.sig_a(sig_a),

.sig_a_anyedge(sig_a_anyedge)

);

initial

begin

clk = 0;

rstb = 0;

sig_a =0;

100;

rstb = 1;

100;

sig_a = 1;

50;

sig_a = 0;

100;

stop;stop;display(“Running testbench”);

end

always #30 clk = !clk;

endmodule

1066

1066

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?