modelsim编译vivado仿真库报错解析

modelsim编译vivado一直报错,搞了两天,换了无数modelsim和vivado版本,血的教训,特此记录!

编译仿真库注意点:

-

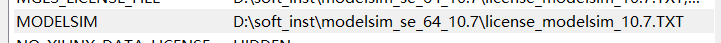

检查环境变量,一定不要不要不要千万不要有 有以下变量,否则编译库时会忽略你选择编译的modelsim版本,默认选这里设置的版本去编译。实测不设置该环境变量可以正常仿真

-

Modelsim和vivado有版本匹配问题,版本不匹配就会编译失败。

vivado2018.2与modelsim10.7匹配 ==> 我用的这个,测试OK

vivado2017.4与modelsim10.6匹配, -

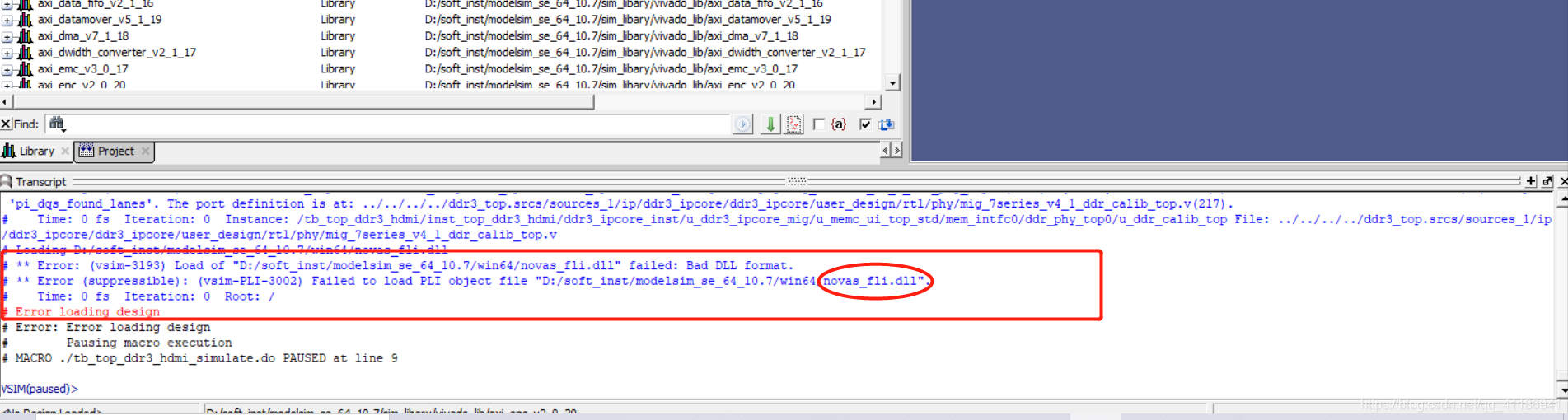

编译0 error,仿真modelsim会报以下错误

Loading D:/soft_inst/modelsim_se_64_10.7/win64/novas_fli.dllError: (vsim-3193) Load of “D:/soft_inst/modelsim_se_64_10.7/win64/novas_fli.dll” failed: Bad DLL format.Error:(suppressible):(vsim-PLI-3002)Failed to load PLI object file “D:/soft_inst/modelsim_se_64_10.7/win64/novas_fli.dll”.

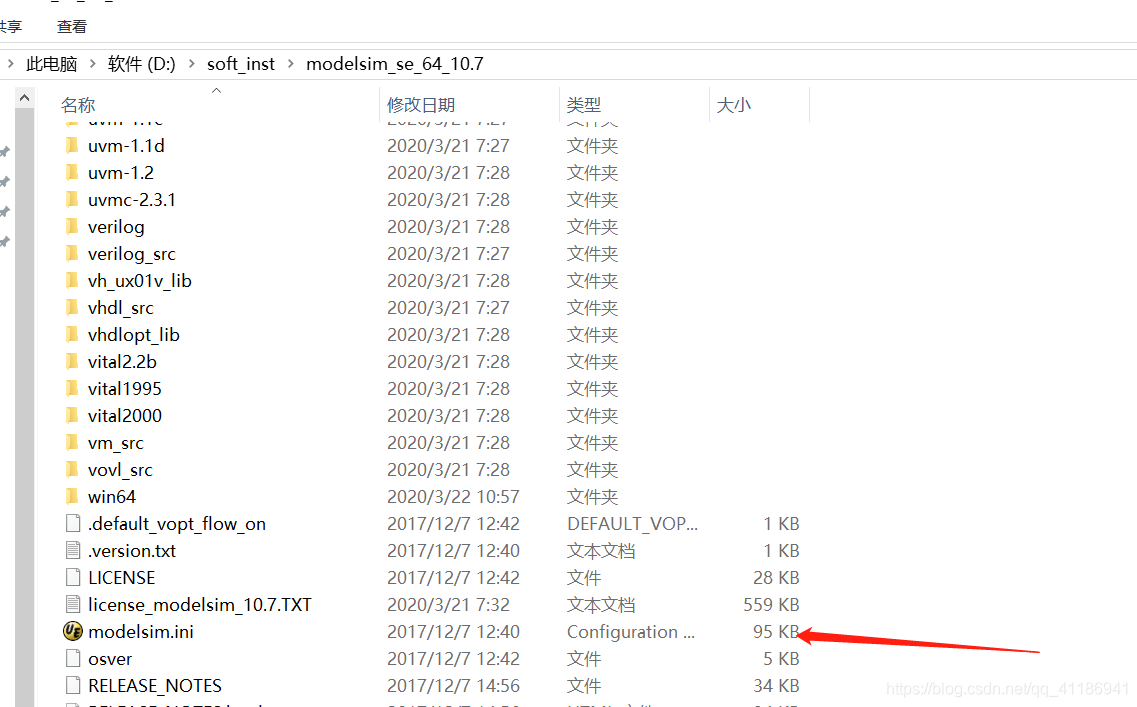

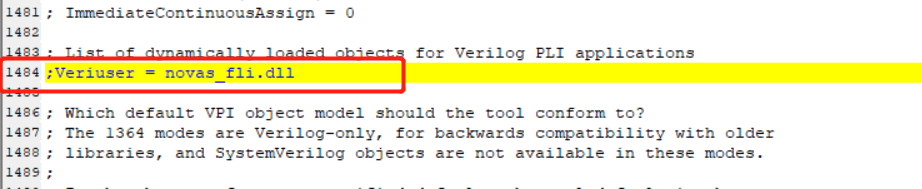

解决方案:找到编译库文件所在的文件夹中生成的modelsim.ini文件,需要将Veriuser = novas_fli.dll注释掉。(分号为注释符)

以上。

本文记录了在使用Modelsim编译Vivado仿真库时遇到的问题及其解决方案。关键点包括:检查环境变量,避免特定变量导致的版本冲突;确保Modelsim和Vivado版本匹配,如vivado2018.2与modelsim10.7的兼容性;以及当出现加载dll错误时,注释modelsim.ini中的Veriuser=novas_fli.dll条目。通过这些步骤,可以成功解决编译和仿真中的错误。

本文记录了在使用Modelsim编译Vivado仿真库时遇到的问题及其解决方案。关键点包括:检查环境变量,避免特定变量导致的版本冲突;确保Modelsim和Vivado版本匹配,如vivado2018.2与modelsim10.7的兼容性;以及当出现加载dll错误时,注释modelsim.ini中的Veriuser=novas_fli.dll条目。通过这些步骤,可以成功解决编译和仿真中的错误。

8940

8940

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?