(2020-03-16-21:00)

<涉及项目: Cyclone*HDMI>

平台: altera Cyclo+ Lattice ECP(serides)

现象1: 每次把声音调到那一路视频口时,会立马蓝屏(无信号),按红外遥控静音按键后图像又会出来。

分析:尝试把it66121的i2s的三根线屏蔽掉则不会出现这种现象。很莫名其妙。

抓reval发现serdes的PLL的lock都没起来。

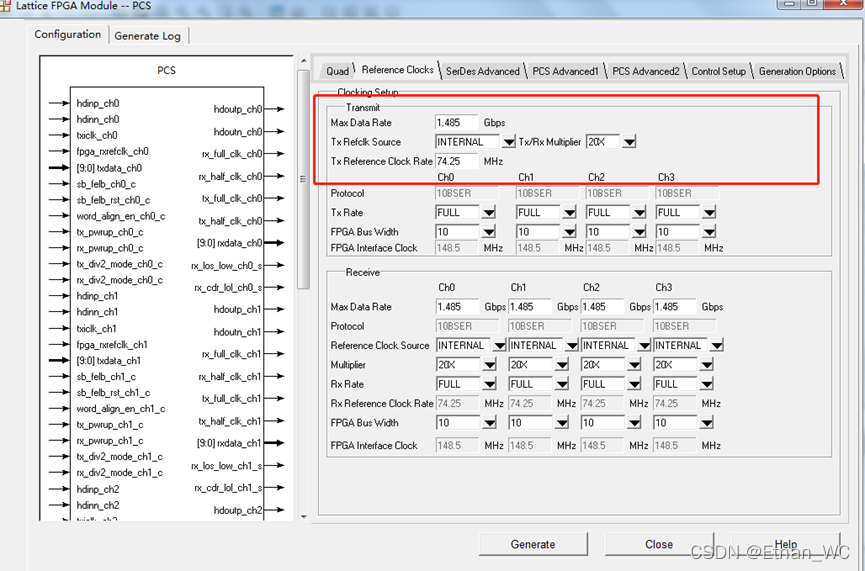

解决方案:将上板的输入时钟晶振由27M改成74.25M。将74.25M直接接入SERDES,降低PLL倍频的级数。(之前是将27M输入到FPGA的PLL生成148.5M,再给到serdes,serdes内部的PLL再倍频到1.45G)

⇒ 给SERDES的参考时钟最好直接由晶振提供。

小结:SERDES的参考时钟不能太小,太小会影响PLL倍频的级数,从而影响产品的稳定性。

=================================

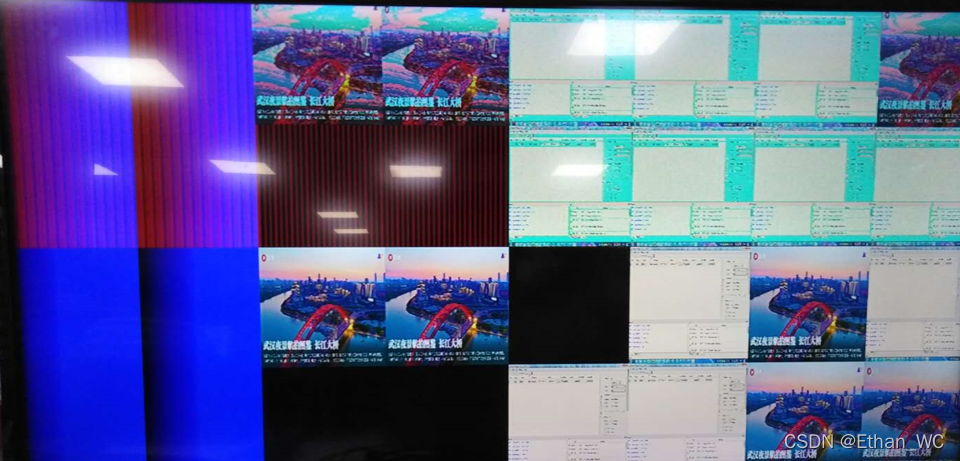

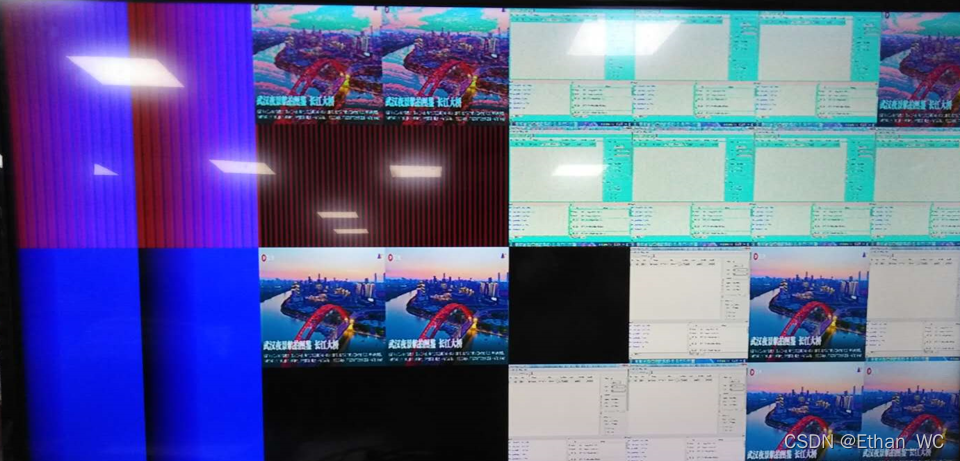

现象2:上16路偏色

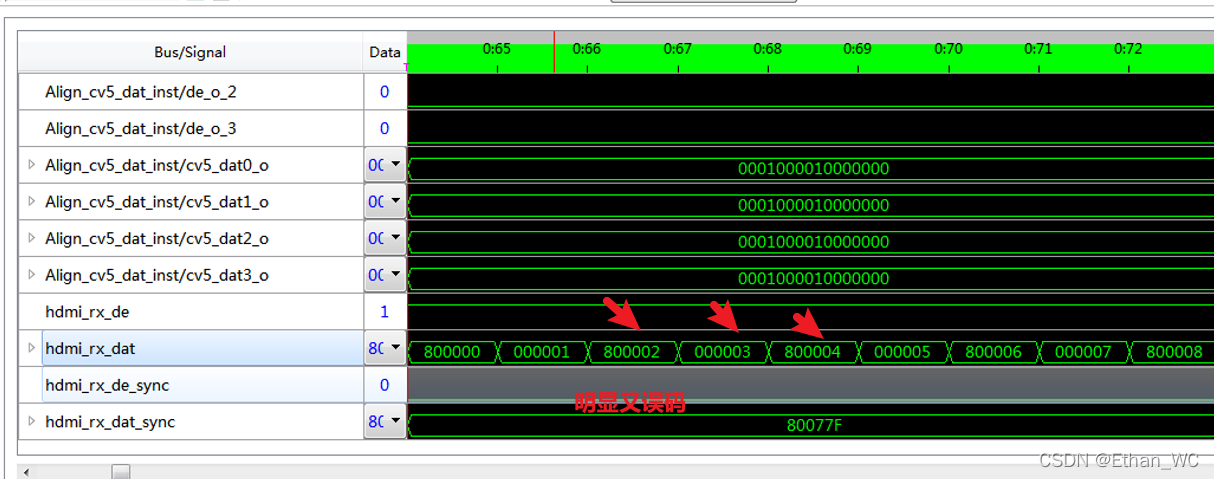

上16路颜色明显偏了,解出来的行场每次检测都能通过,但是有时候烧进去后变成1922长度。上板发送的递增数据,下板解出来就完全不对

重启无法解决!

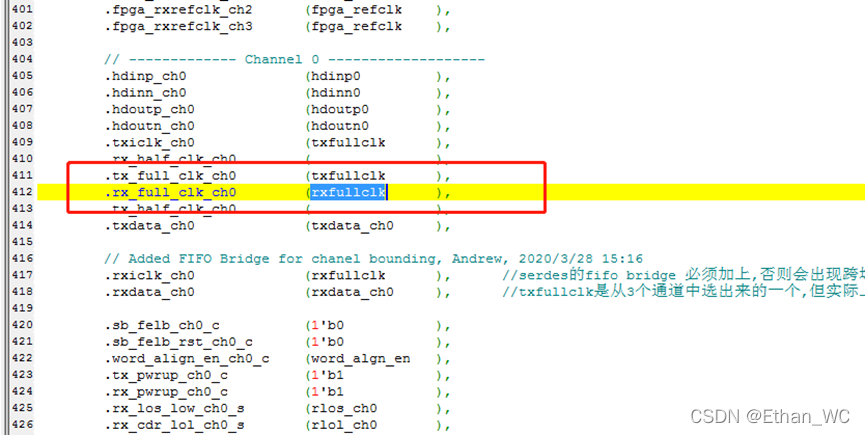

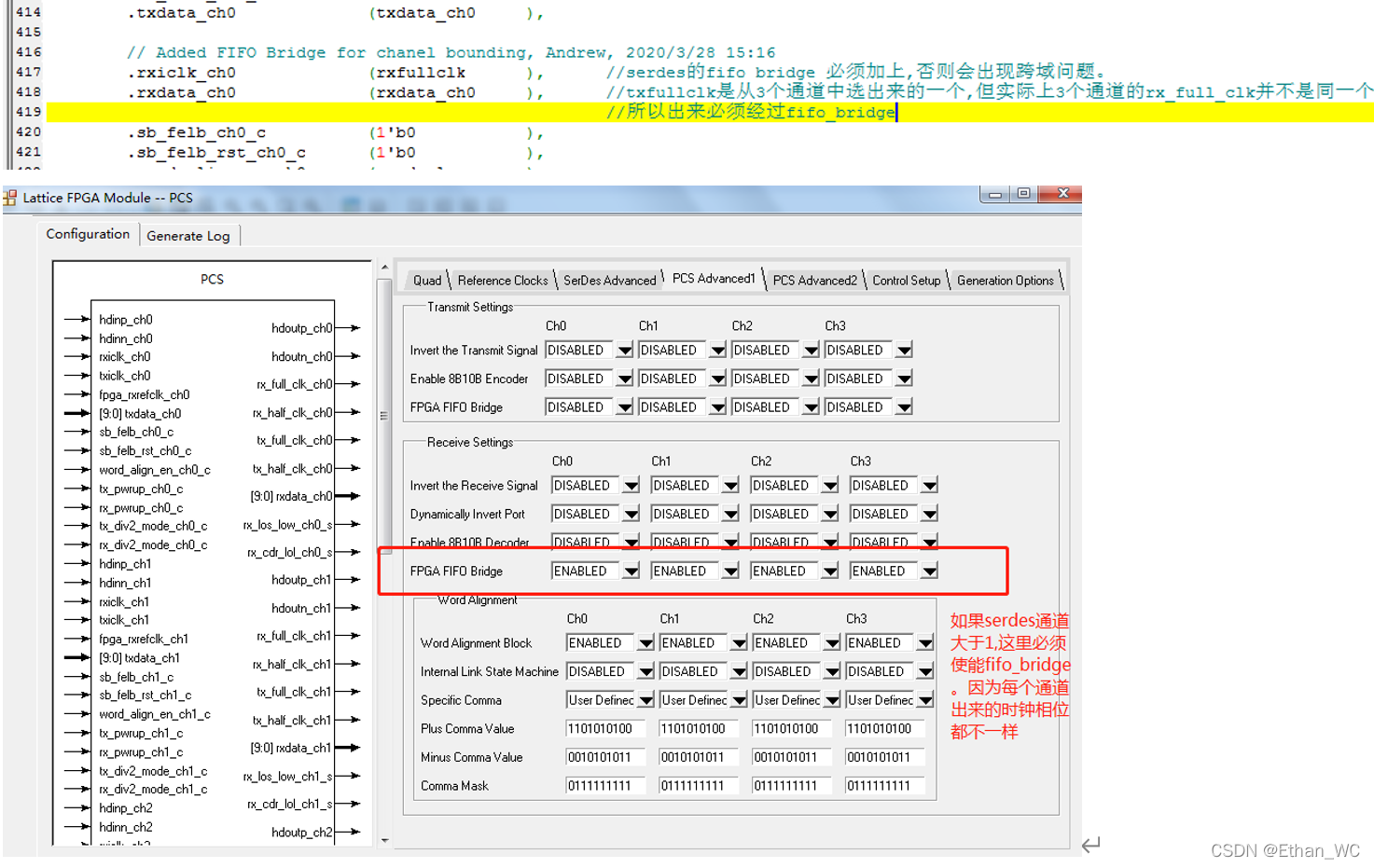

原因:Pcs.v中只例化了0通道的的rxfullclk, 但是其他通道出来的并不是这个时钟,这里就会有一个恶心的跨域问题,隐藏的很深。(巨坑:3个通道出来的时钟相位竟然不同的)

解决方案:

使能SERDES ip中的rx端的FIFO Bridge

本文讲述了在使用Altera Cyclone与Lattice ECP平台时遇到的两个问题:一是SERDES PLL锁相问题导致的视频蓝屏,解决办法是调整时钟配置;二是Pcs.v中的时钟跨域问题导致16路视频偏色,通过启用FIFOBridge解决了这一难题。强调了SERDES参考时钟稳定性和时钟管理的重要性。

本文讲述了在使用Altera Cyclone与Lattice ECP平台时遇到的两个问题:一是SERDES PLL锁相问题导致的视频蓝屏,解决办法是调整时钟配置;二是Pcs.v中的时钟跨域问题导致16路视频偏色,通过启用FIFOBridge解决了这一难题。强调了SERDES参考时钟稳定性和时钟管理的重要性。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?