目录

FPGA定义

FPGA 全称为 Field Programme Gate Array , 现场可编程逻辑门阵列。

用通俗的语言来说,FPGA更像是有很多的积木块儿,开发者根据需要实现的目标,来选择用哪些积木来搭建这个建筑。

由此可见,根据开发者自选积木(对应开发当中的IP)来组合功能,我们可以得到FPGA灵活、可编程(也就是组合不同IP)的特点。

现场这个特点呢,主要是说可以随时重复写入。

门阵列是指的FPGA内部有大量的LUT(Look up table查找表),这样就会免除很多的计算,直接把结果写在查找表里面。

数字电路

数字电路是离散化后的结果,只有0和1。模拟电路是我们现实生活中看到的连续不断,比如看到的正弦电压曲线就是模拟电压的变换过程。那么在数模转换的时候,怎么区分是转为0还是转为1呢?这时候需要一个裁决电平,如果比这个电平高,那么就为1;如果比这个电平低,就为0,可以实现模拟向数字的转化。

至于这个电平具体是多少,其实存在很多工业当中的电平标准:TTL, CMOS, LVTTL, LVCMOS, ECL, PECL, LVDS, HSTL, SSTL。

在代码中,数字设计分为组合逻辑与时序逻辑两大类。

组合逻辑

组合逻辑的输出仅仅与当前输入有关系,是不需要寄存器(reg)的,一个很简单的判断方法是看电路当中有没有时钟信号。

组合逻辑当中是有逻辑门电路组成的,常见的逻辑门包括与门(AND)、非门(NOT,INVERTER / INV)、或门(OR)、异或门(XOR)、与非门(NAND)、或非门(NOR)等等。

时序逻辑

时序逻辑的输出不仅和当前输入有关,也和上一个状态有关,也就是需要寄存器储值,如果电路图当中存在时钟信号,那么就是时序逻辑。

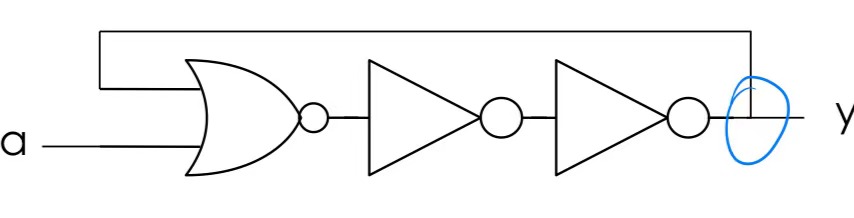

可能只是说与上一个状态有关有些抽象,那么以一个电路图来解释可能更加形象一些。

如下图1所示,此时或非门的输入是a和y,也就是说,上一个状态(前一个输出结果y)会影响到当前输出(作为其中一个输入),那么这就不是一个组合电路,但是和时序电路也有一定的差距,我们需要在上方的电线上加一个reg,来存储上一个y的状态,这样才算是一个时序电路了。

图1 电路图展示

时序逻辑电路是根据时钟信号触发的,这个过程需要用到触发器,存在两种触发类型:电平触发,边沿触发。(触发器我会在下一篇写)

电平触发就是检测电平为高电平1,或者为低电平0的时候有效,在代码中可以这样写eg.

always @ ( clk ) begin //clk为高电平有效

... //省略内部逻辑

end

always @ ( !clk ) begin //clk为低电平有效

... //省略内部逻辑

end

//是注释符号的意思

!和~都是取反符号,!是直接取反,如果clk为真,取反后为0。

~是按位取反,因为时钟信号都是1bit的,所以这里用哪个都可以。按位取反是把每一位都取反后返回。

!1001 = 0

~ 1001 = 0110

边沿触发就是检测时钟信号的上升沿或者下降沿有效,代码中可以这样写eg.

always @ ( posedge clk ) begin //clk为上升沿有效

... //省略内部逻辑

end

always @ ( negedge clk ) begin //clk为低电平有效

... //省略内部逻辑

end

posedge是上升沿的关键词

negedge是下降沿的关键词

事实上呢,组合逻辑与时序逻辑并不是互斥存在的,而是互补同时存在于数字电路当中的,例如常见的状态机转换(FSM)电路。

2247

2247

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?