fifo是一种先入先出的数据缓冲器,有一个写端口(din、wr_en)和一个读端口(rout、rd_en);写端口会输出空满标志。同步fifo相对于异步fifo而言,其好处在于读时钟和写时钟为同一个时钟,不需要对地址进行跨时钟域,可以直接就读地址和写地址进行加减。

1、同步fifo解析

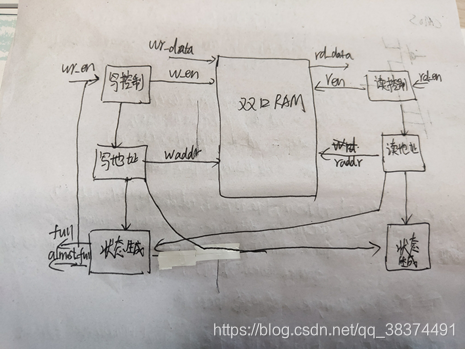

从图中可以看到同步fifo分为读端口和写端口,两边均由三部分组成:写或读控制、写或读地址和状态生成

(1)读控制(ren)、写控制(wen)的生成:当外部输入的wr_en=1且full=0时,也就是外部让你写且你的fifo现在没有写满的情况下,你就可以对fifo进行写操作。用verilog表示即为

wen=!full&&wr_en;

读控制同理:ren=(!empty)&&rd_en;

(2)读地址(raddr)、写地址(waddr)

这块比较简单,时钟上升沿到来了且读使能(ren)或者写使能(wen)有效,读地址(读指针)+1或者写地址(写指针)+1;

对应到verilog代码为:

always@(posedge clk)

if(reset)

waddr<=5’b0;

else if(wen)

waddr<=waddr+1;

always@(posedge clk)

if(reset)

raddr<=5’b0;

else if(ren)

raddr<=raddr+1;

(3) 根据地址计算wr_gap,判断full、almost_full;根据rd_gap判断empty、almost_empty;<

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?