- 1、设计思路

- 2、设计过程中遇到的一些问题

- 3、verilog代码和仿真文件

1、设计思路

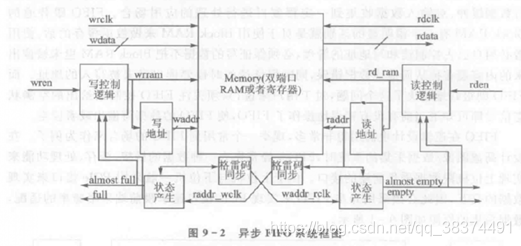

关键的点:读写控制信号的生成、读写地址、状态产生。

(1)读控制(ren)、写控制(wen)的生成:当外部输入的wr_en=1且full=0时,也就是外部让你写且你的fifo现在没有写满的情况下,你就可以对fifo进行写操作。用verilog表示即为

wen=!full&&wr_en;

读控制同理:ren=(!empty)&&rd_en;

(2)读地址(raddr)、写地址(waddr)

这块比较简单,时钟上升沿到来了且读使能(ren)或者写使能(wen)有效,读地址(读指针)+1或者写地址(写指针)+1;

对应到verilog代码为:

always@(posedge clk)

if(reset)

waddr<=5’b0;

else if(wen)

waddr<=waddr+1;

always@(posedge clk)

if(reset)

raddr<=5’b0;

else if(ren)

raddr<=raddr+1;

(3)状态判断

要对状态判断就需要计算出读写地址的差值,因为是异步的,所以需要进行跨时钟域。即计算wr_gap的时候需要将读地址同步到写时钟域来,具体怎么将读地址同步过来呢?

因为读地址是自加1的,这个特性就可以使用格雷码,即将二进制转换成格雷码,这样相邻两位就只有1bit发生变化。

二进制转换成格雷码的方法:将二进制右移移位后,和右移前的数值进行异或即可。

//读地址从二进制转变成格雷码

always @(posedge rd_clk or posedge rd_reset)

if(rd_reset)

raddr_gray<=0;

else raddr_gray<=raddr^(raddr>>1);

转换成格雷码后,就可以通过打两拍的方法进行同步。但是计算wr_gap的时候因为waddr是二进制,所以将同步过来的读地址的格雷码再转换为二进制,具体怎么将格雷码转化为二进制呢?

将格雷码的最高位作为二进制的最高位,然后将格雷码的次高位和二进制的最高位按位异或获得二进制的次高位,依次类推,具体见下图:

//将从读时钟域同步到写时钟域的格雷码读地址转变成二进制读地址

always@(*)

raddr_gray2bin={raddr_gray_syn2w1[4],

raddr_gray_syn2w1[4]^raddr_gray_syn2w1[3],

raddr_gray_syn2w1[4]^raddr_gray_syn2w1[3]^raddr_gray_syn2w1[2],

raddr_gray_syn2w1[4]^raddr_gray_syn2w1[3]^raddr_gray_syn2w1[2]^raddr_gray_syn2w1[1],

raddr_gray_syn2w1[4]^raddr_gray_syn2w1[3]^raddr_gray_syn2w1[2]^raddr_gray_syn2w1[1]^raddr_gray_syn2w1[0]};

关于间隔计算见下图:需要提醒读者的是,wr_gap是计算还有几个空格子,rd_gap计算还有几个数据。因此可以这样理解(可能不是很准确只是一种记忆方法)wr_gap是用读地址减去写地址;rd_gap是用写地址减去读地址。具体见下图:

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?