1、基础知识

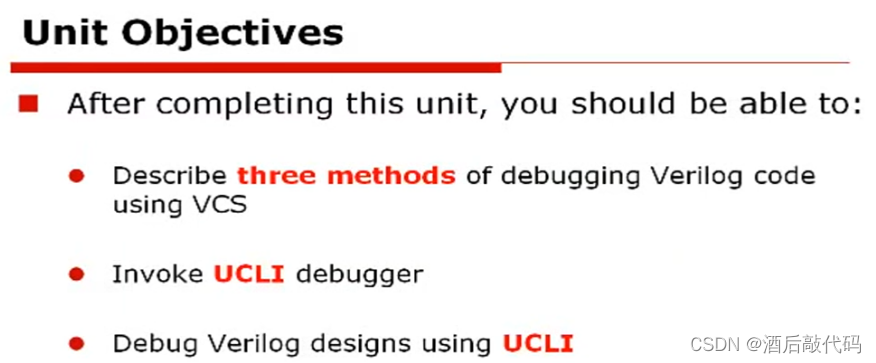

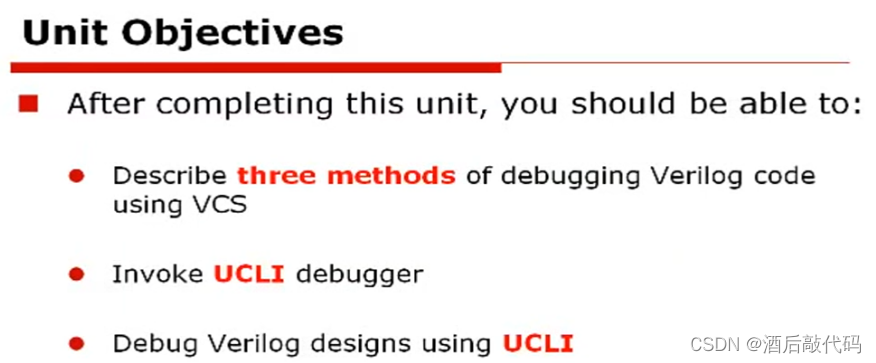

使用命令行进行debug。

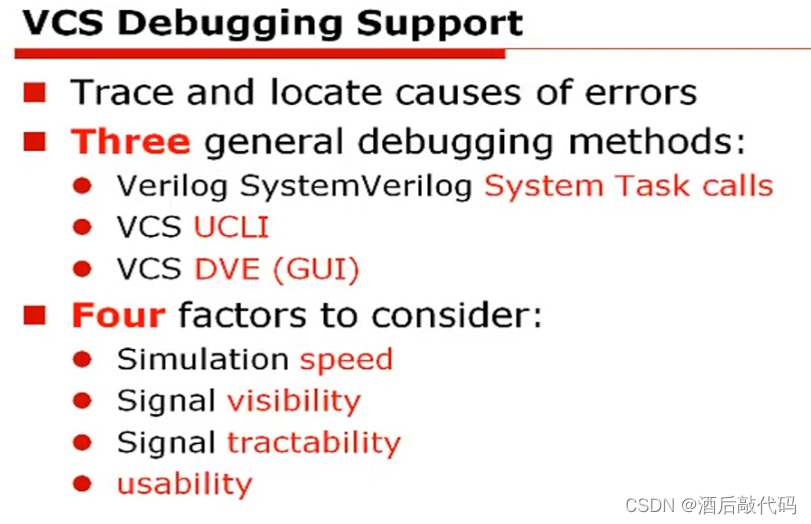

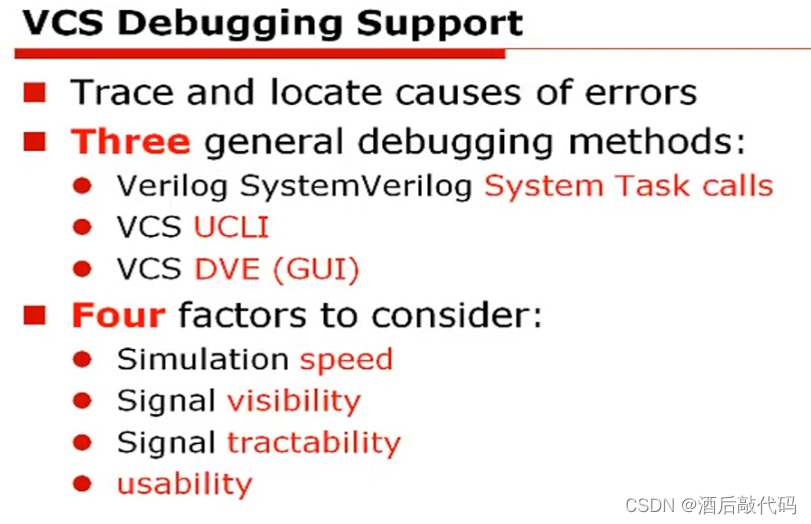

使用VCS进行debug的三种方式:专门做debug的工具目前最好的是Verdi

1、系统函数的调用

2、通过命令行的方式

3、使用DVE(GUI)

debug需要注意的因素:

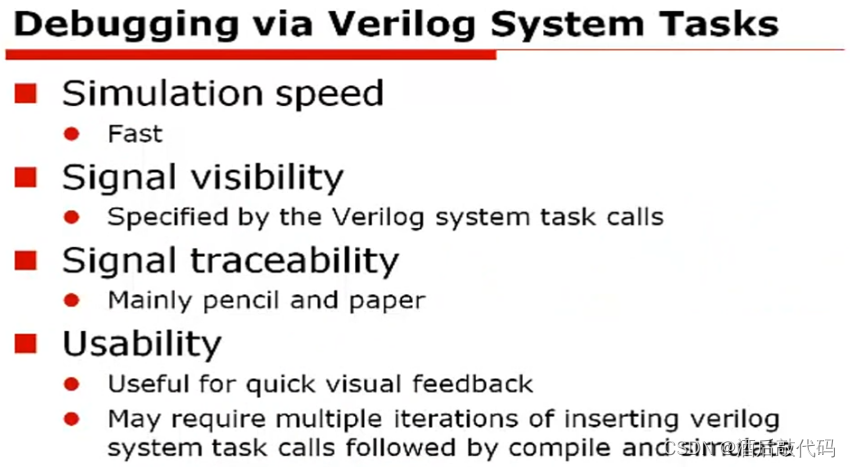

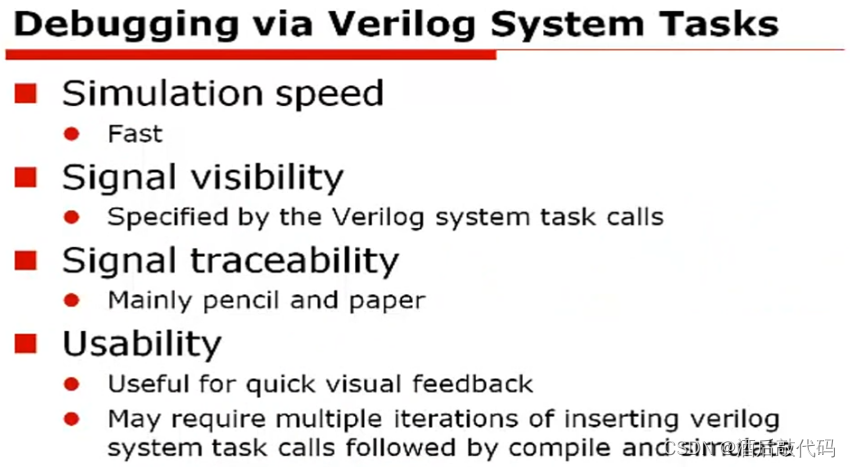

1、仿真速度(开关选项(command_time\run_time)打开越多,越消耗资源,仿真速度越慢)

2、信号可视性,便于观察分析

3、信号可追踪性,便于后期对错误的定位等等

4、可用性

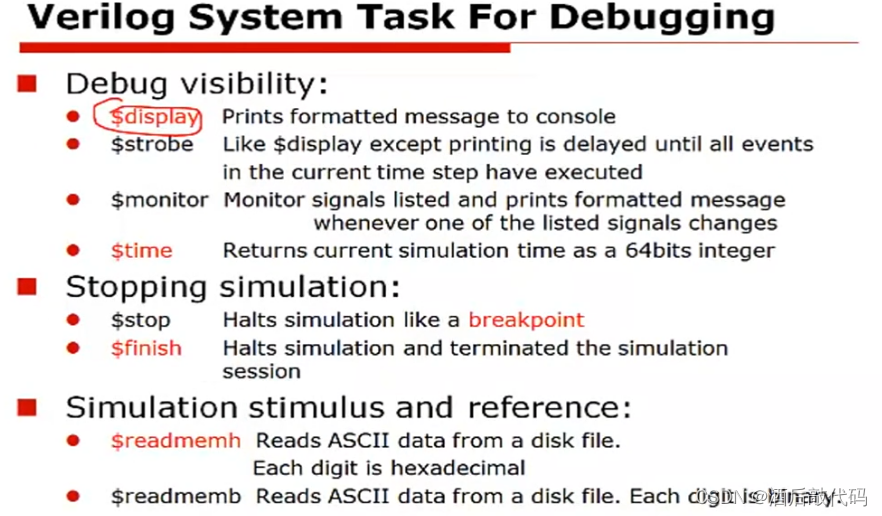

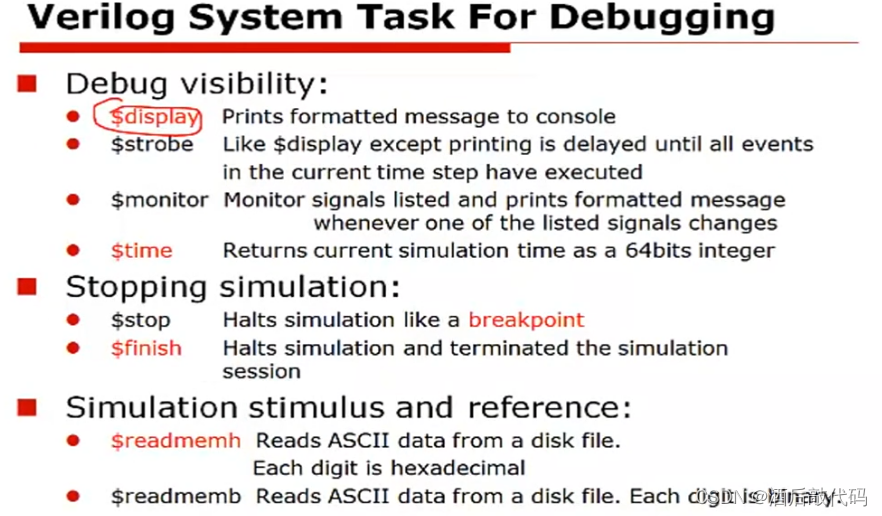

调用系统函数进行debug:

使用示例:

1、基础知识

使用命令行进行debug。

1、系统函数的调用

2、通过命令行的方式

3、使用DVE(GUI)

1、仿真速度(开关选项(command_time\run_time)打开越多,越消耗资源,仿真速度越慢)

2、信号可视性,便于观察分析

3、信号可追踪性,便于后期对错误的定位等等

4、可用性

使用示例:

6212

6212

1520

1520

8309

8309

675

675

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?